# DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

# STEREO VISION HARDWARE ARCHITECTURES FOR REAL-TIME DEPTH COMPUTATION IN EMBEDDED VISION APPLICATIONS

#### DOCTOR OF PHILOSOPHY DISSERTATION

**CHRISTOS TTOFI**

# DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

# STEREO VISION HARDWARE ARCHITECTURES FOR REAL-TIME DEPTH COMPUTATION IN EMBEDDED VISION APPLICATIONS

#### **CHRISTOS TTOFI**

A Dissertation Submitted to the University of Cyprus in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

## **VALIDATION PAGE**

**Doctoral Candidate: Christos Ttofi**

Doctoral Thesis Title: Stereo Vision Hardware Architectures for Real-Time Depth Computation in Embedded Vision Applications

The present Doctoral Dissertation was submitted in partial fulfillment of the requirements for the Degree of Doctor of Philosophy at the **Department of Electrical and Computer Engineering** and was approved on May 23, 2014 by the members of the **Examination Committee**.

| <b>Examination Committee</b> | e: _ | $\Lambda$                 |       |

|------------------------------|------|---------------------------|-------|

|                              |      | ΠΡΟΣΩΠΙΚΑ                 |       |

| Committee Chair              |      | ΔΕΔΟΜΕΝΑ                  |       |

|                              |      | Dr. Maria K Michael       |       |

|                              |      | ΠΡΟΣΩΠΙΚΑ                 | 1     |

| Research Supervisor          |      | ΔΕΔΟΜΕΝΑ                  | >     |

|                              |      | Dr. Theoeharis Theochar   | ides  |

|                              | Γ    | ΠΡΟΣΩΠΙΚΑ                 |       |

| <b>Committee Member</b>      |      | ΔΕΔΟΜΕΝΑ                  | >     |

| _                            |      | Dr. Dimitrios Soudris     |       |

|                              |      | ΠΡΟΣΩΠΙΚΑ                 |       |

| <b>Committee Member</b>      |      | ΔΕΔΟΜΕΝΑ                  | 1     |

| <del></del>                  |      | Dr. Constantinos S. Patti | chis  |

|                              | Γ    | ΠΡΟΣΩΠΙΚΑ                 |       |

| <b>Committee Member</b>      |      | ΔΕΔΟΜΕΝΑ                  |       |

|                              | _    | Dr. Chrysostomos Nicopo   | oulos |

### **DECLARATION OF DOCTORAL CANDIDATE**

The present doctoral dissertation was submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy of the University of Cyprus. It is a product of original work of my own, unless otherwise mentioned through references, notes, or any other statements.

Christos Ttofi

[Full Name of Doctoral Candidate]

ΠΡΟΣΩΠΙΚΑ

ΔΕΔΟΜΕΝΑ

ΔΕΔΟΜΕΝΑ

[Signature]

#### ПЕРІЛНЧН

Η ανάκτηση του βάθους, δηλαδή της απόστασης ενός αντικειμένου από μία διάταξη καμερών, μέσω υπολογιστικών συστημάτων στερεοσκοπικής όρασης, αναμένεται να οδηγήσει σε μια ραγδαία ανάπτυξη νέων εφαρμογών στα ενσωματωμένα συστήματα όρασης μηχανής, των οποίων η λειτουργία μέχρι τώρα βασιζόταν σε δισδιάστατη πληροφορία. Απτές εφαρμογές αυτής της νέας τάσης ήδη υπάρχουν σε πολλές περιοχές: από ηλεκτρονικά είδη ευρείας κατανάλωσης και ψυχαγωγίας, μέχρι συστήματα ρομποτικής, αυτοκινήτων, ιατρικής απεικόνισης, στρατιωτικές συσκευές κ.λ.π. Η στερεοσκοπική όραση μηχανής αποτελεί μια κατάλληλη τεχνολογία για την εκτίμηση πληροφορίας βάθους σε μια οπτική σκηνή, χρησιμοποιώντας στερεοσκοπικά ζεύγη εικόνων. Η διαδικασία αυτή επιτυγχάνεται με την αναζήτηση και εντοπισμό αντίστοιχων προβολών κοινών σημείων στο χώρο, τα οποία όμως ανιχνεύονται από τις δύο κάμερες σε διαφορετικές θέσεις. Σε γενικές γραμμές, η διαδικασία της στερεοσκοπικής αντιστοίχισης συνιστά ένα υπολογιστικά απαιτητικό στόχο και έχει επιλυθεί με διάφορα είδη αλγορίθμων, παράγοντας διαφορετικά αποτελέσματα όσο αφορά την ακρίβεια των αποτελεσμάτων και την υπολογιστική πολυπλοκότητα. Επιπρόσθετα, οι απαιτήσεις είναι ακόμα μεγαλύτερες σε εφαρμογές ενσωματωμένων συστημάτων, όπου το κόστος σε κατανάλωση υλικού, διαθέσιμης μνήμης και ενέργειας χρειάζεται να ελαχιστοποιηθούν.

Η παρούσα διατριβή διερευνά την αρχιτεκτονικές υλικού αλγορίθμων στερεοσκοπικής όρασης που έχουν τη δυνατότητα να ικανοποιήσουν τις απαιτήσεις ενσωματωμένων εφαρμογών όρασης μηχανής. Αρχικά, η διατριβή παρουσιάζει τη σχεδίαση μιας αρχιτεκτονικής στερεοσκοπικής όρασης, η οποία μέσω της ενσωμάτωσης ανίχνευσης ακμών σε εικόνες επιδιώκει να επιταχύνει τη χρονοβόρα διαδικασία αντιστοίχισης κοινών σημείων στις δύο εικόνες, με τη μείωση του συνολικού χώρου αναζήτησης, που έχει ως αποτέλεσμα τη σημαντική βελτίωση της επεξεργαστικής ταχύτητας. Η ενσωμάτωση ανιχνευτών ακμών μειώνει επίσης τους απαιτούμενους πόρους σε υλικό και μνήμη, δίνοντας έτσι τη δυνατότητα σχεδιασμού μιας παράλληλης, επεκτάσιμης και αποδοτικής ως προς τους απαιτούμενους πόρους αρχιτεκτονική που είναι σε θέση να επεξεργάζεται στερεοσκοπικές εικόνες υψηλής ανάλυσης σε πραγματικό χρόνο.

Στη συνέχεια, η διατριβή εστιάζεται στο σχεδιασμό της αρχιτεκτονικής ενός πολύπλοκου, αλλά με μεγάλη ακρίβεια, αλγορίθμου στερεοσκοπικής αντιστοίγισης που χρησιμοποιεί προσαρμοστικά βάρη υποστήριξης και κατάτμηση εικόνας, σε μια προσπάθεια να βελτιώσει την αξιοπιστία της διαδικασία αντιστοίχισης και να ικανοποιήσει τις εξαιρετικά υψηλές απαιτήσεις ακρίβειας αναδυόμενων ενσωματωμένων εφαρμογών όρασης μηχανής. Η διατριβή εισάγει βελτιστοποιήσεις που στοχεύουν στην προσαρμογή του αλγορίθμου, ώστε αυτός να μπορεί να υλοποιηθεί αποδοτικά σε υλικό. Η αρχιτεκτονική που προκύπτει επιτυγχάνει ένα αποτελεσματικό συμβιβασμό ταγύτητας/ακρίβειας σε σύγκριση με ήδη υπάργοντα συστήματα αντιστοίγισης, ωστόσο, καταναλώνοντας μεγάλο ποσοστό διαθέσιμων πόρων.

Κατά συνέπεια, η διατριβή επικεντρώνεται στη συνέχεια σε μια εναλλακτική μέθοδο η οποία στηρίζεται στην υλοποίηση της στερεοσκοπικής αντιστοίχισης με τη χρήση του πρόσφατα προτεινόμενου καθοδηγούμενου φίλτρου εικόνας. Η διατριβή παρουσιάζει μια συμπαγής και αποδοτική σχεδίαση του φίλτρου σε υλικό, και αναδεικνύει τις δυνατότητες του φίλτρου για μείωση της πολυπλοκότητας της διαδικασίας στερεοσκοπικής αντιστοίχισης που είναι βασισμένη σε προσαρμοστικά βάρη υποστήριξης, αλλά και την αποτελεσματικότητά του για υλοποίηση μιας ισχυρής μονάδας βελτίωσης των εξαγόμενων πινάκων βάθους, η οποία μπορεί να βελτιώσει την ακρίβεια του αλγορίθμου στερεοσκοπικής αντιστοίχισης σημαντικά, ακόμη και αν είναι ενσωματωμένη σε απλούς αλγορίθμους αντιστοίχισης.

Τέλος, η διατριβή παρέχει ενδιαφέρουσες πληροφορίες που προκύπτουν από την αξιολόγηση των προτεινόμενων αρχιτεκτονικών στερεοσκοπικής όρασης, σε εφαρμογές ανίχνευσης αντικειμένων σε εικόνες, καθώς και αποφυγής εμποδίων σε αυτόνομα ρομποτικά συστήματα.

**Λέξεις Κλειδιά:** Ενσωματωμένα Συστήματα, Υπολογιστική Όραση, Ενσωματωμένη Όραση Μηχανής, Στερεοσκοπική Όραση, Πίνακες Αναδιατασσόμενης Λογικής

#### **ABSTRACT**

Empowering embedded vision systems with 3D perception capabilities is expected to lead to a boost of new applications that so far could not be done with classical 2D alternatives. Applications of this new trend already exist in numerous areas: from consumer electronics and entertainment, to robotics, automotives, medical imaging, defense, etc. Stereo vision is a well-suited technology that uses two standard image cameras to infer depth information, by solving the so-called stereo matching problem. This involves searching and locating corresponding projections of the same 3D points sensed by the two cameras in different positions, a challenging task that can be tackled with many algorithms, consequently producing different outcomes in terms of accuracy and computational complexity. Stereo matching becomes even more challenging when targeting applications in embedded and mobile environments, where cost, energy and memory overheads need to be minimized.

This thesis investigates hardware architectures of stereo matching algorithms that have the potential to satisfy the requirements of constrained embedded vision applications. Initially, the design of a stereo matching architecture that utilizes edge information as a means to accelerate the overall matching process, is presented. By constraining the matching process only on binary data (edges), the search space is greatly reduced and the overall frame-rate is improved. The integration of edge information also reduces the logic and memory requirements, thus enabling the design of a parallel, scalable and resource-optimized architecture that is able to process HD stereo images in real time. Afterwards, the thesis focuses on designing the architecture of a complex, accurate matching algorithm that uses adaptive support weights (ADSW) and image segmentation, in an attempt to improve the robustness of the matching process and satisfy the extremely high matching accuracy required by many of today's embedded vision applications. The thesis introduces hardware design optimizations to adapt the segment-based ADSW algorithm for a hardware-friendly and compatible with embedded constraints design. The resulting architecture obtains an effective speed-accuracy tradeoff when compared to state-of-the-art stereo matching systems, however at the expense of high resource usage. Consequently, an alternative method that implements stereo matching based on the recently proposed guided filter, is investigated. The thesis presents a compact and efficient design of the filter, and illustrates its potential in reducing the complexity of the ADSW matching process, but also its efficiency in enabling a powerful disparity refinement unit, which can improve the matching accuracy considerably, even if it is integrated into simple stereo matching algorithms. Finally, the thesis provides insights obtained from evaluating the proposed architectures in object detection and obstacle avoidance applications.

**Keywords:** Embedded Systems; Computer Vision; Embedded Vision; Stereo Vision; Real-Time; Field Programmable Gate Arrays (FPGAs)

#### **PUBLICATIONS**

#### **Publications Stemming from this Thesis**

#### Journal Publications:

- 1. **Christos Ttofis**, Christos Kyrkou and Theocharis Theocharides, "A Hardware-Efficient Architecture for Accurate Real-Time Disparity Map Estimation," *ACM Transactions on Embedded Computing Systems*, accepted for publication, 2014.

- Christos Kyrkou, Christos Ttofis, and Theocharis Theocharides, "A Hardware Architecture for Real-Time Object Detection Using Depth and Edge Information," ACM Transactions on Embedded Computing Systems, vol. 13, no. 3, pp. 54:1-54:19, December 2013.

- 3. **Christos Ttofis**, Stavros Hadjitheofanous, Athos Georghiades and Theocharis Theocharides, "Edge-Directed Hardware Architecture for Real-Time Disparity Map Computation," *IEEE Transactions on Computers*, vol. 62, no. 4, pp. 690-704, April 2013.

- 4. **Christos Ttofis** and Theocharis Theocharides, "Hardware Design Considerations for Edge-Accelerated Stereo Correspondence Algorithms," *VLSI Design Special Issue on Circuits and Systems for Advanced Video Compression Standards*, vol. 2012, Article ID 602737, 17 pages, 2012.

#### Publications in Refereed Conference Proceedings:

- 5. **C. Ttofis** and T. Theocharides, "High-Quality Real-Time Hardware Stereo Matching based on Guided Image Filtering," *Design, Automation & Test in Europe Conference & Exhibition (DATE'14)*, Dresden, Germany, 24-28 March 2014.

- 6. **C. Ttofis**, D. Stavrou, D. Koukounis, T. Theocharides and C. Panayiotou, "A Laboratory Course on 3D Vision for Robotic Applications," *Proceedings of the IEEE International Conference on Microelectronic Systems Education 2013 (MSE '13)*, pp. 21-24, 2-3 June 2013, Austin, Texas, USA.

- 7. **C. Ttofis** and T. Theocharides, "Towards Accurate Hardware Stereo Correspondence: A Real-Time FPGA Implementation of a Segmentation-Based Adaptive Support Weight Algorithm," *Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE'12)*, Dresden, Germany, 12-16 March 2012.

- 8. C. Kyrkou, C. Ttofis, T. Theocharides, "FPGA-Accelerated Object Detection using edge information", *Proceedings of Field Programmable Logic and Application Conference (FPL) 2011*.

- 9. C. Kyrkou, C. Ttofis, T. Theocharides, "Depth-directed hardware object detection," *Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE) 2011*, pp.1-6, Grenoble, France, 14-18 March 2011.

10. S. Hadjitheophanous, **C. Ttofis**, A. S. Georghiades, and T. Theocharides, "Towards Hardware Stereoscopic 3D Reconstruction: A Real-Time FPGA Computation of the Disparity Map," *Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE) 2010*, pp.1743-1748, Dresden, Germany, 8-12 March 2010.

#### Other Publications:

11. **Christos Ttofis**, "Disparity Estimation Hardware Architectures and Design Techniques for Embedded Stereo Vision Applications," *presented as part of PhD dissertation in PhD Forum at the IEEE Design Automation and Test in Europe (DATE'13) Conference*, Grenoble, France, March 2013.

#### **Under Submission:**

- 12. Martinianos Papadopoulos, **Christos Ttofis**, Christos Kyrkou, Theocharis Theocharides, "Real-Time Obstacle Avoidance for Mobile Robots via Stereoscopic Vision Using Reconfigurable Hardware," *24th International Conference on Field Programmable Logic and Applications*, 2014

- 13. **Christos Ttofis** and Theocharis Theocharides, "A low-cost embedded accurate stereo vision system based on guided image filtering", *Computer Vision and Image Understanding*, Elsevier, 2014.

#### Other Publications by the Author

#### Journal Publications:

- 14. Dimitris Koukounis, **Christos Ttofis**, Agathoklis Papadopoullos, Theocharis Theocharides, "A High Performance Hardware Architecture for Portable, Low-Power Retinal Vessel Segmentation," *Integration, The VLSI Journal, Elsevier*, to appear, 2014.

- 15. **Christos Ttofis**, Theocharis Theocharides, and Maria K. Michael, "FPGA-based Laboratory Assignments for NoC-based Manycore Systems," *IEEE Transactions on Education*, vol. 55, no. 2, pp. 180-189, May 2012.

- 16. **Christos Ttofis**, Agathoklis Papadopoulos, Theocharis Theocharides, Maria K. Michael, and Demosthenes Doumenis, "An MPSoC-Based QAM Modulation Architecture with Run-Time Load-Balancing," *EURASIP Journal on Embedded Systems*, vol. 2011, Article ID 790265, 15 pages, 2011.

#### Publications in Refereed Conference Proceedings:

17. D. Koukounis, **C. Ttofis**, T. Theocharides, "Hardware Acceleration of Retinal Blood Vasculature Segmentation", *Proceedings of the 23rd ACM international conference on Great lakes symposium on VLSI (GLSVLSI'13)*, pp. 113-118, Paris, France, 2-3 May 2013.

- 18. **C. Ttofis**, A. Papadopoulos, T. Theocharides, M. Michael, D. Doumenis, "A reconfigurable MPSoC-based QAM modulation architecture," *Proceedings of 18th IEEE/IFIP VLSI System on Chip Conference (VLSI-SoC 2010)*, pp.137-142, 27-29 Sept. 2010.

- 19. **C Ttofis**, C. Kyrkou, T. Theocharides and M. K. Michael, "FPGA-Based NoC-Driven Sequence of Lab Assignments for Manycore Systems," *Proceedings of the IEEE International Conference on Microelectronic Systems Education 2009 (MSE '09)*, pp.5-8, San Francisco, USA, 25-27 July 2009 **Best Paper Award**

- 20. **C. Ttofis**, **T. Theocharides**, "A C++ Simulator for Evaluting NoC Communication Backbones," in the Proceedings of the 3rd Greek National Student Conference of Electrical and Computer Engineering, page 54, Thessaloniki, Greece, April 2009.

#### **ACKNOWLEDGEMENTS**

During the three years of this thesis research work, I received much support from many people around me. Therefore, I would like to take this opportunity to express my gratitude and appreciation to these people. This thesis would not have been possible without their invaluable help and support.

First of all, I would like to thank my very passionate advisor, Dr. Theocharis Theocharides, for his guidance and support over these years. He have believed in me from the beginning, guided me steadily through this period, and managed to keep me calm in demanding and stressful situations. Furthermore, I will always be thankful for his knowledge, insistence, and the fact that he has provided a productive and friendly environment for research, factors that all strengthened this work significantly. It has been an honor to work with him.

I would also like to express my sincere thanks to my colleagues from the EASOC laboratory for the pleasant collaborations, as well as the enjoyable group meetings and discussions we had. A special thanks to my colleague Christos Kyrkou for his committed collaboration in the development of the "depth-accelerated hardware object detection system". Our collaboration has resulted in several publications, which are included in this thesis. I also thank my colleagues at the KIOS Research Center for establishing a nice and enjoyable working atmosphere.

During the three-year period of my PhD research, I was lucky to have the chance to work in the RUNNER project, together with a group of brilliant experts, who contributed in making meetings, visits and workshops a fun and rewarding experience. I am also indebted to the members of my examination committee professor Constantinos Pattichis, Dr. Maria Michael, Dr. Dimitrios Soudris, Dr. Theocharis Theocharides and Dr. Chrysostomos Nicopoulos, who dedicated time to review this dissertation, and provided feedback and suggestions.

On a personal note, I am so thankful to my wonderful family for the continuous support, patience and encouragement during the progress of my thesis. I am grateful for my wife, Ioanna, who always make me keep trying to reach my dreams, and for my son, Savvas, because he has brought me so much joy, but in addition to the smiles and laughter he brings, he has taught me more than I believe could have been possible. I now understand why they both came in my life so early. I am also thankful for my pets, which make life so much pleasanter. Lastly, I am thankful for God, who not only gave me all the above, but who is always in my corner, seeing me through each day!!

Thank You All

Christos Ttofi May 23, 2014

# **DEDICATION PAGE**

# To My Family

My Wife Ioanna Filippou, and

My son Savvas Ttofi

# TABLE OF CONTENTS

| 1    | I    | ntro  | duction to Embedded Vision and Depth Perception - Thesis Motivat   | ion & |

|------|------|-------|--------------------------------------------------------------------|-------|

| Cont | ribu | tions | 5                                                                  | 1     |

|      | 1.1  | The   | e Embedded Vision Revolution                                       | 1     |

|      | 1.2  | Em    | bedded Stereo Vision - Motivation                                  | 3     |

|      | 1.3  | Ob    | jectives and Scope of Research - Thesis Contributions              | 4     |

|      | 1.4  | Ov    | erview of Chapters                                                 | 7     |

|      | 1.5  | The   | e Main Contributions of the Author                                 | 11    |

|      |      |       |                                                                    |       |

| 2    | \$   | Stere | o Vision for Depth Perception: Fundamentals and Relevant Work      | 12    |

|      | 2.1  | ΑI    | Brief Introduction to Computer Vision and Depth Estimation         | 12    |

|      | 2.   | 1.1   | Image Representation                                               | 13    |

|      | 2.   | 1.2   | Color, Grayscale and Binary Images                                 |       |

|      | 2.   | 1.3   | Representation of 3D images over a plane                           | 15    |

|      | 2.   | 1.4   | Standard Testbeds                                                  | 17    |

|      | 2.2  | De    | pth Estimation Technologies                                        |       |

|      | 2.   | 2.1   | Time-of-flight                                                     |       |

|      | 2.   | 2.2   | Structured-light                                                   |       |

|      | 2.   | 2.3   | Stereo vision                                                      |       |

|      | 2.   | 2.4   | Conclusion                                                         |       |

|      | 2.3  |       | e Human Visual Perception of Depth                                 |       |

|      | 2.4  | De    | pth Estimation using Stereo Vision                                 | 25    |

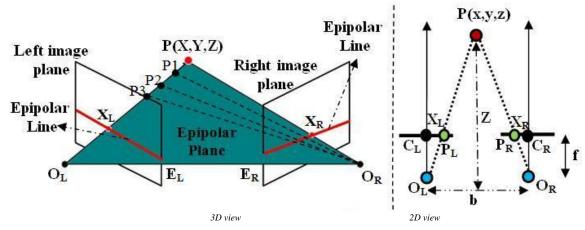

|      | 2.   | 4.1   | Pinhole Camera Model, Perspective Projection and Epipolar Geometry |       |

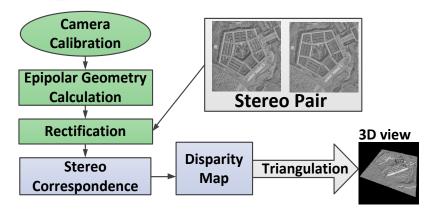

|      |      | 4.2   | Major Steps in a Stereo Vision System                              |       |

|      | 2.5  | Ov    | erview and Classification of Stereo Matching Algorithms            |       |

|      | 2.   | 5.1   | Stereo Matching Four-Step Pipeline                                 |       |

|      |      | 5.2   | Classification of stereo matching algorithms                       |       |

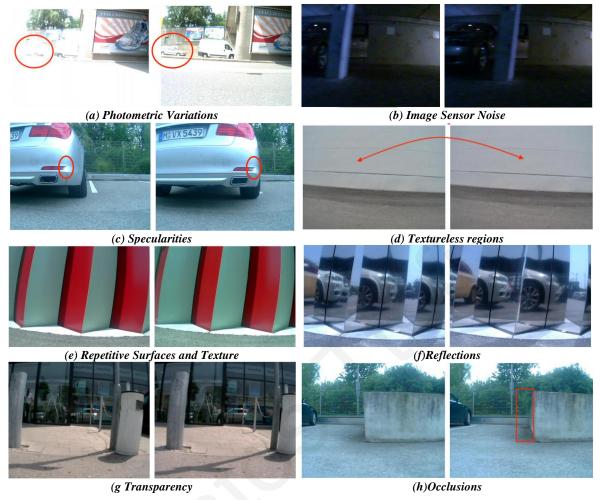

|      | 2.6  | Ch    | allenges of Stereo Vision Systems                                  | 45    |

|      | 2.7  | Ap    | plications of Stereo Vision                                        | 48    |

|      | 2.8  | Par   | rallel Architectures – Implementation Platforms                    | 49    |

|      | 2.   | 8.1   | Multi-core Central Processing Units (CPUs)                         | 51    |

|      | 2.   | 8.2   | Graphics Processing Units (GPUs)                                   | 52    |

|      | 2.   | 8.3   | Cell Broadband Engine                                              |       |

|      |      | 8.4   | Digital Signal Processors (DSPs)                                   |       |

|      |      | 8.5   | Field Programmable Gate Arrays (FPGAs)                             |       |

|      |      | 8.6   | Application Specific Integrated Circuits (ASICs)                   |       |

|      | 2.9  | Re    | view of Existing Stereo Vision Implementations                     | 56    |

| 2.9.1           | Implementations based on General Purpose CPUs                                                                                                         | 56  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.9.2           | Implementations based on General Purpose Graphics Hardware                                                                                            | 57  |

| 2.9.3           | Implementations based on Digital Signal Processors                                                                                                    | 57  |

| 2.9.4           | Implementations based on the Cell Platform                                                                                                            | 58  |

| 2.9.5           | Implementations based on Application-Specific Hardware Acceleration                                                                                   | 58  |

| 2.10 Co         | oncluding Remarks                                                                                                                                     | 61  |

| _               | e-Directed Hardware Stereo Matching: Empowering Resource-Constr                                                                                       |     |

|                 | ystems with Hard Real-Time Depth Computation                                                                                                          |     |

|                 | troduction - Motivation                                                                                                                               |     |

|                 | lge-Directed Disparity Estimation System Overview                                                                                                     |     |

| 3.3 Ec          | lge Detection Unit (EDU)                                                                                                                              | 65  |

| 3.3.1           | Sobel Edge Detector Overview                                                                                                                          | 66  |

| 3.3.2           | Sobel Edge Detection Unit (EDU) Architecture                                                                                                          | 66  |

| 3.4 Di          | isparity Computation Unit (DCU)                                                                                                                       | 67  |

| 3.4.1           | DCU process overview                                                                                                                                  | 68  |

| 3.4.2           | DCU Architecture Overview                                                                                                                             | 69  |

| 3.5 Ex          | xperimental Platform and Results                                                                                                                      | 72  |

| 3.5.1           | Experimental Platform                                                                                                                                 | 72  |

| 3.5.2           | Disparity Map Quality-Impact of Edge Detector                                                                                                         | 74  |

| 3.5.3           | Disparity Map Quality Analysis                                                                                                                        | 79  |

| 3.5.4           | System Performance                                                                                                                                    | 81  |

| 3.5.5           | Hardware Overheads                                                                                                                                    | 84  |

| 3.6 Co          | oncluding Remarks                                                                                                                                     | 87  |

| Support Wei     | Segmentation-Based Stereo Matching Hardware Design with Adaghts: Balancing Speed and Accuracy in Embedded Vision Applications troduction - Motivation | 88  |

|                 | egment-based adaptive support weight algorithm                                                                                                        |     |

| 4.2.1           | Matching Cost Initialization                                                                                                                          |     |

| 4.2.2           | Cost Aggregation                                                                                                                                      |     |

| 4.2.3           | Disparity Computation                                                                                                                                 |     |

| 4.2.4           | Disparity Refinement                                                                                                                                  |     |

|                 | ardware Adaptation Methodology                                                                                                                        |     |

|                 | oposed disparity estimation hardware architecture                                                                                                     |     |

| 4.4 P1<br>4.4.1 | Input Management Unit (IMU)                                                                                                                           |     |

| 4.4.1           | Disparity Calculation Unit (DCU)                                                                                                                      |     |

| 4.4.2           | Disparity Refinement Unit (DRU)                                                                                                                       |     |

|                 | sperimental methodology & Results                                                                                                                     |     |

| T.J L/          | \p\c1111\c11\tu1 111\cu1\cu1\cu2\cu2\cu2\cu2\cu3\cu1\cu3\cu1\cu3\cu1\cu3\cu1\cu3\cu3\cu3\cu3\cu3\cu3\cu3\cu3\cu3\cu3                                  | 104 |

| 4.5.1         | Experimental Platform & Synthesis Results                        | 102     |

|---------------|------------------------------------------------------------------|---------|

| 4.5.2         | FPGA Implementation and Emulation                                | 102     |

| 4.5.3         | Exploring large-scale scalability through an ASIC Implementation | 105     |

| 4.5.4         | Performance Results and Discussion                               | 106     |

| 4.6 Co        | ncluding Remarks                                                 | 114     |

| 5 High        | -Quality Real-Time Hardware Stereo Matching Based on Guideo      | d Image |

| Filtering     |                                                                  | 116     |

| 5.1 Int       | roduction - Motivation                                           | 116     |

| 5.2 Th        | e Guided Image Filter and its Use in Stereo Matching             | 119     |

| 5.2.1         | The Guided Image Filter (GIF)                                    |         |

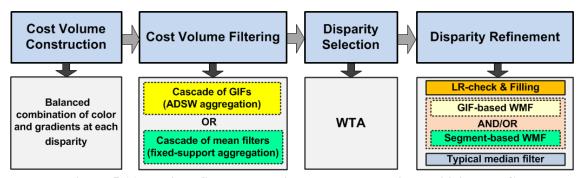

| 5.2.2         | Stereo Matching using Guided Image Filtering                     |         |

| 5.2.3         | Weighted Median Filtering using the Guided Filter Weights        |         |

| 5.3 Ha        | rdware Implementation of the Guided Image Filter                 | 127     |

| 5.4 Pro       | pposed GIF-based Stereo Matcher (GIF-SM)                         | 130     |

| 5.4.1         | Gradients Computation & Memory Management Unit (GCMMU)           | 131     |

| 5.4.2         | Cost Volume Construction Unit (CVCU)                             | 132     |

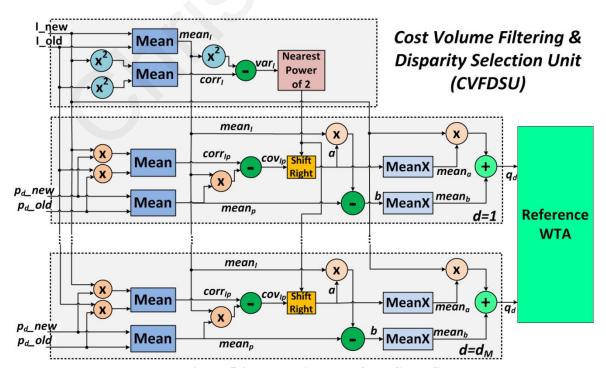

| 5.4.3         | Cost Volume Filtering & Disparity Selection Unit (CVFDSU)        |         |

| 5.4.4         | Disparity Refinement Unit (DRU)                                  |         |

| 5.5 FP        | GA Implementation Results                                        |         |

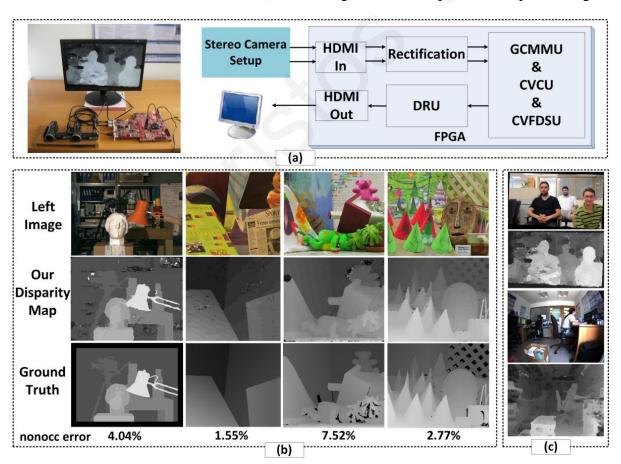

| 5.5.1         | Experimental Platform                                            |         |

| 5.5.2         | Cost-Benefit Analysis                                            |         |

| 5.5.3         | Comparisons with Related Work                                    |         |

| 5.5.4         | FPGA Synthesis Results - System scalability                      |         |

| 5.6 Co        | ncluding Remarks                                                 | 142     |

| 6 Inco        | rporating Real-Time Depth Computation in Embedded                | Vision  |

| Applications. |                                                                  | 144     |

| 6.1 De        | pth-Accelerated Hardware Object Detection                        | 144     |

| 6.1.1         | Introduction - Motivation                                        | 144     |

| 6.1.2         | Background                                                       | 146     |

| 6.1.3         | Related Work                                                     | 148     |

| 6.1.4         | Depth-Accelerated Object Detection Hardware Architecture         | 149     |

| 6.1.5         | Experimental Platform and Results                                | 153     |

| 6.1.6         | Conclusion                                                       | 157     |

| 6.2 Re        | al-Time Obstacle Avoidance for Mobile Robots                     | 157     |

| 6.2.1         | Introduction - Motivation                                        | 158     |

| 6.2.2         | Obstacle Avoidance - Overview & Existing Techniques              |         |

| 6.2.3         | Proposed Robotic Platform                                        | 162     |

|      | 6.2 | 2.4         | Experiments and Evaluation                             | 168      |

|------|-----|-------------|--------------------------------------------------------|----------|

|      | 6.2 | 2.5         | Conclusion                                             | 171      |

| 7    | C   | Conc        | lusion and Future Work                                 | 172      |

|      | 7.1 | Coı         | ncluding Remarks                                       | 172      |

|      | 7.2 | Fut         | ure Directives                                         | 174      |

|      | 7.2 | 2.1         | Short-Term Plans                                       | 174      |

|      | 7.2 | 2.2         | Long-Term Plans                                        | 176      |

|      | 7.3 | Sur         | nmary                                                  | 181      |

| 8    | R   | Refer       | rences                                                 | 182      |

| 9    | C   | Case        | Study: Edge-Accelerated Adaptive Support Weight Stereo | Matching |

| Desi | ign | • • • • • • |                                                        | 194      |

|      | 9.1 | Alg         | orithm Overview                                        | 194      |

|      | 9.2 |             | dware-Directed Optimization Techniques                 |          |

|      | 9.3 |             | posed Hardware Architecture                            |          |

|      | 9.3 |             | Input Stage (IS)                                       |          |

|      | 9.3 | 3.2         | On-chip Memory Arrangements (MAs)                      | 197      |

|      | 9.3 | 3.3         | Calculation Stage (CS)                                 | 199      |

|      | 9.4 | Exp         | perimental Platform and Results                        | 199      |

|      | 9.4 | 4.1         | Experimental Platform                                  | 199      |

|      | 9.4 | 1.2         | Disparity Map Quality Analysis                         | 201      |

|      | 9.4 | 1.3         | Processing Speed                                       | 202      |

|      | 9.4 | 1.4         | Hardware Overheads                                     | 203      |

|      | 9.5 | Coı         | nclusion                                               | 204      |

|      | 9.6 | Ref         | erences                                                | 204      |

| 1    | 0 B | iogr        | raphy                                                  | 206      |

## LIST OF FIGURES

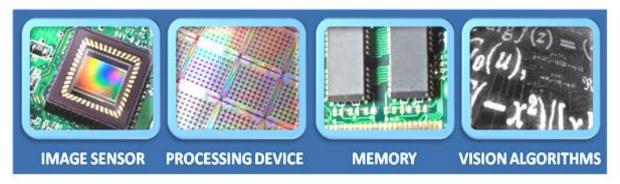

| Figure 1.1: Elements of an embedded vision system.                                                                                                                                                     | 3     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

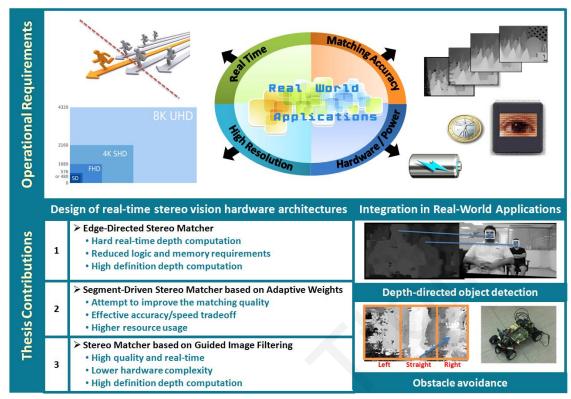

| Figure 1.2: Scope of Research and Thesis Contributions.                                                                                                                                                | 8     |

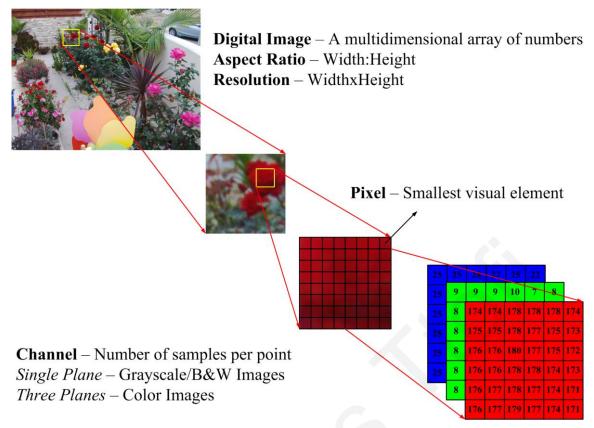

| Figure 2.1: Digital Image Representation in a Nutshell                                                                                                                                                 | 14    |

| Figure 2.2: Color vs. grayscale, vs. binary image.                                                                                                                                                     | 15    |

| Figure 2.3: Discetization of depth.                                                                                                                                                                    | 16    |

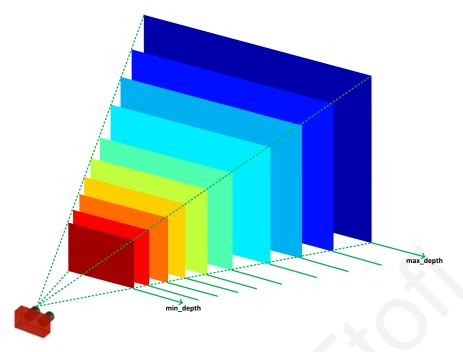

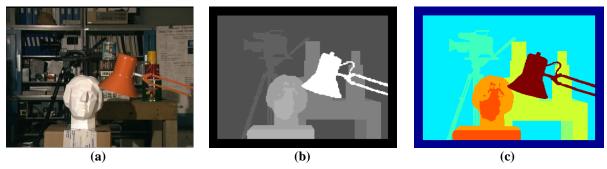

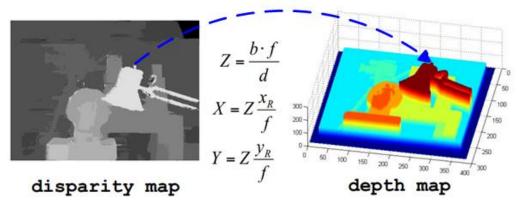

| Figure 2.4: Tsukuba (left view) and its grayscale and color-based 3D representation [25].                                                                                                              | 17    |

| Figure 2.5: (a) Teddy (left view). (b) Pseudo 3D depth map representation [24]                                                                                                                         | 17    |

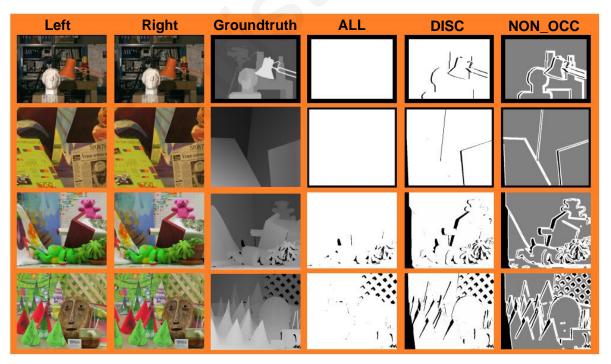

| Figure 2.6: Sample of stereo pairs in the Middlebury dataset with their corresponding g truth disparity maps and the ALL, DISC and NON_OCC regions                                                     | 18    |

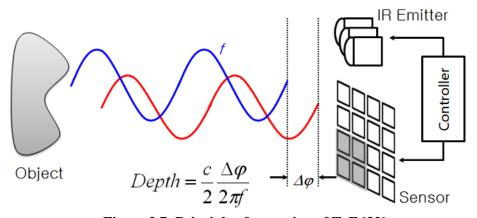

| Figure 2.7: Principle of operation of ToF [32]                                                                                                                                                         | 19    |

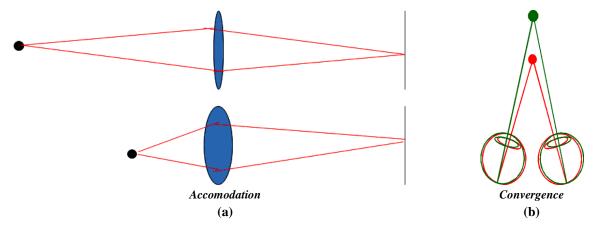

| Figure 2.8: Accomodation and Convergence in human visual perception system                                                                                                                             | 24    |

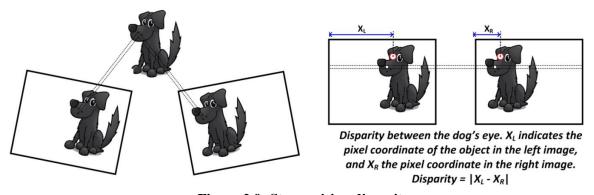

| Figure 2.9: Stereo vision disparity.                                                                                                                                                                   | 26    |

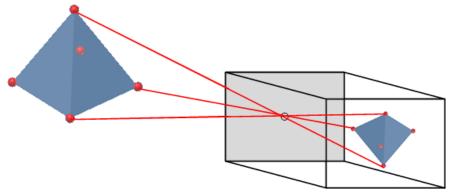

| Figure 2.10: The principle of a pinhole camera.                                                                                                                                                        | 27    |

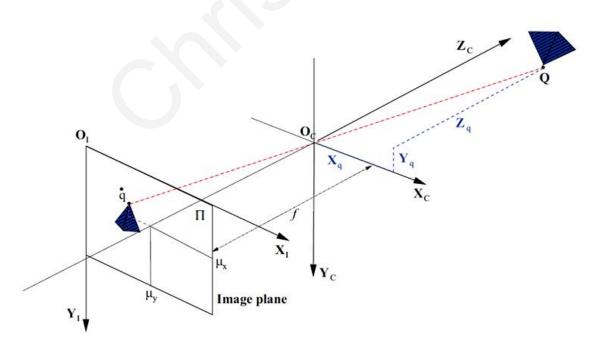

| Figure 2.11: The perspective projection.                                                                                                                                                               | 28    |

| Figure 2.12: The epipolar geometry.                                                                                                                                                                    |       |

| Figure 2.13: Stereo vision system overview.                                                                                                                                                            | 29    |

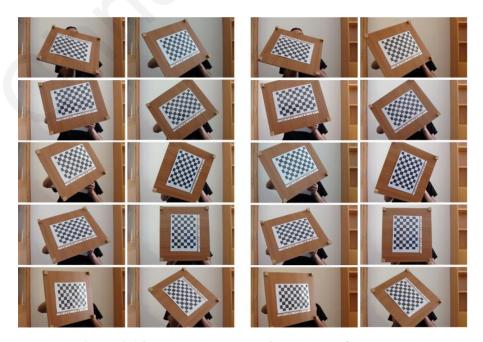

| Figure 2.14: Images used to calibrate the left camera.                                                                                                                                                 | 31    |

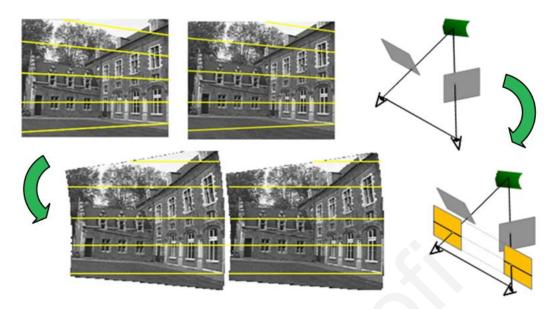

| Figure 2.15: Rectification transforms each image into a common image plane, aligning pairs of conjugate epipolar lines to the horizontal image axis [51].                                              | _     |

| Figure 2.16: Triangulation computes 3D coordinates of corresponding points                                                                                                                             | 34    |

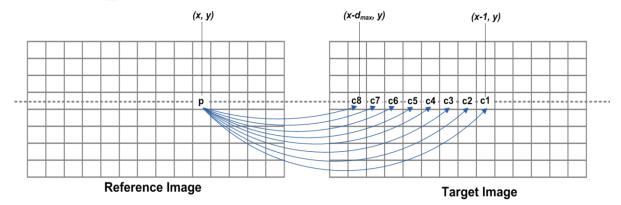

| Figure 2.17: The pixel-wise cost computation process.                                                                                                                                                  | 35    |

| Figure 2.18: Cost Aggregation Strategies.                                                                                                                                                              | 37    |

| Figure 2.19: Stereo image pairs showing the challenges of stereo matching                                                                                                                              | 47    |

| Figure 2.20: Examples of real-world applications of stereo vision technology. (a) humanoid robot from Aldebaran Robotics, (b) Mars rover, (c) Continental's Continental forward-looking braking system | Guard |

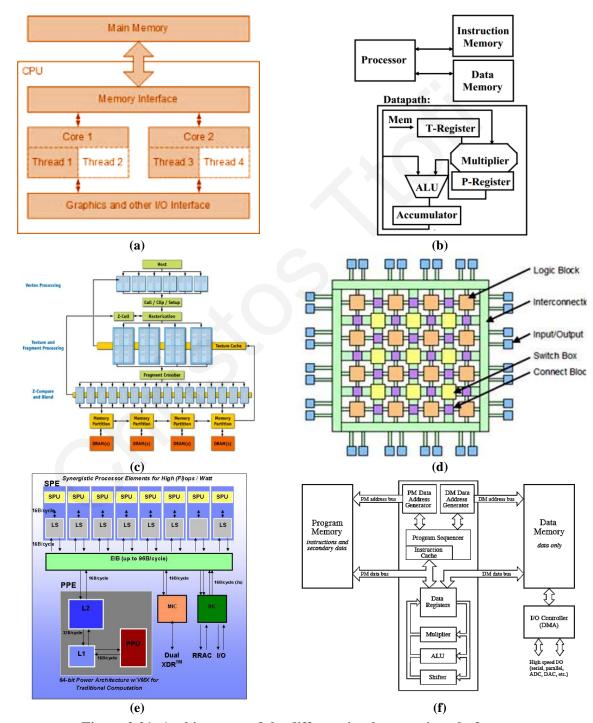

| Figure 2.21: Architectures of the different implementation platforms.                                                                                                                                  | 55    |

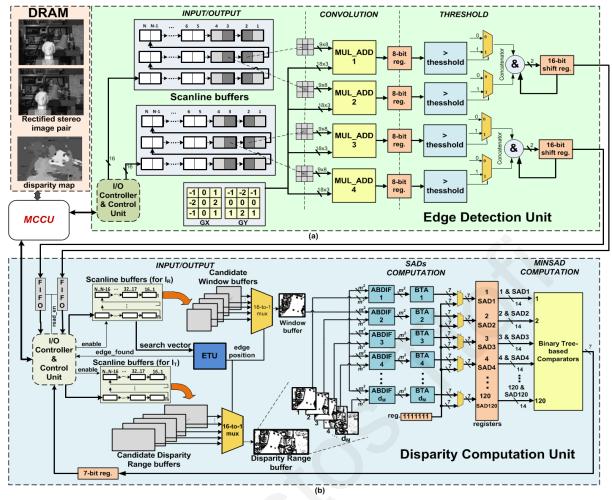

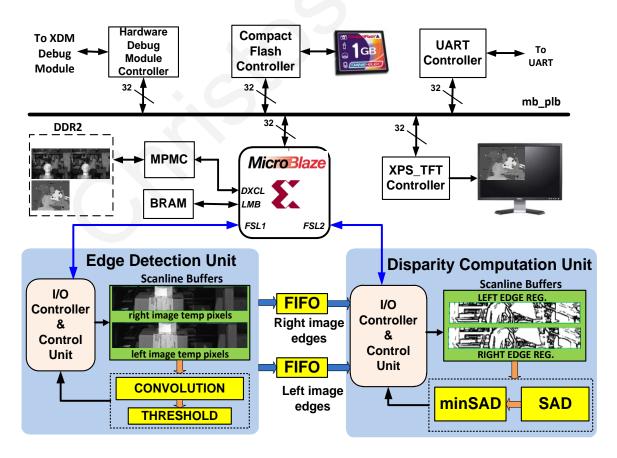

| Figure 3.1: Detailed block diagram of the proposed system architecture. (a) Edge determit (b) Disparity computation unit.                                                                              |       |

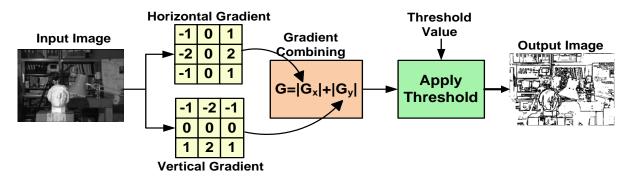

| Figure 3.2: Sobel edge detection overview.                                                                                                                                                             | 66    |

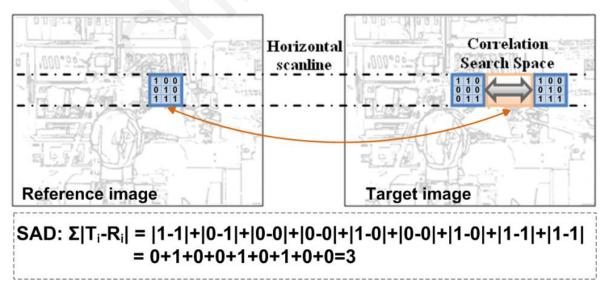

| Figure 3.3: Search area and SAD technique used in correlation matching.                                                                                                                                | 68    |

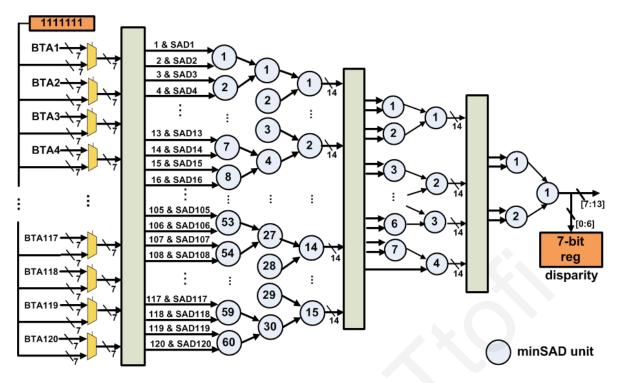

| Figure 3.4: Computing the minimum SAD value.                                                                                                                                                           | 72    |

| Figure 3.5: FPGA implementation used to verify the proposed architecture.                                                                                                                              | 73    |

| Figure 3.6: FPGA implementation used to verify the proposed architecture.                                                                                                                              | 74    |

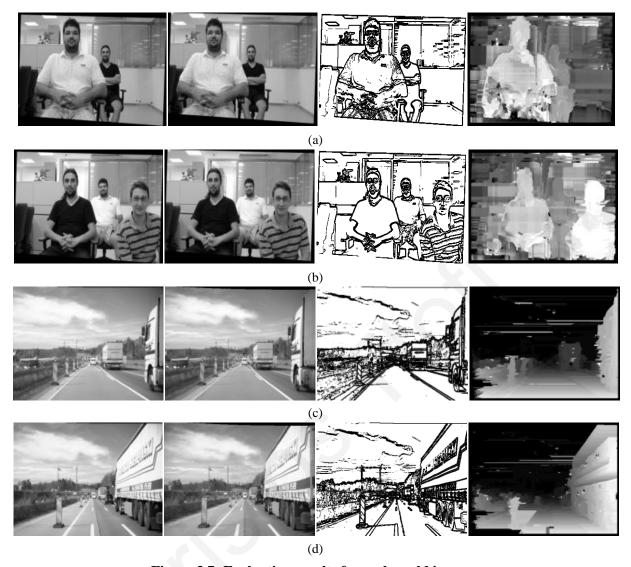

| Figure 3.7: Evaluation results for real-world images.                                                                                                                                                  | 75    |

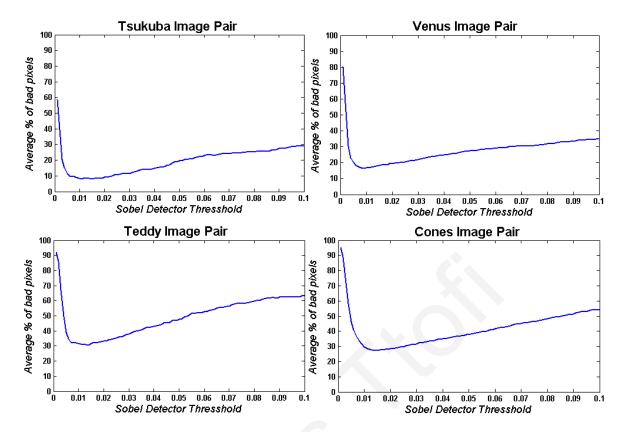

| Figure 3.8: Percentage of bad pixels vs. Sobel threshold                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

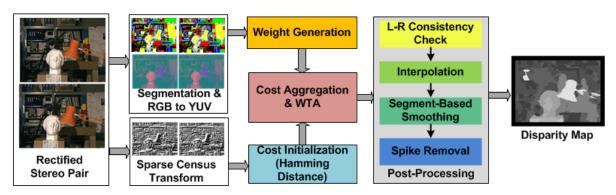

| Figure 4.1: Steps involved in the algorithm implemented by the proposed disparity estimation                                                                                                                             |

| architecture                                                                                                                                                                                                             |

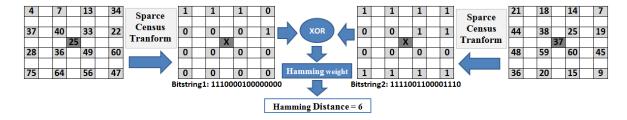

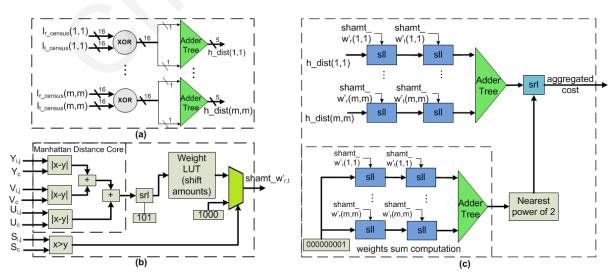

| Figure 4.2: Sparse Census transform and matching cost computation. The Hamming distance of the bitstrings resulting from sparse Census transform over $I_r$ and $I_t$ is the Hamming weight of Bitstring1 xor Bitstring2 |

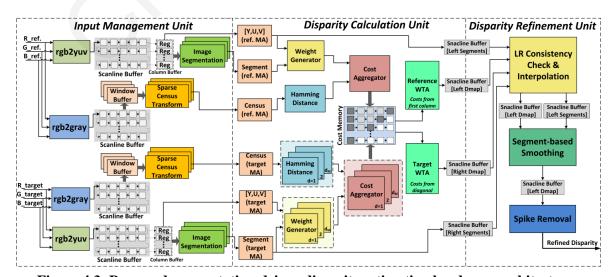

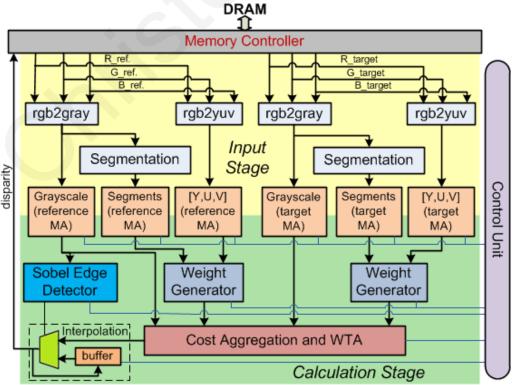

| Figure 4.3: Proposed segmentation-driven disparity estimation hardware architecture 97                                                                                                                                   |

|                                                                                                                                                                                                                          |

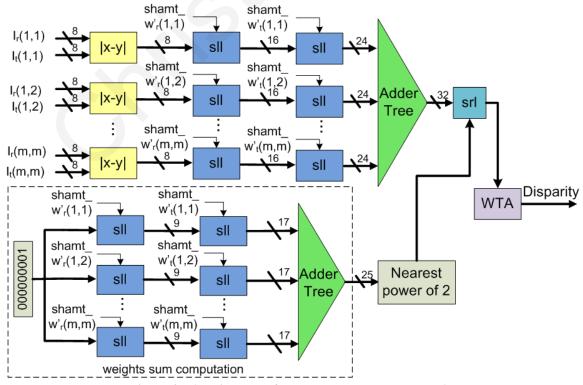

| Figure 4.4: Major units involved in the disparity calculation unit. (a) Hamming distance computation, (b) Weight generation, (c) Cost aggregation                                                                        |

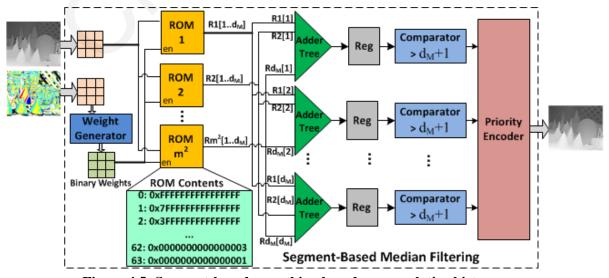

| Figure 4.5: Segment-based smoothing based on cumulative histograms                                                                                                                                                       |

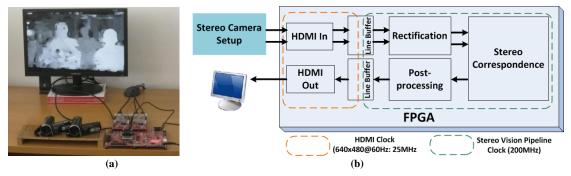

| Figure 4.6: FPGA prototype system. (a) Experimental testbed used to verify the operation of the system architecture, (b) Block diagram of system components                                                              |

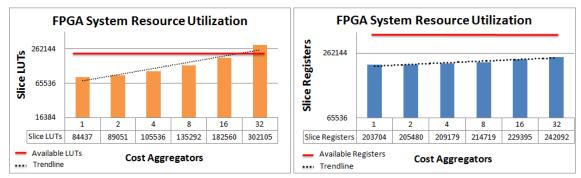

| Figure 4.7: Scalability analysis of full system on Kintex-7 FPGA (impact of the number of                                                                                                                                |

| aggregators on the amount of utilized FPGA resources). Axes with logarithmic scale (base 2).                                                                                                                             |

| Y-axes do not start at zero.                                                                                                                                                                                             |

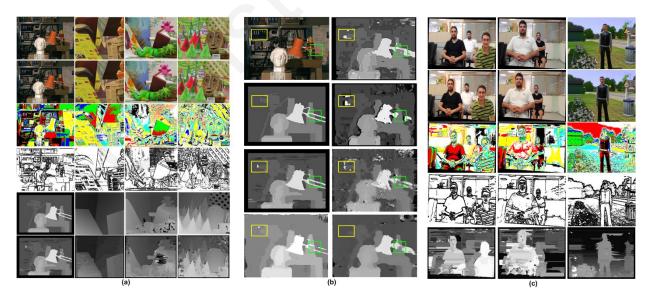

| Figure 4.8: Evaluation results with synthetic and real-world images. (a) Evaluation results of                                                                                                                           |

| the proposed system architecture and the original algorithm [Tombari et al. 2007] using                                                                                                                                  |

| Middlebury stereo pairs. From left to right: Reference image, Ground truth, Disparity maps                                                                                                                               |

| generated by the original algorithm, and Disparity map yielded by the proposed system. (b)                                                                                                                               |

| Evaluation results of real-world and synthetic scenes before and after applying post-processing steps. Real-world scenes captured in our laboratory (rows 1-2), a real-world scene with a                                |

| moving vehicle (row 3), and a synthetic scene of pedestrians (row 4)                                                                                                                                                     |

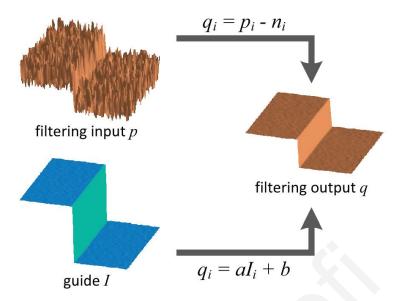

| Figure 5.1: Illustration of the guided image filtering process [141]                                                                                                                                                     |

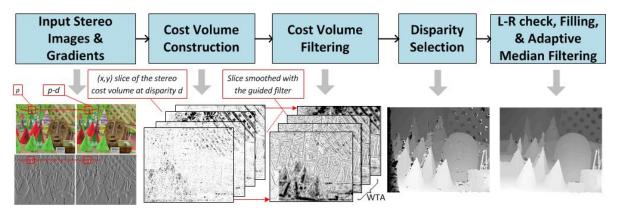

| Figure 5.2: Major Steps of the GIF-based Stereo Matching Algorithm                                                                                                                                                       |

|                                                                                                                                                                                                                          |

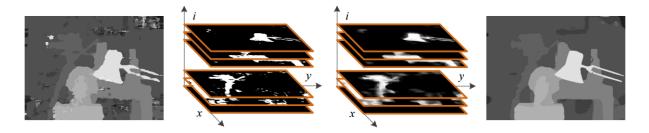

| Figure 5.3: Weighted median filtering over a noisy disparity map based on the GIF [143] 127                                                                                                                              |

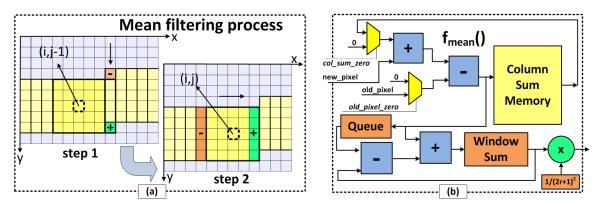

| Figure 5.4: (a) Mean Filtering Process. (b) Mean Filter Hardware Architecture                                                                                                                                            |

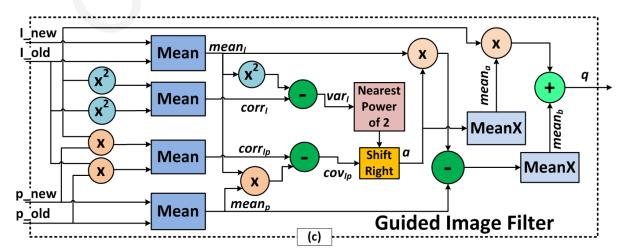

| Figure 5.5: Guided Image Filter Hardware Architecture                                                                                                                                                                    |

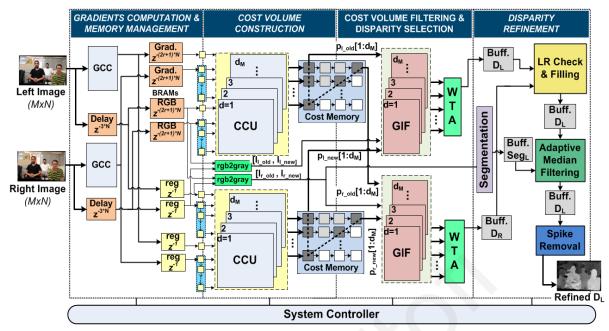

| Figure 5.6: Architecture of the proposed GIF-based Stereo Matcher                                                                                                                                                        |

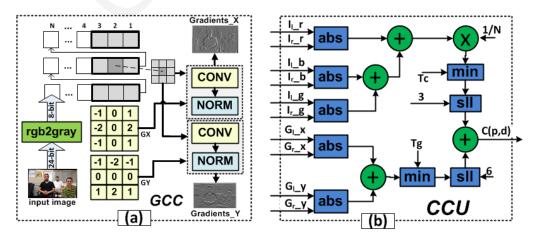

| Figure 5.7: (a) Gradients Computation Core, (b) Cost Computation Unit                                                                                                                                                    |

| Figure 5.8: Block diagram of the CVFDSU.                                                                                                                                                                                 |

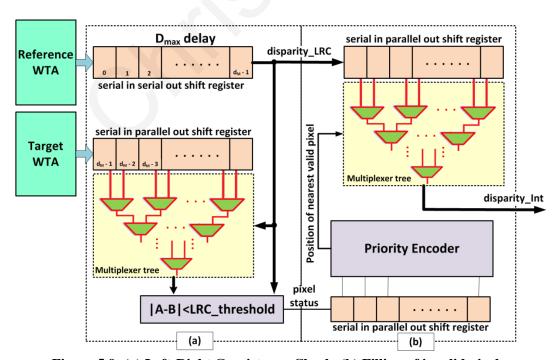

| Figure 5.9: (a) Left-Right Consistency Check, (b) Filling of invalid pixels                                                                                                                                              |

| Figure 5.10: (a) Experimental Testbed. (b) Benchmark Stereo Images. (c) Real-world Stereo                                                                                                                                |

| Pairs Captured in the Lab                                                                                                                                                                                                |

| Figure 5.11: Various Stereo Matching Hardware Designs utilizing the GIF                                                                                                                                                  |

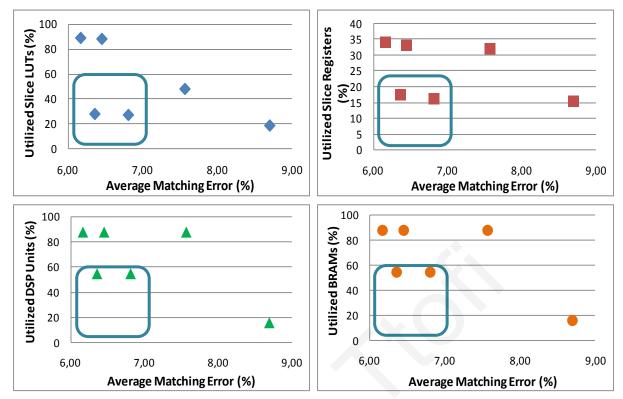

| Figure 5.12: FPGA resource usage/matching accuracy tradeoff analysis using scatter plots. 139                                                                                                                            |

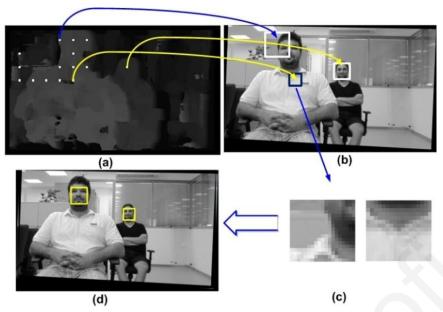

| Figure 6.1: Window Size Estimation Algorithm. (a) The disparity map is sampled every few pixels (b) For each disparity value the corresponding window size is estimated (c) Read                                         |

| window pixel values from one of the two stereo images (d) Output result of classific windows14                                                                                                                                                       |           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

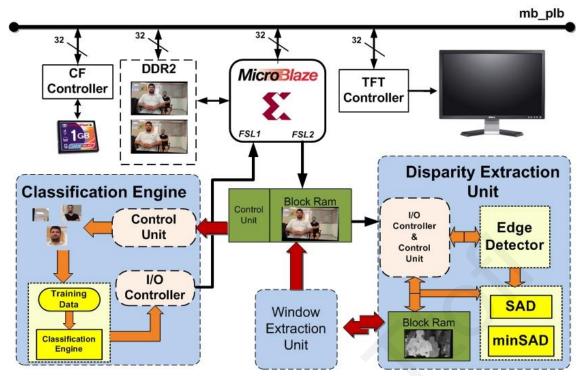

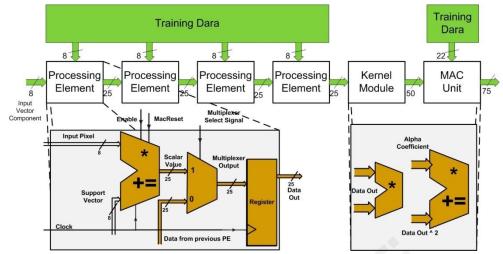

| Figure 6.2: Proposed Hardware System Architecture15                                                                                                                                                                                                  | 50        |

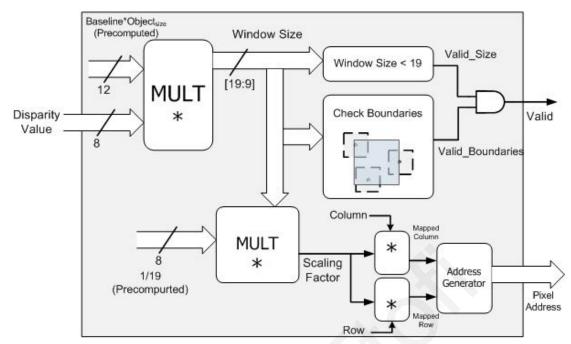

| Figure 6.3: Window Extraction Unit                                                                                                                                                                                                                   | 51        |

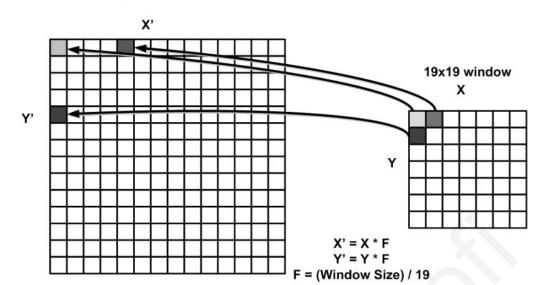

| Figure 6.4: Downscaling Process. Each coordinate in the 19x19 window is mapped to coordinate in the larger window. The coordinates where the 19x19 window coordinates a mapped, correspond to the pixels values that will be read for classification | re        |

| Figure 6.5: SVM classification engine architecture                                                                                                                                                                                                   | 53        |

| Figure 6.6: Evaluation Images and Results. (a) Right Images from stereoscopic pairs (Disparity Maps from stereo processing (c) Detection results using depth-guided method (Detection results using the traditional sliding window approach          | (d)<br>54 |

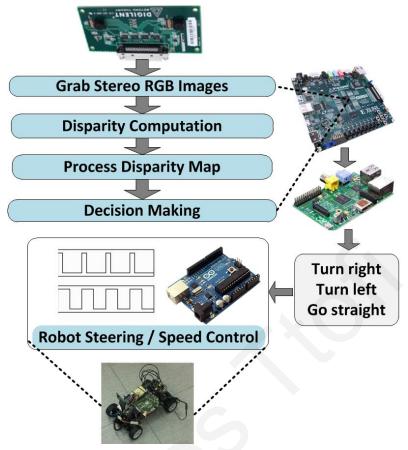

| Figure 6.7: Block diagram of the proposed robotic platform                                                                                                                                                                                           | 53        |

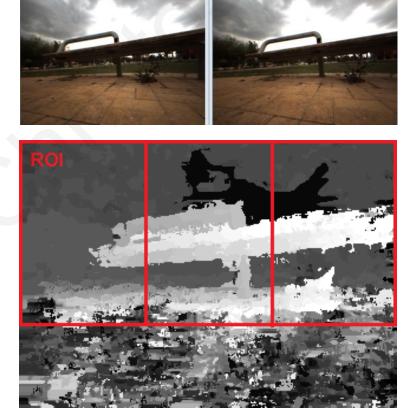

| Figure 6.8: Obstacle Avoidance Algorithm. (a) Input from Stereo Camera. (b) The region interest divided in three equally sized windows over the disparity map                                                                                        | of        |

| Figure 6.9: The Next State and Output Process of the Decision-Making Module 16                                                                                                                                                                       | 56        |

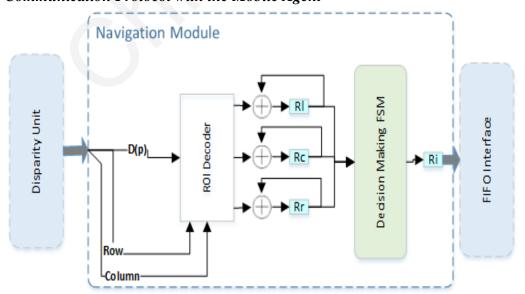

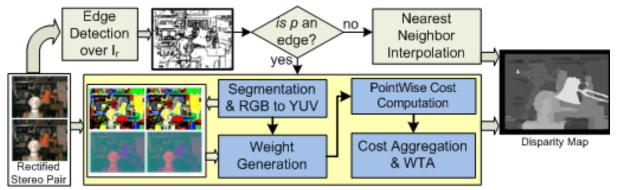

| Figure 6.10: Proposed navigation module architecture                                                                                                                                                                                                 | 56        |

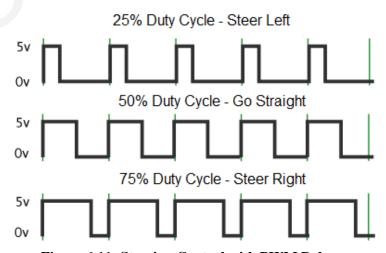

| Figure 6.11: Steering Control with PWM Pulses                                                                                                                                                                                                        | 57        |

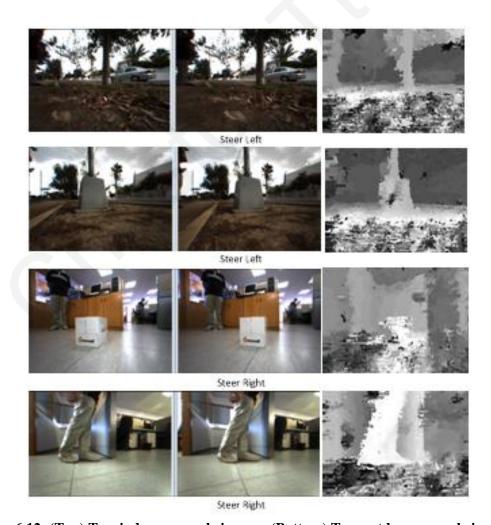

| Figure 6.12: Figure 6. (Top) Two indoor example images. (Bottom) Two outdoor example images with the decision beneath                                                                                                                                |           |

## LIST OF TABLES

| Table 2.1: Common Cost Aggregation Methods.                                             | 36  |

|-----------------------------------------------------------------------------------------|-----|

| Table 2.2: Classification of stereo matching algorithms.                                | 443 |

| Table 2.3: Comparison of the different implementation platforms.                        | 543 |

| Table 3.1: Input image pairs and the output of the EDU for the left image               | 765 |

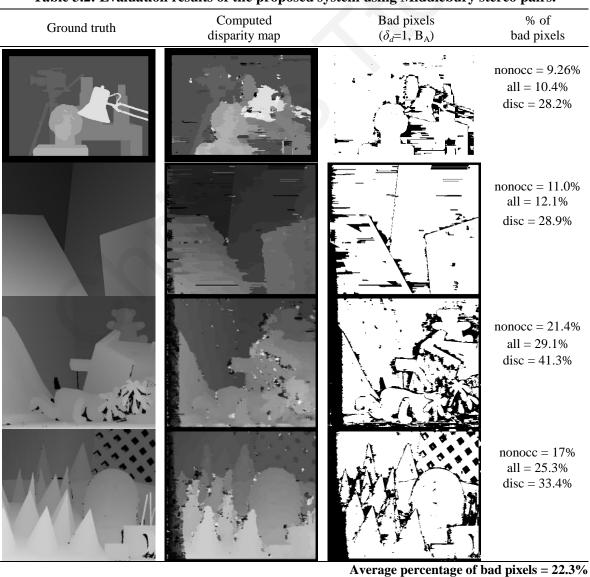

| Table 3.2: Evaluation results of the proposed system using Middlebury stereo pairs      |     |

| Table 3.3: Quality reduction for different edge detectors.                              | 787 |

| Table 3.4: Average percentage of bad pixels B <sub>E</sub> .                            | 787 |

| Table 3.5: Quality comparison of the proposed method with other methods                 |     |

| Table 3.6: Image size and system performance.                                           | 81  |

| Table 3.7: Comparison of MDE/s performance for various systems and methods              | 82  |

| Table 3.8: Resource utilization and maximum disparity range.                            | 85  |

| Table 3.9: Resource utilization and maximum window size.                                | 85  |

| Table 3.10: Resource utilization and maximum image size.                                | 85  |

| Table 3.11: Complete system hardware overheads.                                         | 86  |

| Table 4.1: FPGA Prototype Hardware Overheads                                            | 104 |

| Table 4.2: Resource Utilization Of Different FPGA Implementations                       | 105 |

| Table 4.3: ASIC implementation synthesis results.                                       | 106 |

| Table 4.4: Summary of existing disparity estimation systems.                            | 108 |

| Table 4.5: Comparison of the percentage of bad matching pixels between implementations. |     |

| Table 4.6: Average performance ranking.                                                 |     |

| Table 5.1: Definition of the various stereo matching designs that utilize the GIF       | 137 |

| Table 5.2: FPGA resource usage of the various system configurations                     | 138 |

| Table 5.3: Matching accuracy of the different system configurations                     | 138 |

| Table 5.4: Quality and Processing Speed Comparison with Related Work                    | 141 |

| Table 5.5: Kintex-7 Synthesis Results for major system components                       | 142 |

| Table 6.1: Performance for different system configurations.                             | 155 |

| Table 6.2: Hardware requirements for each unit and different system configurations      | 156 |

| Table 6.3: Evaluation results in indoor environments.                                   | 170 |

| Table 6.4: Evaluation results in outdoor environments.                                  | 171 |

| Table 65: FPGA Platform Parameters                                                      | 171 |

#### LIST OF ABBREVIATIONS

#### (In Alphabetical Order)

2D Two Dimensional

3D Three Dimensional

ABDIF Absolute Difference

AD Absolute Difference

ADSW Adaptive Support Weight

ALL All Image Regions

API Application Programming Interface

ASIC Application Specific Integrated Circuit

BP Belief Propagation

BTA Binary Tree Adders

CBE Cell Broadband Engine

CCU Cost Computation Unit

CE Classification Engine

CONV Convolution

CPU Central Processing Unit

CS Calculation Stage

CVC Cost Volume Construction

CVCU Cost Volume Construction Unit

CVF Cost Volume Filtering

CVFDSU Cost Volume Filtering Disparity Selection Unit

CW Constant Window

DCU Disparity Computation Unit

DCU Disparity Calculation Unit

DEU Disparity Extraction Unit

DISC Regions with Depth Discontinuities

DMA Direct Memory Access

DP Dynamic Programming

DRU Disparity Refinement Unit

DS Disparity Selection

DSI Disparity Space Image

DSP Digital Signal Processor

EDK Embedded Development Kit

EDU Edge Detection Unit ETU Edge Tracking Unit FIFO First-In First-Out

FPGA Field Programmable Gate Array

FPS Frames per Second FSL Fast Simplex Link FW Fixed Window

GCC Gradient Computation Core

GCMMU Gradient Computation Memory Management Unit

GIF Guided Image Filter

GPP General Purpose Processor GPU Graphics Processing Unit

HD High Definition

HDL Hardware Description Language

I/O Input / Output

IMU Input Management Unit IP Intellectual Property

IR Infrared IS Input Stage

LoG Laplacian of Gaussian

LR-check Left-Right Consistency Check

LS Local Store LUT Look-up Table

MA Memory Arrangement

MCCU Memory Controller Control Unit

MDE/s Million Disparity Estimations per second

MFC Memory Flow Controller

MRF Markov Random Field

MUL\_ADD Multiplication-Addition

MW Multiple Window

NCC Normalized Cross Correlation

NN Nearest Neighbor

NON\_OCC Non Occluded Regions

NORM Normalization

NRE Non Recursive Engineering

PLB Processor Local Bus

PPE PowerPC Processor Element

PPU Power Processing Unit

PWM Pulse Width Modulation

RMS Root-Mean-Square

RoI Region of Interest

RPi Raspberry Pi

RSB Reference Scanline Buffer

SAD Sum of Absolute Difference

SC System Configuration

SCV Stereo Cost Volume

SDK Software Development Kit

SGM Semi Global Matching

SHD Sum of Hamming Distances

SIMD Single Instruction Multiple Data

SMT Simultaneous Multithreading

SNR Signal to Noise SoC System on a chip

SPE Synergistic Processing Element

SSD Sum of Square Differences

SSE Streaming SIMD Extensions

SVMSupport Vector MachineSXUSynergistic eXecution UnitTADTruncated Absolute Difference

TFT Thin Film Transistor

ToF Time of Fight

TSB Target Scanline Buffer UHD Ultra High Definition USB Universal Serial Bus

VLIW Very Long Instruction Word

VW Varying Window

WEU Window Extraction Unit WMF Weight Median Filtering

WTA Winner-Takes-All

# CHAPTER 1

# Introduction to Embedded Vision and Depth Perception - Thesis Motivation & Contributions

The development of a stereo vision system comprises an interdependent design process, where the efficiency of the resulting system depends both on the hardware architecture and the associated algorithms. The design of such a system becomes even more challenging when targeting applications in embedded and mobile environments, where cost, energy and memory overheads need to be minimized. This thesis investigates hardware architectures of stereo vision algorithms that have the potential to satisfy the requirements of constrained embedded vision applications. This chapter has two purposes. First, it provides an overview on the development and deployment of embedded vision / stereo vision technology into a variety of interesting and promising applications, highlighting advances in enabling technologies, including processors, sensors, and development platforms. Second, it motivates the thesis background, and summarizes its main contributions and the individual chapters.

#### 1.1 The Embedded Vision Revolution

Most of us have smart phones and tablets with front- and rear-viewing cameras capable of capturing high-resolution still images and high-definition video clips. Many of us have enjoyed the fresh new gaming experiences offered by the Xbox's Microsoft Kinect and Sony's Playstation 4 video game consoles. Some of us may even have a car with a rear-view parking camera, or a more advanced driver assistance system capable of detecting pedestrians, lanes, or even classify various traffic signs including speed limit signs, etc. What we may not realize is that all of these devices, which have recently become an essential part of our everyday lives, have something in common – *embedded vision*.

Embedded vision is a technology that entails a hybrid of two well-established fields: Embedded Systems and Computer Vision. This emerging technology aims at incorporating automated image analysis and vision capabilities into any kind of a computer-based system that is not a general purpose computer, but rather it is designed to perform certain tasks only. Using digital processing and intelligent algorithms, an embedded vision system can extract and interpret meaning from images or video, enabling it to understand the surrounding world and interact with its host environment [1]. Embedded vision can lead to the development of safer, smarter and more responsive machines, which like humans, see and understand. To put it simply, embedded vision refers to devices or machines that are empowered with the gift of sight, and are able to see and understand their environment!

Although computer vision algorithms have been extensively studied over the last few decades in academic research, they have only been implemented using large, heavy, expensive, and power-draining computers, restricting their usage to a short list of applications such as factory automation / assembly line inspection, optical character recognition and military systems [2]. In recent years, however, the emergence of very powerful, low-cost and energy-efficient processors, image sensors, memories, and other semiconductor devices, along with robust computer vision algorithms, has made embedded vision much more accessible and feasible [3]. Nowadays, even inexpensive smart phones and tablets are capable to supply formidable processing capabilities, including multi-core high-frequency CPUs and embedded graphics processors, on-chip DSPs and imaging coprocessors, and multiple gigabytes of memory. They are also provided with front- and rear-viewing camera sensors that support high image resolutions and frame rates. Therefore, a major transformation is underway, aiming to integrate vision capabilities into a wide variety of embedded systems and electronic products to make them more intelligent and responsive than before, and thus more valuable to the users.

An embedded vision system is comprised of four major elements [4], which are illustrated in Figure 1.1. The image sensor outputs images at some resolution of pixels and a specific rate, which corresponds to how many image frames the sensor outputs per second. These images are processed by an embedded processing device, in the form of specialized processors that implement unique architectures, or dedicated accelerators specific to image and video processing. Image sensors generate image/video data in a streaming fashion. Processing the data output from the video sensor usually requires storing in memory either all or some parts of the image/video. Finally, specialized vision algorithms are required to manipulate and analyze the vast amount of incoming video data to extract visual meaning about the surrounding 3D world.

Figure 1.1: Elements of an embedded vision system.

Due to continues technological advances in sensors, processors, memory and algorithms, embedded vision systems have nowadays the potential to revolutionize a multitude of industries, including medicine, advertising, security, personal health, entertainment, automotive and more [5]. Embedded vision has high potential in medicine, where it can be incorporated for example in medical electronic devices such as intelligent x-ray and MRI systems to assist radiologist to rapidly and accurately identify image irregularities, eliminating degrading factors like fatigue and distraction, which occurred when the image analysis is performed by humans [6]. Another medical application involves the detection of skin cancer signs in moles on the human body, using a smartphone to capture images of a mole and process them by a complex vision algorithm developed by dermatologists [6]. Other revolutionary medical applications aim at providing assistance to blind people, by utilizing a camera to interpret real objects and communicate them to the user as auditory cues [7]. In automotive, vision-based systems utilize gesture and face recognition for car safety; the driver for example can use a winking of the eye to turn the radio on and off, or a movement of the head to change the volume, thus reducing distractions while driving [7]. Furthermore, the ability of such systems to detect meaning from images of the road ahead the car could be used to provide warnings if for example a car begins leaving a lane, approaches a car too closely, or detects a bicycle or a pedestrian. Furthermore, active research in the field of embedded vision aims to incorporate face recognition for advertising, in order to track the facial responses of internet users while they view online advertisements [7]. In general, the era of embedded vision has just started. We would need several pages to list the abundant applications that could benefit from the use of this emerging technology, as the technology's potential is fundamentally limited only by our imagination. Moreover, there are great expectations that within the next ten years, embedded vision will broaden and accelerate its penetration into numerous new markets, creating exciting products for a range of applications [2].

The rapid proliferation of embedded vision technology is considered similar to the evolution of high-speed wireless connectivity, which initially began as an exotic and costly technology found only in complex and expensive systems, but when digital circuits got fast enough, inexpensive enough, and energy efficient enough, it became a mass-market technology. Today, advances in digital integrated circuits are critical enough to pave the way for the proliferation of embedded vision into high volume applications, in virtually every category of electronic products, from automobiles to consumer electronics to health care, etc.

Embedded vision applications usually rely on advanced computer vision algorithms that typically require high processing performance. In addition, they are deployed in embedded systems of all kinds that need to fit into tight memory, power consumption, size, communication bandwidth and cost envelopes. In contrast to other digital signal processing application domains, such as wireless communications, where the aforementioned constraints are satisfied by the use of specialized accelerators and coprocessors implemented on Application Specific Integrated Circuits (ASICs), the use of non-programmable accelerators is less attractive for embedded vision applications. This is mainly attributed in the fact that there are no common standards available to constrain the choice of vision algorithms; there are usually many approaches to choose from to solve a particular vision problem. As such, the majority of computer vision algorithms are implemented on programmable embedded computing platforms such as Digital Signal Processors (DSPs), Field Programmable Gate Arrays (FPGAs), and several kinds of multi-core Central Processing Units (CPUs) [2]. These platforms though are based on heterogeneous and specialized architectures, therefore, to meet the challenging combination o high performance, low power and low cost, embedded vision systems are required to exploit the inherent parallelism found in such architectures. Efficient development methods are also an important issue.

Besides the general parameters of performance, cost and integration associated with the computing platform, there are also other critical parameters that restrict the computing devices that can be selected for implementing computer vision applications. Factors such as the way in which data are transferred to the device (I/O operations), the data type and representation, and the program flow, are all critical towards delivering revolutionary vision processing in performance-demanding and power-sensitive embedded vision applications [8]. Hence, an embedded vision system must be able to deal with all of them.

### 1.2 Embedded Stereo Vision - Motivation

Among the most important tasks of an embedded vision system is the extraction of depth information. This can become possible through stereo vision technology, which delivers precise depth information of the observed scene in a manner similar to human binocular vision [9], [10], [11]. It uses two cameras that capture the same scene from two different viewpoints, and depth information is inferred by finding corresponding points in the two images, a process known as stereo matching (or disparity estimation). Stereo vision has enabled the realization of applications, which so far could not be done with classical 2D computer vision technologies [11]. Many applications of stereo vision are in inspection, medicine, automotives, etc. [11]. Moreover, detailed 3D information about the surrounding world is important to enable autonomous navigation, obstacle detection and classification in unknown environments [12]. Therefore, stereo vision is also used in several consumer electronics and multimedia products that demand vision-based autonomous behaviors (e.g. mobile robots, intelligent surveillance and autonomous vehicles). One successful example is the UK's Oxford robot car, an autonomous car recently unveiled by a team from Oxford University that uses stereo vision to locate and track vehicles [13]. The new Mercedes-Benz S-class 2014 also features a stereoscopic camera that sees objects ahead in 3-D and helps to detect cross-traffic and pedestrians [14]. With products like these demonstrating what it is possible, several other application areas of stereo vision that span virtually every embedded market will experience huge growth rates in the near future.

While stereo vision is a rather popular and important subject in the fields of machine vision and image analysis, it is a computationally expensive task. Therefore, its use in consumer electronics and multimedia products has posed new challenges that need to be tackled. Such systems usually impose several, often contradictory constraints, including real-time processing, high matching accuracy and low power consumption. This makes the successful realization of an embedded stereo vision system a key challenge, both in terms of the matching algorithm, as well as in terms of the implementation platform. On one hand, implementations of complex stereo matching algorithms produce very accurate results but rely on the high-end hardware resources of multi-core CPUs and/or GPU platforms to achieve real-time processing. Such platforms therefore are unsuitable for the realization of stand-alone stereo matching systems, and also consume excessive power, which is not desirable in embedded vision applications, especially in the case of battery-operated devices. DSP

platforms, on the other side, feature lower power consumption than software implementations running on high-end processors or GPUs, thus they are more favorable in embedded stereo vision applications. However, the fixed logic and small number of processing cores prohibit this platform from offering the required parallelism for real-time performance. Recent research indicates that application-specific hardware acceleration using either FPGAs or custom circuits (ASICs) might be the most appropriate solution for embedded stereo vision applications, since it can provide high computational power with low power consumption. Furthermore, it allows the architectures to be designed in a customized way; therefore, the computational resources can be optimized in terms of resource utilization. To this end, a lot of work has been carried out on real-time dedicated hardware implementations of disparity estimation algorithms on both FPGAs and ASICs. However, FPGAs remain the most popular implementation choice because of their inherent parallelism, re-programmability and great flexibility in manipulating the algorithm, and relatively short design cycle.

Application-specific hardware acceleration has been proven to be a promising means towards designing efficient stereo matching hardware architectures. Existing efforts towards this direction have yielded encouraging results, yet satisfying the hard real-time constraints of emerging embedded stereo vision applications, especially for High Definition (HD) images and under limited resource usage, is still challenging. Moreover, existing dedicated hardware implementations are mostly directed towards implementing simple stereo algorithms, therefore trading accuracy for speed. Hence, this research is concerned with the implementation of hardware architectures of different stereo matching algorithms, which can be used to satisfy the different constraints involved in embedded environments.

# 1.3 Objectives and Scope of Research - Thesis Contributions

The scope of this thesis is on dedicated hardware architectures of stereo matching algorithms for efficient 3D perception in embedded applications. Although there have been several attempts recently to implement real-time stereo vision systems on dedicated hardware, most of them cannot satisfy hardware efficiency and memory footprint requirements that characterize vision applications running on platforms with limited resources. As such, the first problem addressed in the thesis is how to find novel ways to satisfy the requirements of hard real-time, resource constrained embedded vision applications. The thesis proposes the design of a hybrid, block- and feature-matching stereo algorithm; through an edge detector that generates the features (edges) used to reduce the search space, and a block matching Sum of

Absolute Difference (SAD) algorithm used for the stereo matching computation. The integration of edge information constrains the stereo matching process only on binary data (edges), therefore reducing the search space and improving the overall frame-rate, while also reducing the logic and memory requirements, thus enabling the design of a parallel, scalable and resource-optimized architecture that is able to process HD stereo images in real time (50Hz@1280x1024). Furthermore, edges represent reliable image features, and their use reduces the sensitivity to pixel intensity variations caused by camera gain or illumination changes. Therefore, the proposed edge-directed architecture outperforms traditional SAD block matching-based hardware architectures in terms of matching quality. These features make the developed architecture suitable for resource-constrained embedded vision systems that need to satisfy hard real-time and low-power constraints.

However, many of today's applications not only need to satisfy embedded constraints but also the extremely high matching accuracy offered by more complex stereo algorithms. Hence, the second problem address in the thesis is the implementation of complex stereo matching algorithms through hardware-oriented algorithmic modifications, in an attempt to balance accuracy and speed in embedded stereo vision applications. To this end, the second part of the thesis presents the design of an Adaptive Support Weight (ADSW) algorithm that integrates information obtained from image segmentation in an attempt to improve the robustness of the matching process. The thesis also presents hardware-oriented algorithmic modifications and optimization techniques that make the algorithm hardware-friendly and compatible with embedded constraints. A prototype of the architecture was implemented on a Kintex-7 FPGA board, achieving 60 frames per second (fps) for 640x480 image sizes. At the same time, synthesis results targeting a commercial CMOS 65-nm cell library indicate that the architecture can be extended to larger scale systems.

The good quality results of the segment-based ADSW architecture come at the expense of high resource usage. As a result, a final but important objective of the thesis is the design of a stereo matching hardware system able to satisfy both speed and accuracy aspects with low resource requirements. To this end, the thesis focuses on the design of a fully pipelined, parallel and scalable stereo matching hardware architecture based on the recently proposed Guided Image Filter. This type of filter has been employed to reduce the complexity of the cost aggregation step in ADSW methods implemented in software. Therefore, the thesis aims to present a new and efficient hardware design of the GIF (that can be potentially adopted in

Figure 1.2: Scope of Research and Thesis Contributions.

other uses of the filter), and also to explore and concurrently discuss the hardware design parameters and optimizations involved in integrating the GIF hardware architecture in the cost aggregation step of ADSW-based hardware stereo matching systems. The latter reduces the overall hardware complexity of cost aggregation, which in turn allows real-time stereo matching of HD images, as well as improvements of the overall matching accuracy, thanks to the edge-preserving property of the GIF.