# THE TFLUX PLATFORM: A PORTABLE PLATFORM FOR DATA-DRIVEN MULTITHREADING ON COMMODITY MULTIPROCESSOR SYSTEMS

Kyriakos Stavrou

University of Cyprus, 2009

This work presents the *Thread Flux* (*TFlux*) *Parallel Processing Platform*, a complete system that offers an efficient dataflow-like thread-based model of execution, the *Data-Driven Multi-threading* (DDM), to its users using commodity components, *i.e.* unmodified Operating System, unmodified compiler and unmodified ISA hardware making it applicable to *off-the-shelf* systems. *TFlux* provides a complete solution from the programming toolchain to the hardware implementation. The abstraction layer *TFlux* exports to its users hides all the details of the underlying machine allowing different hardware configurations to support its model of execution transparently to the programmer. One key component of TFlux is the TFlux Scheduler that is responsible for Thread Scheduling based on data-availability.

The user of *TFlux* can develop applications using a set of simple but powerful compiler directives. Then the TFlux-C-Preprocessor converts this code to an ANSI C program that includes the Runtime Support for *TFlux* and all calls to the system's scheduler. This code can be compiled with a commodity C compiler resulting in a binary that is executable by any commodity Operating System on any commodity CPU processor. The layered design of *TFlux* has been tested on different Unix-based multiprocessor systems. Moreover, this design enabled the porting of *TFlux* to different machines with minimum effort.

In this work, two *TFlux* designs are presented: *TFluxHard* and *TFluxSoft*. For *TFluxHard* the Thread Scheduler is a hardware unit whereas for *TFluxSoft*, the Scheduler's functionality is

provided at the software level. As such, *TFluxHard* is applicable to systems that offer the ability to augment the machine with a small hardware module while *TFluxSoft* is directly applicable to any existing, *off-the-shelf* system.

To evaluate the *TFlux* designs, a benchmark suite based on real-life and synthetic applications was developed. The applications in this suite were carefully chosen in order to have different characteristics both in terms of their dynamic behavior and complexity of their dataflow graph.

For the applications of the evaluation suite, both *TFluxHard* and *TFluxSoft* show remarkable speedup and scalability. Although for most applications both achieve almost the same performance, *TFluxHard* shows an advantage over *TFluxSoft* arising from offloading the Scheduler's functionality to the hardware module. In addition, the experimental results also show that both *TFluxHard* and *TFluxSoft* are able to exploit more parallelism for applications with complex dependency graphs, compared with traditional parallel programming model approaches.

Overall, *TFlux* is a platform able to deliver high-performance by exploiting dataflow-like Thread scheduling on *off-the-shelf* systems through augmentation of the source code with simple compiler directives.

# THE TFLUX PLATFORM: A PORTABLE PLATFORM FOR DATA-DRIVEN MULTITHREADING ON COMMODITY MULTIPROCESSOR SYSTEMS

Kyriakos Stavrou

A Dissertation

Submitted in Partial Fulfillment of the

Requirements for the Degree of

Doctor of Philosophy

at the

University of Cyprus

Recommended for Acceptance

by the Department of Computer Science

January, 2009

© Copyright by

Kyriakos Stavrou

All Rights Reserved

2009

## **APPROVAL PAGE**

Doctor of Philosophy Dissertation

Presented by

Kyriakos Stavrou

| Research Supervisor |                      |

|---------------------|----------------------|

|                     | Pedro Trancoso       |

|                     |                      |

| Committee Member    |                      |

|                     | Marios Dikaiakos     |

|                     |                      |

| Committee Member    |                      |

|                     | Paraskevas Evripidou |

|                     |                      |

| Committee Member    |                      |

|                     | Lasse Natvig         |

|                     |                      |

| Committee Member    |                      |

|                     | Costas Pattichis     |

|                     |                      |

| Committee Member    |                      |

|                     | Theo Ungerer         |

|                     |                      |

University of Cyprus

January, 2009

## ACKNOWLEDGEMENTS

This thesis would not have been possible without many people's help. The first person I would like to thank is my advisor Dr. Pedro Trancoso who was always there in the good and bad times. His help was not limited to guiding and supervising this work but also at the personal level. He has supported all my professional steps but also he was there as a friend during all these years. In addition to my advisor, I would like to thank my other advisor, Professor Paraskevas Evripidou who had an important role on the design of the TFlux Platform through his comments, ideas and experience.

For parts of this work I need to acknowledge and thank other researchers. Demos Pavlou and Marios Nicolaides have contributed to the implementation of the TFluxSoft platform and the extension of the TFlux Preprocessor. The help of Demos and Marios, who I had the luck to work with for almost two years, also covered the evaluation of the TFlux platform, design and plan of optimizations for TFluxSoft and the authorship of a number of papers published during this work. Moreover, I want to thank Samer Arandi who had an important contribution on the implementation of TFluxCell. I would also like to thank Panayiotis Petrides for his help on benchmarks.

In addition, I would like to thank my committee members, Professor Constantinos Pattichis, Professor Marios Dikaiakos, Professor Lasse Natvig and Professor Theo Ungerer for their valuable comments.

I am also grateful to the organizations that partially funded this work, the Cyprus Research Promotion Foundation and the HiPEAC network of excellence. Professor Stamatis Vassiliadis was the distinguished collaborator in the project that gave us the larger portion of funding for this work. Although this is something for which I am really grateful, what I would really like to thank him about are some other, more important things; for showing the road, for inspiring, and for reminding that kindness, wisdom and success can coexist.

Last but not least I want to thank my family; my father Avramis, my mother Xenia, my brother Stavros and of course Avra. It is not possible to define the things I thank them for just because I want to thank them for everything they did for me.

# TABLE OF CONTENTS

| Chapter | r 1: Introduction                                                       | 1  |

|---------|-------------------------------------------------------------------------|----|

| 1.1     | The TFlux Parallel Processing Platform                                  | 4  |

| 1.2     | Contributions                                                           | 7  |

| Chapter |                                                                         | 9  |

| 2.1     | The Shift to Multicore Systems                                          | 9  |

| 2.2     | Parallel Programming Models                                             | 11 |

| 2.3     | The Dataflow Model of Computation                                       | 17 |

|         | 2.3.1 Dataflow Architectures                                            | 18 |

|         |                                                                         | 20 |

|         | 2.3.3 Hybrid Dataflow                                                   | 22 |

|         | 2.3.4 Non-blocking Multithreading                                       | 23 |

|         | 2.3.5 Recent Dataflow Developments                                      | 24 |

| 2.4     | Data-Driven Multithreading (DDM)                                        | 27 |

| 2.5     | Data-Driven Multithreading Network of Workstations (D <sup>2</sup> NOW) | 30 |

| 2.6     | Data-Driven Multithreading Chip Multiprocessor(DDM-CMP)                 | 31 |

| Chapter | r 3: The TFlux Parallel Processing Platform                             | 32 |

| 3.1     | TFlux Layered Design                                                    | 32 |

|         | 3.1.1 Runtime Support                                                   | 34 |

|         | 3.1.2 TFlux Kernel                                                      | 35 |

|         | 3.1.3 The TFlux Scheduler                                               | 36 |

|         | 3.1.4 Compilation Toolchain                                             | 38 |

|     | 3.2          | Basic I                                                                         | Execution Components                                                                                                                                                                                                           | 39                                                        |

|-----|--------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

|     |              | 3.2.1                                                                           | Data-Driven Threads (DThreads)                                                                                                                                                                                                 | 39                                                        |

|     |              | 3.2.2                                                                           | TFlux Loops                                                                                                                                                                                                                    | 40                                                        |

|     |              | 3.2.3                                                                           | Thread Recycling                                                                                                                                                                                                               | 50                                                        |

|     |              | 3.2.4                                                                           | Blocks                                                                                                                                                                                                                         | 51                                                        |

|     | 3.3          | TFlux                                                                           | Scheduler Basic Operations                                                                                                                                                                                                     | 53                                                        |

|     |              | 3.3.1                                                                           | Thread Load                                                                                                                                                                                                                    | 53                                                        |

|     |              | 3.3.2                                                                           | Thread Completion                                                                                                                                                                                                              | 53                                                        |

|     |              | 3.3.3                                                                           | Thread Update                                                                                                                                                                                                                  | 56                                                        |

|     |              | 3.3.4                                                                           | Find Ready Thread                                                                                                                                                                                                              |                                                           |

|     |              | 3.3.5                                                                           | Clear TSU                                                                                                                                                                                                                      | 56                                                        |

|     | 3.4          | TFlux                                                                           | Incarnations                                                                                                                                                                                                                   | 56                                                        |

|     | 5.4          | IIIux                                                                           |                                                                                                                                                                                                                                | 50                                                        |

|     | apter        |                                                                                 | TFlux Preprocessor                                                                                                                                                                                                             | 58                                                        |

| Cha | -            | 4:                                                                              |                                                                                                                                                                                                                                | 58                                                        |

| Cha | apter        | <b>4:</b><br>Structu                                                            | TFlux Preprocessor                                                                                                                                                                                                             | <b>58</b><br>59                                           |

| Cha | apter<br>4.1 | <b>4:</b><br>Structu                                                            | TFlux Preprocessor                                                                                                                                                                                                             | <b>58</b><br>59<br>61                                     |

| Cha | apter<br>4.1 | 4:<br>Structu<br>Phases<br>4.2.1                                                | <b>TFlux Preprocessor</b> ure of a TFlux Application Code         s of the TFlux Preprocessor         Phase 1: Parsing                                                                                                         | <b>58</b><br>59<br>61<br>61                               |

| Cha | apter<br>4.1 | 4:<br>Structu<br>Phases<br>4.2.1<br>4.2.2                                       | <b>TFlux Preprocessor</b> ure of a TFlux Application Code         s of the TFlux Preprocessor                                                                                                                                  | <b>58</b><br>59<br>61<br>61<br>63                         |

| Cha | 4.1<br>4.2   | 4:<br>Structu<br>Phases<br>4.2.1<br>4.2.2                                       | TFlux Preprocessor         ure of a TFlux Application Code         s of the TFlux Preprocessor         Phase 1: Parsing         Phase 2: Creation of Output Code                                                               | <b>58</b><br>59<br>61<br>61<br>63<br>64                   |

| Cha | 4.1<br>4.2   | 4:<br>Structu<br>Phases<br>4.2.1<br>4.2.2<br>Basic                              | TFlux Preprocessor         ure of a TFlux Application Code         s of the TFlux Preprocessor         Phase 1: Parsing         Phase 2: Creation of Output Code         TFlux directives                                      | <b>58</b><br>59<br>61<br>61<br>63<br>64<br>64             |

| Cha | 4.1<br>4.2   | 4:<br>Structu<br>Phases<br>4.2.1<br>4.2.2<br>Basic 7<br>4.3.1                   | TFlux Preprocessor         ure of a TFlux Application Code         s of the TFlux Preprocessor         Phase 1: Parsing         Phase 2: Creation of Output Code         TFlux directives         DThreads                     | <b>58</b><br>59<br>61<br>61<br>63<br>64<br>64<br>64       |

| Cha | 4.1<br>4.2   | 4:<br>Structu<br>Phases<br>4.2.1<br>4.2.2<br>Basic 7<br>4.3.1<br>4.3.2<br>4.3.3 | TFlux Preprocessor         ure of a TFlux Application Code         s of the TFlux Preprocessor         Phase 1: Parsing         Phase 2: Creation of Output Code         TFlux directives         DThreads         TFlux Loops | <b>58</b><br>59<br>61<br>61<br>63<br>64<br>64<br>66<br>72 |

## Chapter 5: TFluxHard

|    | 5.1   | The TI | FluxHard System                      | 78  |

|----|-------|--------|--------------------------------------|-----|

|    | 5.2   | TFluxI | Hard Scheduler                       | 79  |

|    |       | 5.2.1  | TFluxHard Scheduler Units            | 80  |

|    |       | 5.2.2  | Implementation of Basic Operations   | 83  |

|    | 5.3   | TFluxI | Hard Scheduler Interface             | 90  |

|    |       | 5.3.1  | Load TSU                             | 90  |

|    |       | 5.3.2  | Clear this TSU                       | 91  |

|    |       | 5.3.3  | Flush Scheduler                      | 92  |

|    |       | 5.3.4  | Thread Completed Execution           |     |

|    | 5.4   | TFluxI | Hard Scheduler Hardware              |     |

|    |       | 5.4.1  | Logic Units                          |     |

|    |       | 5.4.2  | Memory Units                         |     |

|    | 5.5   |        | are Budget Estimation                |     |

|    |       |        |                                      |     |

|    | 5.6   |        | Hard Implementation Issues           |     |

|    |       | 5.6.1  | Current Design                       |     |

|    |       | 5.6.2  | Possible Future Implementations      | 104 |

| Ch | apter | 6:     | TFluxSoft                            | 106 |

|    | 6.1   | SoftSc | heduler                              | 108 |

|    |       | 6.1.1  | Implementation of Basic Operations   | 109 |

|    |       | 6.1.2  | Mutual Exclusion                     | 112 |

|    |       | 6.1.3  | Upper Bound of Basic Operations Cost | 113 |

|    | 6.2   | SoftSc | heduler Design Issues                |     |

|    |       |        |                                      |     |

78

|       | 6.2.1               | Thread to Kernel Indexing (TKI)                                                                                                                                                                                                               | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 6.2.2               | TUB Segmentation                                                                                                                                                                                                                              | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 6.2.3               | Local TUB                                                                                                                                                                                                                                     | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

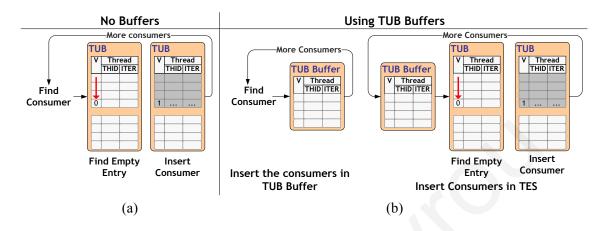

|       | 6.2.4               | TUB Buffers                                                                                                                                                                                                                                   | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 6.2.5               | TUB Ranges                                                                                                                                                                                                                                    | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 6.2.6               | Summary                                                                                                                                                                                                                                       | 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

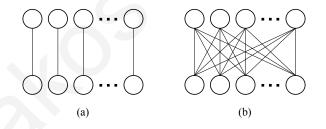

| 6.3   | TFlux               | Soft Scalability Issues                                                                                                                                                                                                                       | 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| apter |                     |                                                                                                                                                                                                                                               | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7.1   |                     |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.2   | Real-li             | ife Applications                                                                                                                                                                                                                              | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

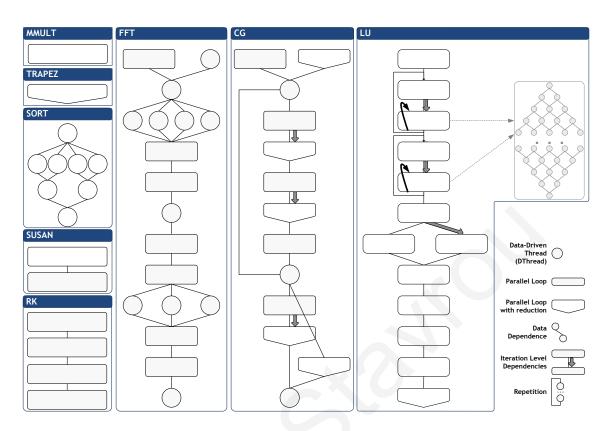

|       | 7.2.1               | Matrix Multiply (MMULT)                                                                                                                                                                                                                       | 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

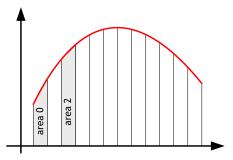

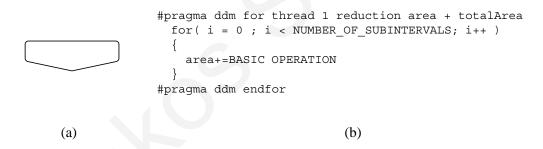

|       | 7.2.2               | Trapezoidal Rule for Integration (TRAPEZ)                                                                                                                                                                                                     | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

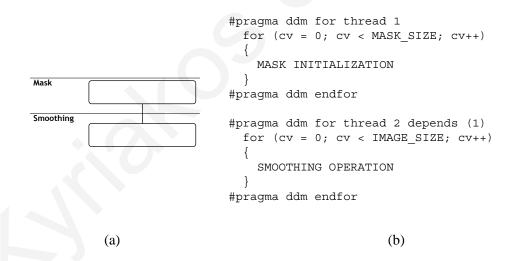

|       | 7.2.3               | Susan Smoothing (SUSAN)                                                                                                                                                                                                                       | 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

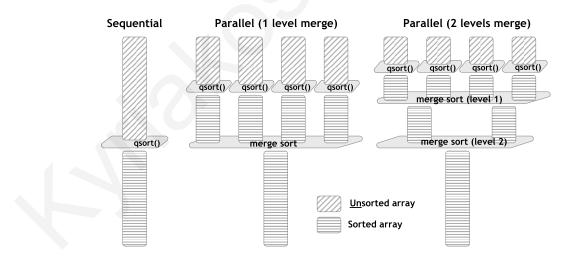

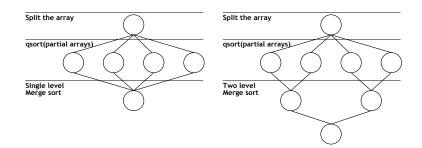

|       | 7.2.4               | Sorting using qSort (SORT)                                                                                                                                                                                                                    | 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 7.2.5               | Runge-Kutta (RK)                                                                                                                                                                                                                              | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

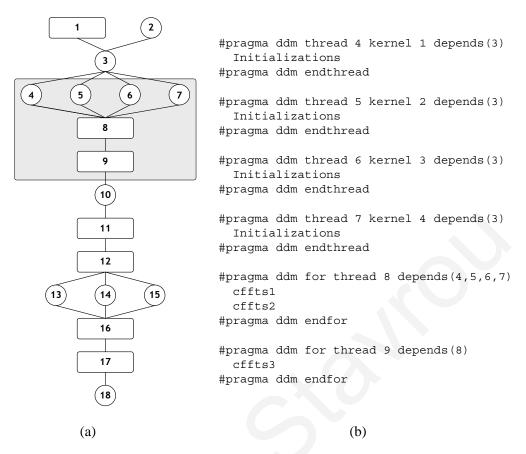

|       | 7.2.6               | Fast Fourier Transformation (FFT)                                                                                                                                                                                                             | 141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 7.2.7               | Conjugate Gradient Method (CG)                                                                                                                                                                                                                | 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 7.2.8               | LU                                                                                                                                                                                                                                            | 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 7.2.9               | Summary                                                                                                                                                                                                                                       | 156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

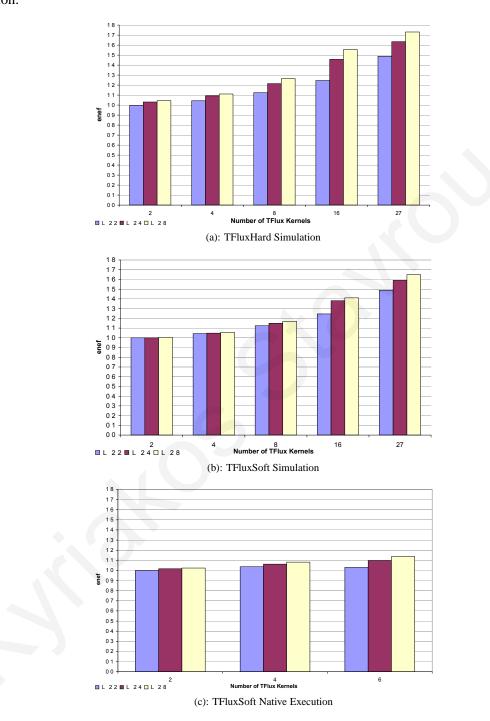

| 7.3   | Synthe              | etic Applications                                                                                                                                                                                                                             | 158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 7.3.1               | Parallel Threads                                                                                                                                                                                                                              | 161                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

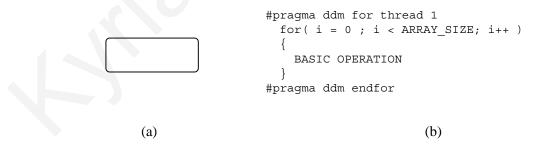

|       | 7.3.2               | Basic Loops                                                                                                                                                                                                                                   | 162                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 7.3.3               | TFlux Advantage of Dataflow Scheduling                                                                                                                                                                                                        | 166                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | apter<br>7.1<br>7.2 | 6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.3 TFlux3<br>apter 7:<br>7.1 Introdu<br>7.2 Real-li<br>7.2.1<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.3 Synthe<br>7.3.1<br>7.3.2 | 6.2.2       TUB Segmentation         6.2.3       Local TUB         6.2.4       TUB Buffers         6.2.5       TUB Ranges         6.2.6       Summary         6.3       TFluxSoft Scalability Issues         apter 7:       TFlux Evaluation Suite         7.1       Introduction         7.2       Real-life Applications         7.2.1       Matrix Multiply (MMULT)         7.2.2       Trapezoidal Rule for Integration (TRAPEZ)         7.2.3       Susan Smoothing (SUSAN)         7.2.4       Sorting using qSort (SORT)         7.2.5       Runge-Kutta (RK)         7.2.6       Fast Fourier Transformation (FFT)         7.2.7       Conjugate Gradient Method (CG)         7.2.8       LU         7.2.9       Summary         7.3       Synthetic Applications         7.3.1       Parallel Threads         7.3.2       Basic Loops |

|         | 7.3.4   | TFluxSoft Scalability Study                         | 171 |

|---------|---------|-----------------------------------------------------|-----|

| Chapter | 8:      | Experimental Setup                                  | 179 |

| 8.1     | Experi  | mentation Infrastructure                            | 179 |

|         | 8.1.1   | Virtutech Simics Full System Simulator              | 180 |

|         | 8.1.2   | TFluxHard Simulation: Modeling the Scheduler        | 181 |

|         | 8.1.3   | Systems used for Performance Evaluation             | 183 |

|         | 8.1.4   | Systems used for Studying Virtualization            | 186 |

|         | 8.1.5   | Summary                                             | 186 |

| 8.2     | Compi   | ilation                                             | 187 |

| 8.3     | Schedu  | uling Policy                                        | 187 |

| 8.4     | Unroll  | ing                                                 | 188 |

| 8.5     | Metric  | ·s                                                  | 188 |

| 8.6     | Collec  | ting Statistics                                     | 189 |

| 8.7     | Statist | ical Significance                                   | 190 |

|         | 0       |                                                     | 101 |

| Chapter | 9:      | Performance Evaluation                              | 191 |

| 9.1     | Minim   | num DThread Size                                    | 191 |

| 9.2     | Real L  | ife Applications                                    | 194 |

|         | 9.2.1   | TFluxHard                                           | 195 |

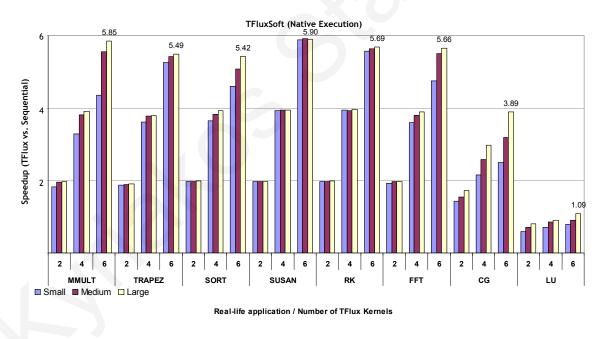

|         | 9.2.2   | TFluxSoft                                           | 204 |

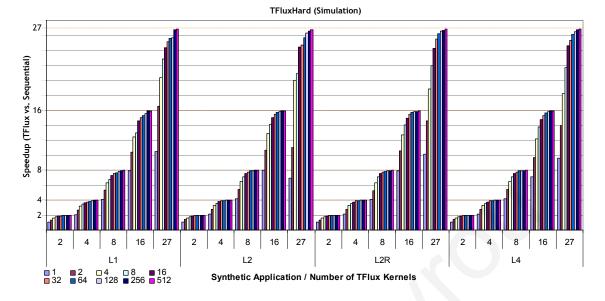

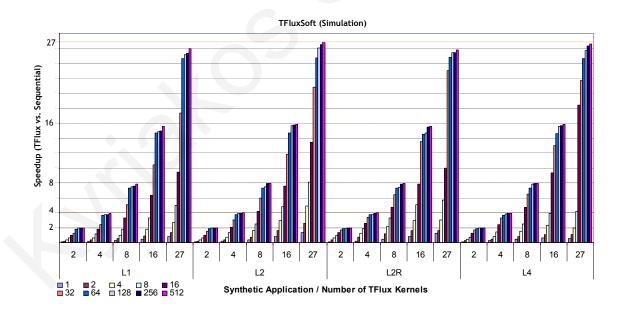

| 9.3     | Synthe  | etic Applications                                   | 206 |

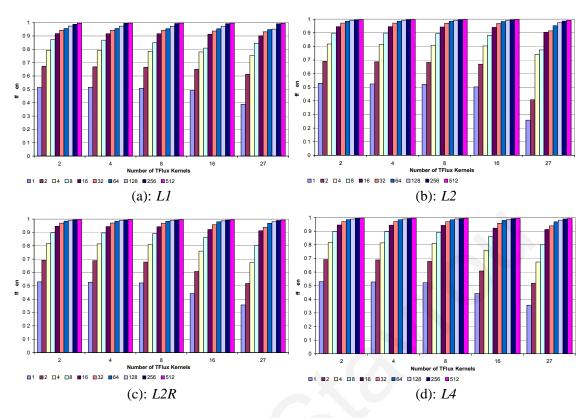

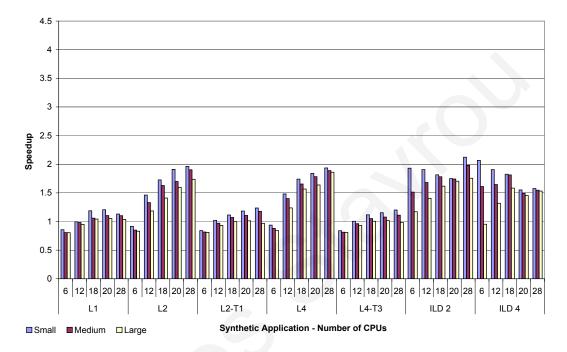

|         | 9.3.1   | TFlux Loops Dependencies                            | 207 |

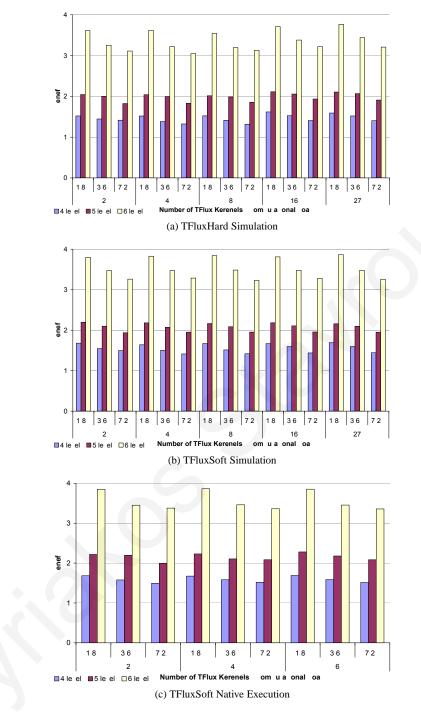

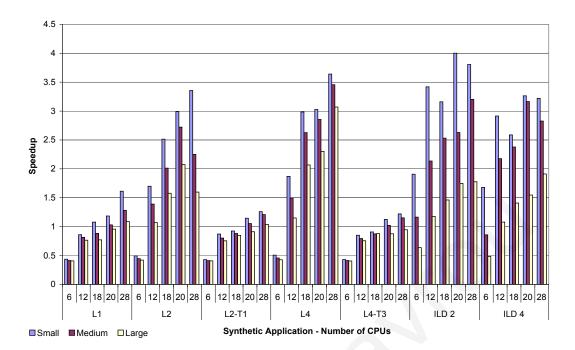

|         | 9.3.2   | Applications with Complex Dataflow Dependencies     | 212 |

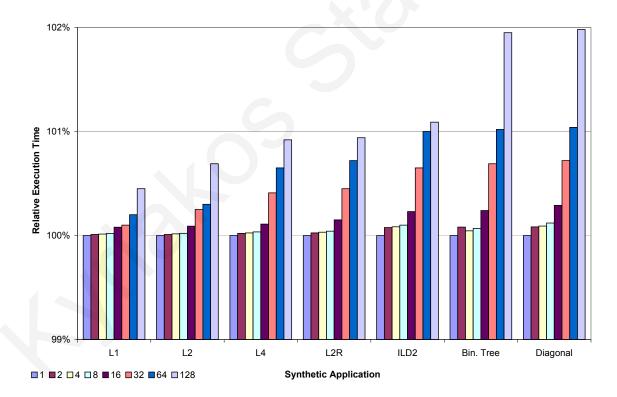

| 9.4     | TFlux   | Soft Scalability - Operation with Multiple Updaters | 218 |

|         | 9.4.1   | Potential of using Multiple Updaters                  | 219 |

|---------|---------|-------------------------------------------------------|-----|

|         | 9.4.2   | Performance Evaluation with Multiple Updaters         | 223 |

| 9.5     | TFluxI  | Hard Scheduler Delay                                  | 225 |

| Chapter | 10:     | Virtualization and Portability                        | 228 |

| 10.1    | TFlux   | Virtualization                                        | 228 |

| 10.2    | TFlux   | Portability                                           | 231 |

|         | 10.2.1  | From TFluxHard to TFluxSoft                           | 231 |

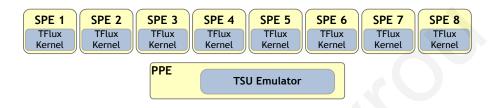

|         | 10.2.2  | TFluxCell                                             | 231 |

|         | 10.2.3  | Execution on Distributed Memory Environments          | 232 |

| Chapter | 11:     | Conclusions and Future Work                           | 235 |

| -       |         | isions                                                | 235 |

|         |         | Work                                                  |     |

|         |         | TFlux Platform                                        |     |

|         |         | TFluxHard                                             |     |

|         |         | TFluxSoft                                             |     |

|         | 11.2.4  | TFlux Preprocessor                                    | 238 |

| Appendi | x A:    | Example of using the interface of TFluxHard-Scheduler | 240 |

|         |         |                                                       |     |

| Appendi | x B:    | TFlux Directives                                      | 246 |

| B.1     | Notatio | ons                                                   | 246 |

| B.2     | Progra  | m Control                                             | 248 |

| B.3     | Variab  | les Declaration                                       | 249 |

| B.4     | Block   | Declaration                                           | 249 |

| B.5 | DThread Dec | laration | <br> | <br> | <br> | <br> | • | <br> |   | <br> | • |   | <br>. 250 |

|-----|-------------|----------|------|------|------|------|---|------|---|------|---|---|-----------|

| B.6 | TFlux Loop  |          | <br> | <br> | <br> | <br> | • | <br> | • | <br> |   | • | <br>. 254 |

258

## Bibliography

Starrow Contraction

# LIST OF TABLES

| 1  | Explanation of the operation of DThreads                                             |

|----|--------------------------------------------------------------------------------------|

| 2  | The API of the TFlux Scheduler                                                       |

| 3  | Examples of TFlux Loops scheduling                                                   |

| 4  | Consumer List usage example                                                          |

| 5  | The configuration of the memory units of TFluxHard Scheduler                         |

| 6  | Access pattern of SoftScheduler units for the Basic Operations                       |

| 7  | Theoretical Upper bound cost for the SoftScheduler Operations                        |

| 8  | Size of the SoftScheduler units. The size of the TUB regards a configuration with 27 |

|    | TFlux Kernels                                                                        |

| 9  | Cache setup for the memory statistics of the TFlux Evaluation Suite                  |

| 10 | Summary of the characteristics of <i>MMULT</i>                                       |

| 11 | Summary of the characteristics of <i>TRAPEZ</i>                                      |

| 12 | Summary of the characteristics of SUSAN                                              |

| 13 | Summary of the characteristics of SORT                                               |

| 14 | Summary of the characteristics of <i>RK</i>                                          |

| 15 | Summary of the characteristics of <i>FFT</i>                                         |

| 16 | Summary of the characteristics of CG                                                 |

| 17 | Summary of the characteristics of <i>LU</i>                                          |

| 18 | Summary of the characteristics of real-life applications                             |

| 19 | Number of dynamic instructions in synthetic applications' computational load 161     |

| 20 | Applications used for the evaluation of execution with multiple Updaters 178         |

| 21 | Memory hierarchy configuration for TFluxSim                                          |

| 22 | Memory hierarchy of Intel Xeon E5320                          | 185 |

|----|---------------------------------------------------------------|-----|

| 23 | Summary of the machines of the experimentation infrastructure | 187 |

| 24 | Machines used for virtualization study                        | 230 |

# LIST OF FIGURES

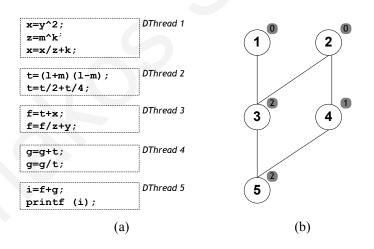

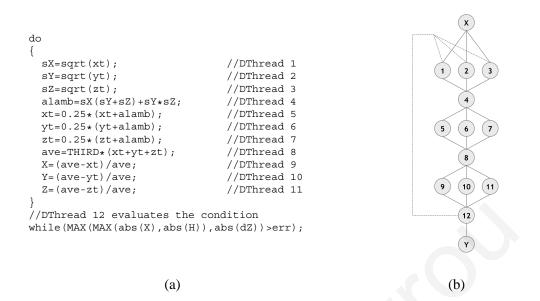

| 1  | Example of a Data-Driven Multithreading program             | 28 |

|----|-------------------------------------------------------------|----|

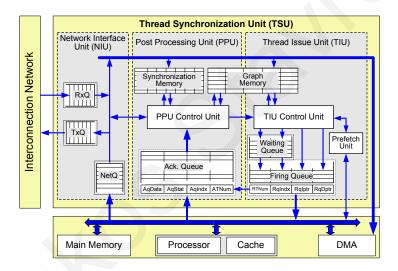

| 2  | The Thread Synchronization Unit (TSU)                       | 29 |

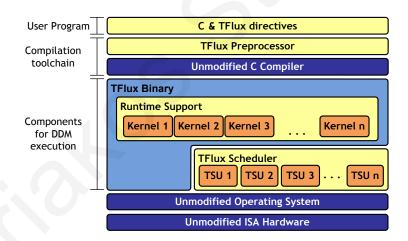

| 3  | The layers of the TFlux Platform                            | 33 |

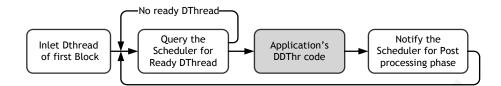

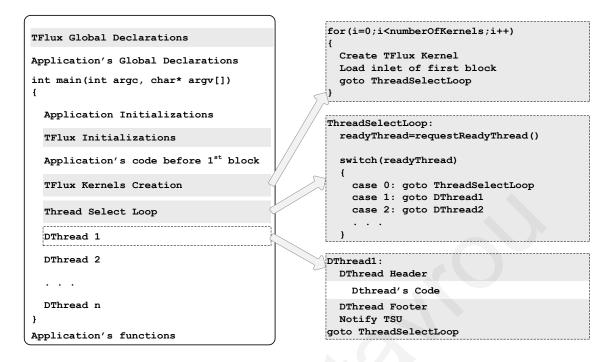

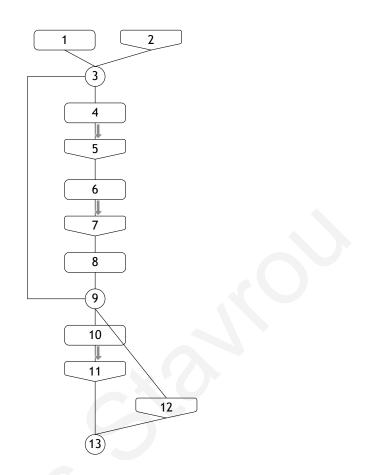

| 4  | Operation of the TFlux Kernel                               | 36 |

| 5  | The TFlux Scheduler                                         | 37 |

| 6  | Explanation of the operation of DThreads                    | 40 |

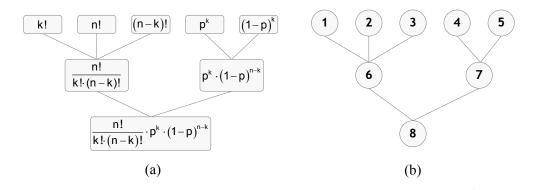

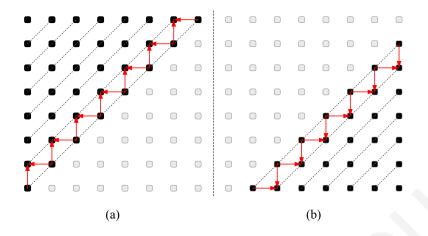

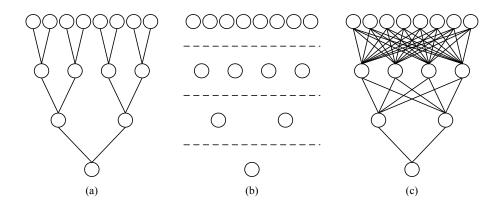

| 7  | Explanation of TFlux Loops: TFlux Loop - DThread dependency | 43 |

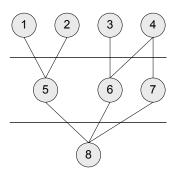

| 8  | Explanation of TFlux Loops: TFlux Loop - TFlux Loop         | 44 |

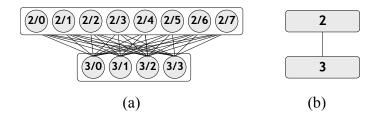

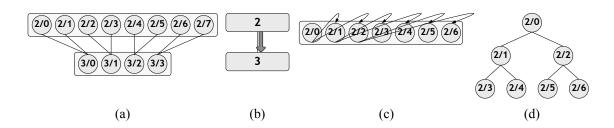

| 9  | Explanation of TFlux Loops: Iteration Level Dependencies    | 45 |

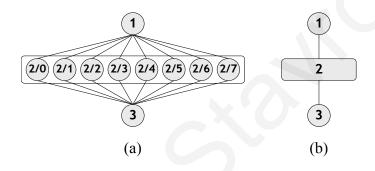

| 10 | Execution of TFlux Loops                                    | 45 |

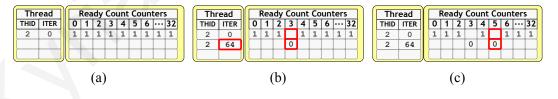

| 11 | Execution of TFlux Loops with large number of iterations    | 47 |

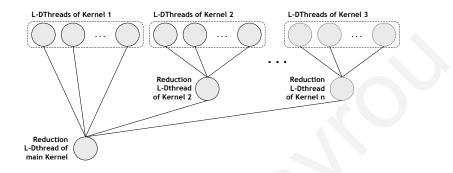

| 12 | Example of TFlux Loop that performs a reduction operation   | 50 |

| 13 | Execution of Reduction TFlux Loops                          | 50 |

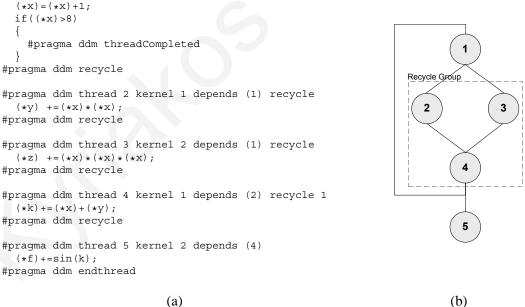

| 14 | Thread Recycling                                            | 51 |

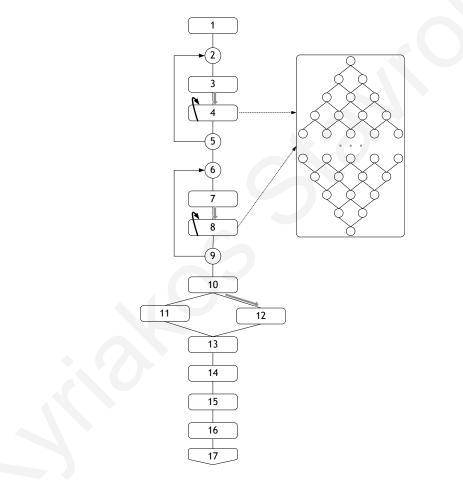

| 15 | The structure of TFlux programs                             | 60 |

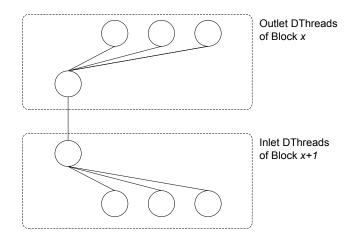

| 16 | Inlet/Outlet Synchronization                                | 63 |

| 17 | TFlux directives: DThread declaration                       | 65 |

| 18 | TFlux directives: <i>import/export</i> statements           | 65 |

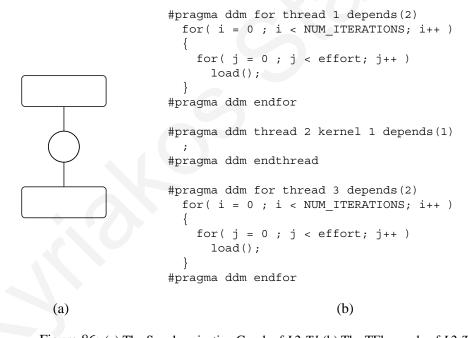

| 19 | TFlux directives: <i>depends</i> statement                  | 65 |

| 20 | TFlux directives: kernel all statement                      | 66 |

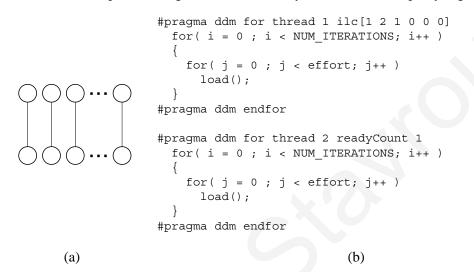

| 21 | TFlux directives: TFlux Loop declaration                    | 66 |

| 22 | TFlux directives: The <i>schedule 1</i> statement           | 68 |

| 23 | TFlux directives: TFlux Loop with unrolling                                         | 69  |

|----|-------------------------------------------------------------------------------------|-----|

| 24 | TFlux directives: TFlux Loop with reduction                                         | 69  |

| 25 | TFlux directives: TFlux Loop with reduction using a custom function                 | 70  |

| 26 | TFlux directives: TFlux Loop dependencies                                           | 71  |

| 27 | TFlux directives: TFlux Loops with Iteration Level Dependencies                     | 71  |

| 28 | TFlux directives: Thread Recycling                                                  | 72  |

| 29 | TFlux directives expressibility: Example program                                    | 74  |

| 30 | TFlux directives expressibility: Code of the example program                        | 75  |

| 31 | TFlux directives expressibility: Example with iteration level dependencies          | 75  |

| 32 | TFlux directives expressibility: Code of the iteration level dependencies example . | 76  |

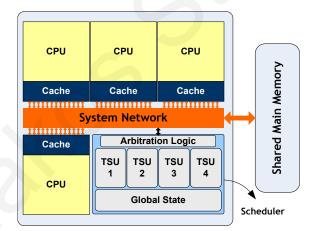

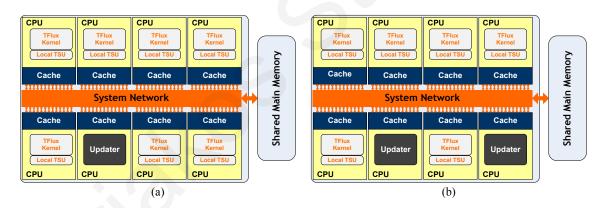

| 33 | Abstract TFluxHard configuration with 4 cores                                       | 79  |

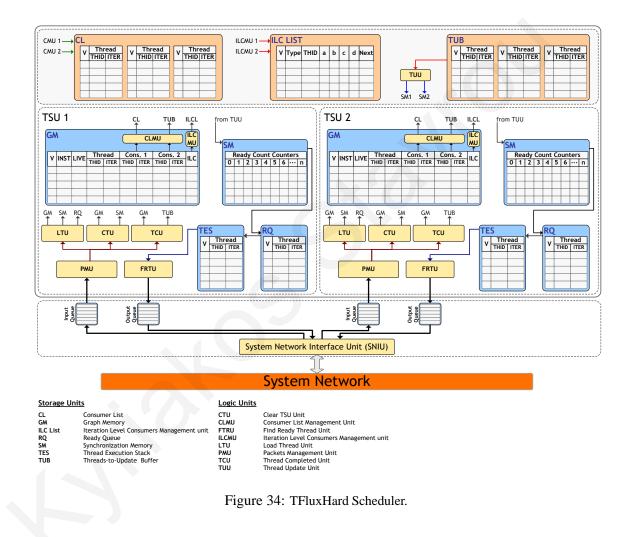

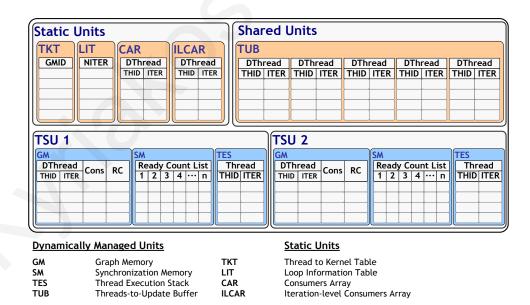

| 34 | TFluxHard Scheduler                                                                 | 80  |

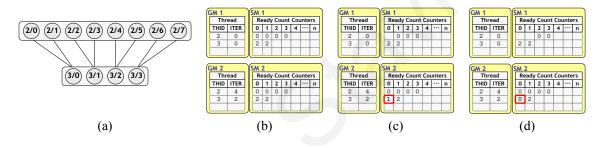

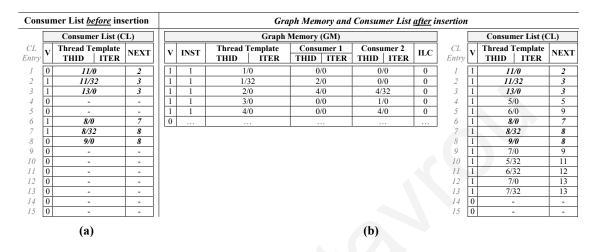

| 35 | Example of Thread Loading                                                           | 84  |

| 36 | Consumer List usage example                                                         | 86  |

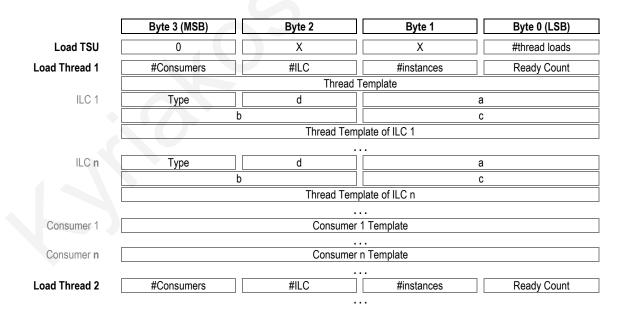

| 37 | TFluxHard Scheduler Interface for <i>Load TSU</i>                                   | 90  |

| 38 | TFluxHard Scheduler Interface for <i>Clear TSU</i>                                  | 91  |

| 39 | TFluxHard Scheduler Interface for <i>Flush Scheduler</i>                            | 92  |

| 40 | TFluxHard Scheduler Interface for <i>Execution Completion</i>                       | 92  |

| 41 | TFluxHard Scheduler Interface for <i>L-DThread Recycle</i>                          | 93  |

| 42 | TFluxHard Scheduler Interface for <i>Recycle Execution</i>                          | 93  |

| 43 | TFluxSoft multicore                                                                 | 107 |

| 44 | SoftScheduler                                                                       | 108 |

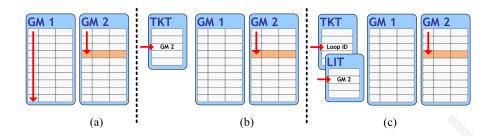

| 45 | Thread to Kernel Indexing (TKI)                                                     | 119 |

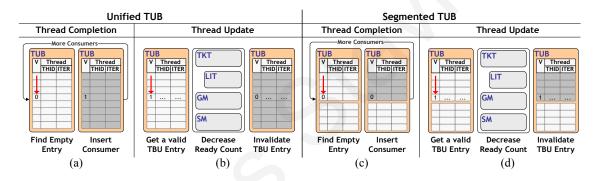

| 46 | TUB Segmentation                                                                    | 120 |

| 47 | TUB Buffers                                                                   |

|----|-------------------------------------------------------------------------------|

| 48 | Operation of <i>MMULT</i>                                                     |

| 49 | Real-life applications: MMULT                                                 |

| 50 | Operation of the parallel version of TRAPEZ                                   |

| 51 | Real-life applications: TRAPEZ                                                |

| 52 | Real-life applications: SUSAN                                                 |

| 53 | Operation of the parallel version of <i>SORT</i>                              |

| 54 | Real-life applications: SORT - Synchronization Graph                          |

| 55 | Real-life applications: SORT - TFlux Code                                     |

| 56 | Real-life applications: RK                                                    |

| 57 | Real-life applications: FFT                                                   |

| 58 | Real-life applications: CG - Synchronization Graph                            |

| 59 | Real-life applications: CG - TFlux Code                                       |

| 60 | Details of the code of $CG$                                                   |

| 61 | Real-life applications: CG with iteration level dependencies - TFlux Code 151 |

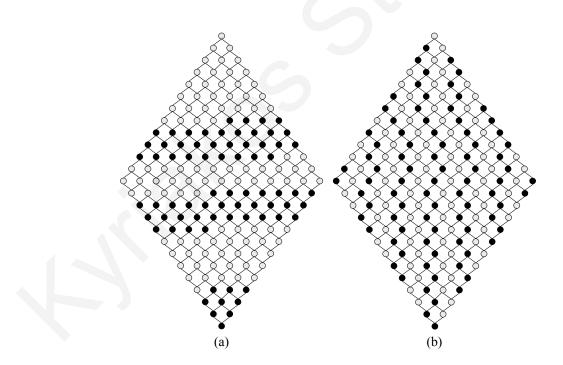

| 62 | Dependencies of the critical loops of $LU$                                    |

| 63 | The Synchronization Graph of LU                                               |

| 64 | Details of the code of $LU$                                                   |

| 65 | Scheduling for LU                                                             |

| 66 | Synchronization Graphs of the real-life applications                          |

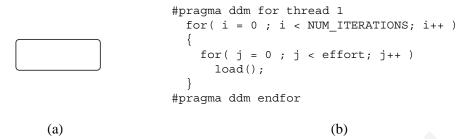

| 67 | Computational load for synthetic the applications                             |

| 68 | The <i>load()</i> function used for synthetic applications                    |

| 69 | Synthetic applications: Parallel Threads                                      |

| 70 | Synthetic applications: Baseline for <i>Parallel Threads</i>                  |

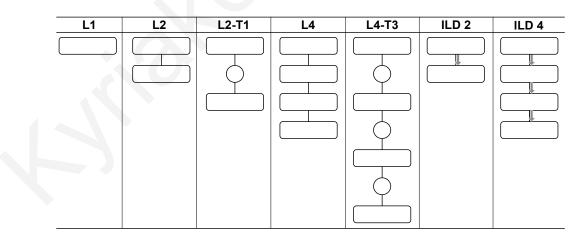

| 71 | Synthetic applications: L1                                                                                                                                                                 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 72 | Synthetic applications: Baseline for $L1$                                                                                                                                                  |

| 73 | Synthetic applications: L2                                                                                                                                                                 |

| 74 | Synthetic applications: Baseline for <i>L</i> 2                                                                                                                                            |

| 75 | Synthetic applications: L4                                                                                                                                                                 |

| 76 | Synthetic applications: Baseline for <i>L</i> 4                                                                                                                                            |

| 77 | Synthetic applications: L2R                                                                                                                                                                |

| 78 | Synthetic applications: Baseline for <i>L2R</i>                                                                                                                                            |

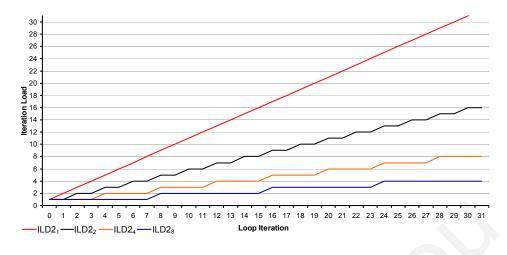

| 79 | The load executed by the $ILD2_x$ synthetic application                                                                                                                                    |

| 80 | The $ILD2_x$ synthetic application and its baseline $\ldots \ldots \ldots$ |

| 81 | Synthetic applications: the code of the TFlux and baseline versions for $ILD_x^2$ 169                                                                                                      |

| 82 | The BINARY TREE synthetic application and its baseline                                                                                                                                     |

| 83 | Synthetic applications: the code of the TFlux and baseline versions for $ILD_x^2$ 171                                                                                                      |

| 84 | Synthetic applications: ILD4                                                                                                                                                               |

| 85 | The baseline for the <i>DIAGONAL</i> synthetic application                                                                                                                                 |

| 86 | Synthetic applications: L2-T1                                                                                                                                                              |

| 87 | Synthetic applications: L4-T3                                                                                                                                                              |

| 88 | Synthetic applications: ILD2                                                                                                                                                               |

| 89 | Synthetic applications: ILD4                                                                                                                                                               |

| 90 | Synthetic applications used to study the potential of using multiple Updaters 176                                                                                                          |

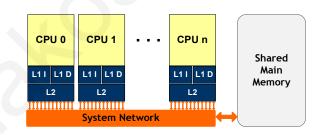

| 91 | Conceptual view of the generic simulated machine                                                                                                                                           |

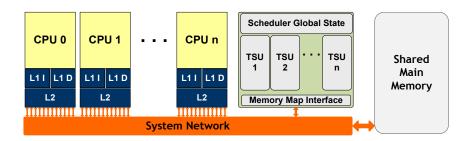

| 92 | Conceptual view of the TFluxHardSim simulator                                                                                                                                              |

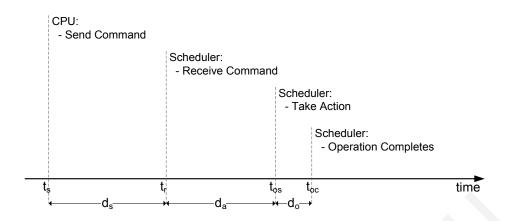

| 93 | Timing of executing Scheduler operations for TFluxHard                                                                                                                                     |

| 94 | Conceptual view of the TFluxHardSim simulator                                                                                                                                              |

| 95  | Quantification of the minimum DThread size for TFluxHard                            |

|-----|-------------------------------------------------------------------------------------|

| 96  | Quantification of the minimum DThread size for TFluxSoft                            |

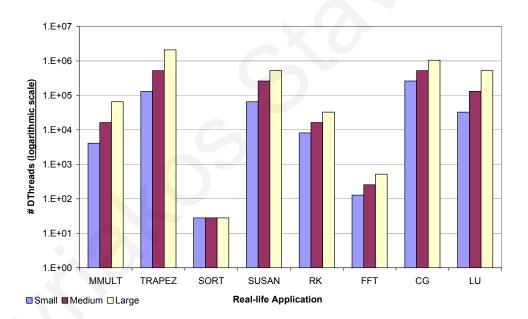

| 97  | Number of DThread for the real-life applications                                    |

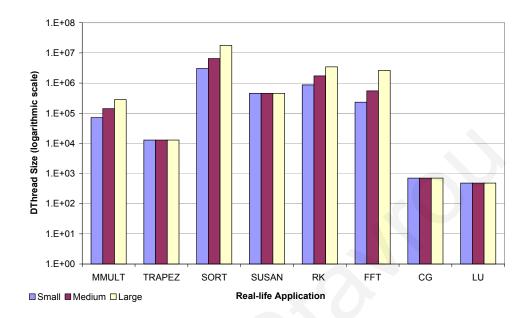

| 98  | DThread sizes for the real-life applications                                        |

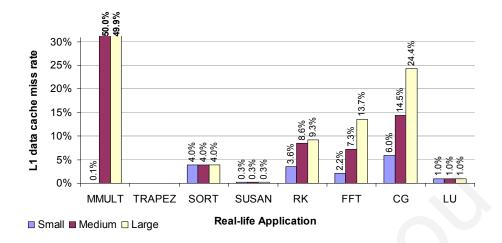

| 99  | L1-data cache miss rate for the real-life applications                              |

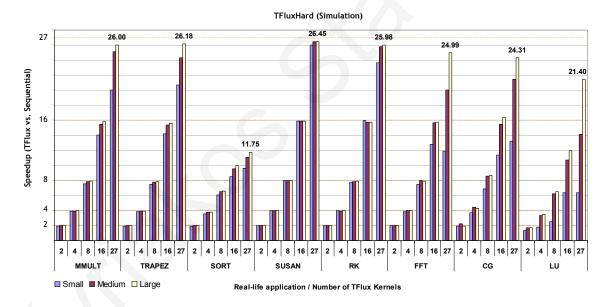

| 100 | TFluxHard performance for the real-life applications                                |

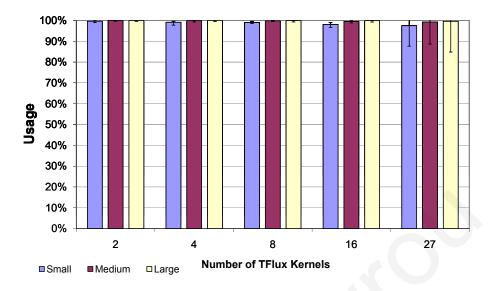

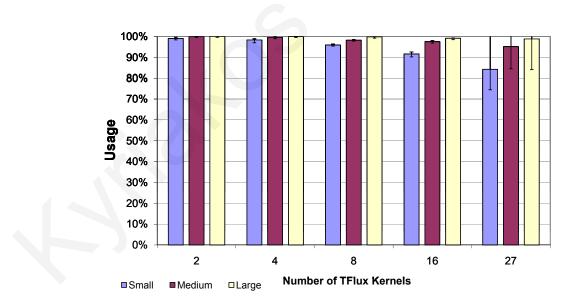

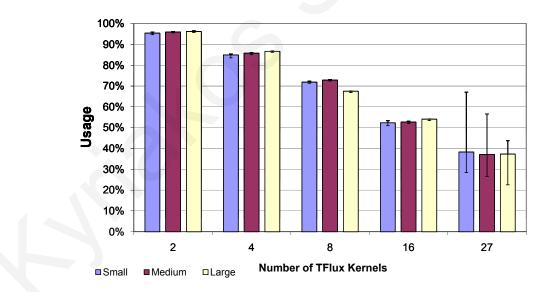

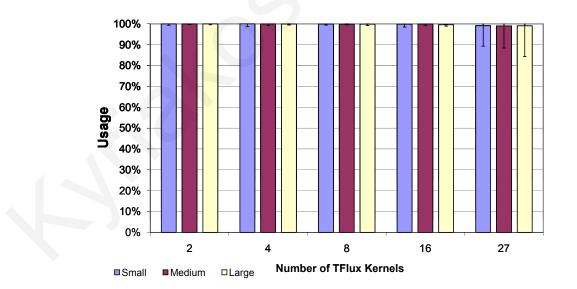

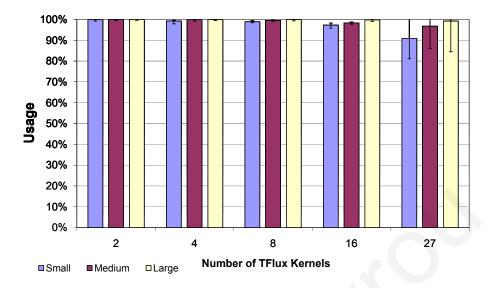

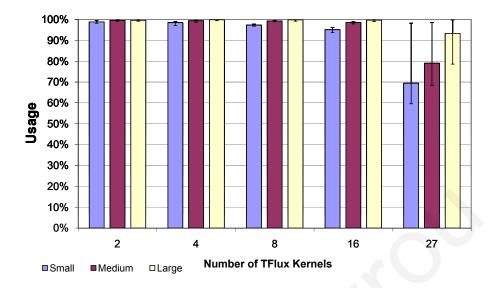

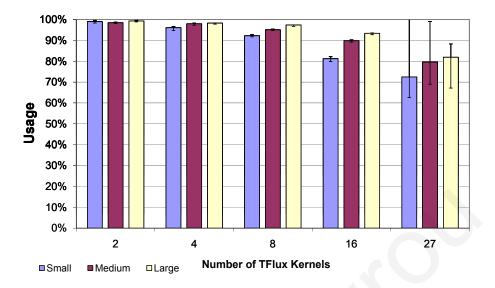

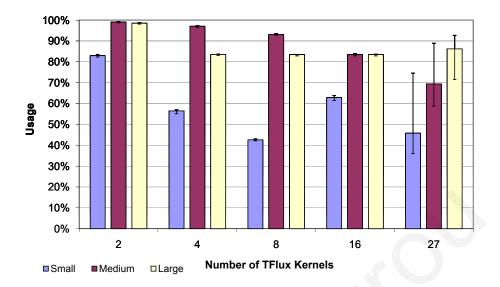

| 101 | TFlux Kernels usage for MMULT                                                       |

| 102 | TFlux Kernels usage for TRAPEZ                                                      |

| 103 | TFlux Kernels usage for QSORT                                                       |

| 104 | TFlux Kernels usage for SUSAN                                                       |

| 105 | TFlux Kernels usage for <i>RK</i>                                                   |

| 106 | TFlux Kernels usage for FFT                                                         |

| 107 | TFlux Kernels usage for CG                                                          |

| 108 | TFlux Kernels usage for LU                                                          |

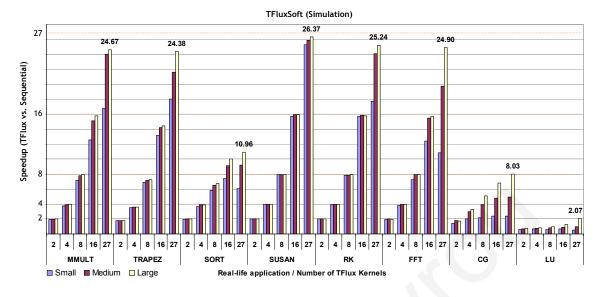

| 109 | TFluxSoft performance for the real-life applications (simulation results) 207       |

| 110 | TFluxSoft performance for the real-life applications (native execution results) 207 |

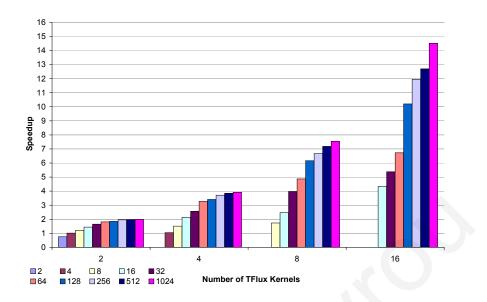

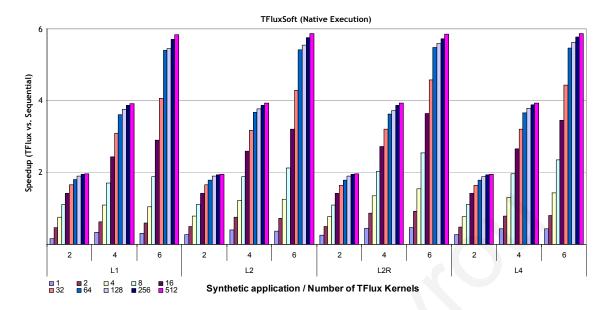

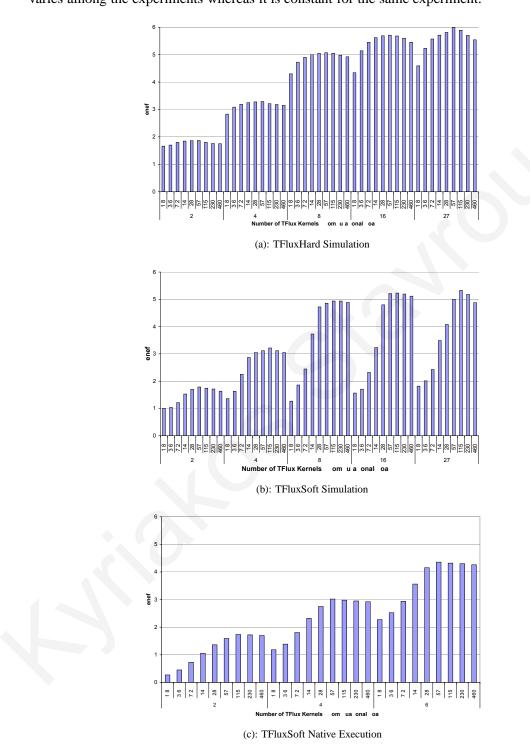

| 111 | TFluxHard performance for the synthetic applications with TFlux Loops 209           |

| 112 | TFluxHard efficiency for the synthetic applications with TFlux Loops                |

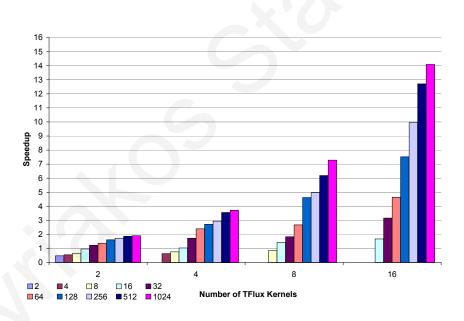

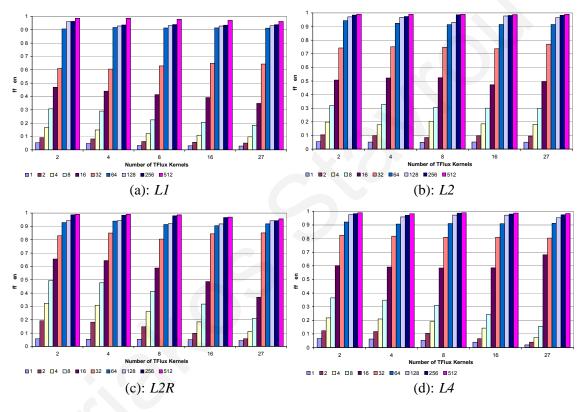

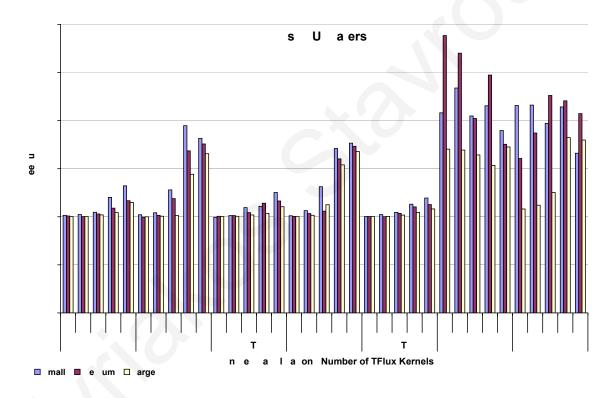

| 113 | TFluxSoft performance for L1, L2, L2R and L4 (simulation results)                   |

| 114 | TFluxSoft efficiency for the synthetic applications with TFlux Loops                |

| 115 | TFluxSoft performance for L1, L2, L2R and L4 (native execution results) 212         |

| 116 | TFlux performance for $ILD2_x$                                                      |

| 117 | TFlux performance for BINARY TREE                                                   |

| 118 | TFlux performance for DIAGONAL                                                      |

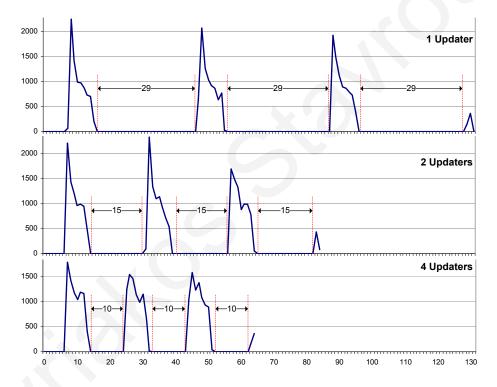

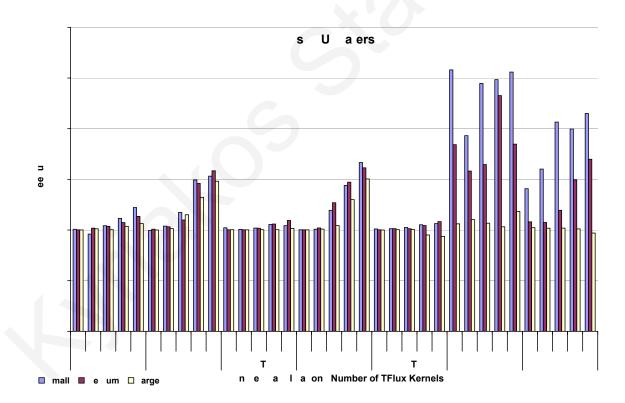

| 119 | Potential performance benefit of using 2 Updaters                          |

|-----|----------------------------------------------------------------------------|

| 120 | Update-requests for execution with different number of Udpaters            |

| 121 | Potential performance benefit of using 2 Updaters                          |

| 122 | Performance comparison of system with 2 versus a system with 1 Updater 224 |

| 123 | Performance comparison of system with 4 versus a system with 1 Updater 225 |

| 124 | TFluxHard performance for the real-life applications                       |

| 125 | The implementation of TFlux on the Cell/BE processor                       |

| 126 | Performance of TFluxCell                                                   |

| 127 | TFluxHard Scheduler Interface Example Program                              |

|     |                                                                            |

# **Chapter 1**

# Introduction

It is a known fact that traditional techniques used to improve microprocessor performance have lead to diminishing returns. Such techniques include, among others, packing more transistors into the same chip [76], clocking the chips at higher frequencies [1, 82], the introduction of on-chip caches [48], exploitation of Instruction Level Parallelism [10, 110, 111, 119], speculation [66, 65, 107, 109] and prefetching [106]. The main reasons that limited the performance improvement delivered by these techniques are twofold. On the one hand the complexity of the design and the power consumed have reached such high levels, that make the extension of the above techniques unfeasible [11, 19, 80]. On the other hand, the performance increase that these techniques could deliver has, to a large extent, already been exploited [1, 11, 19].

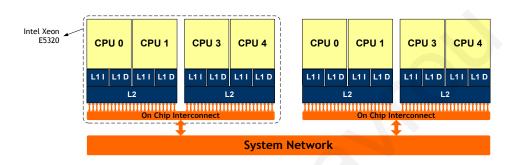

To overcome these limitations, the CPUs have entered a new era, that of the *multicore* chips. These processors consist of a number of interconnected cores on the same die. These cores are usually simpler than the traditional monolithic designs leading to lower complexity designs and more power efficient systems. Currently, all major manufacturers have multicore products in the market. Examples include Sun's T1 and T2 (Niagara) that support up to 64 hardware threads, IBM's Cell/BE [56] with 8+1 cores, Intel's Xeon 7400 with 6 cores, Intel's Quad Core [51] with 4 cores, and AMD's Opteron [2] with also 4 cores. Moreover, more ambitious designs like the Intel Teraflops chip [50] with 80 cores and the IBM Cyclops-64 (C64) [31] with 160 cores, are under development.

There are two major ways to explore the parallelism offered by the multicore processors: "throughput" and "concurrency". Throughput refers to executing multiple independent applications on the system, one on each of its cores. Although this approach can keep the resources busy it is unable to improve the performance of each particular instance of an application. Moreover, it is not likely that users will have as many compute intensive tasks as the number of on-chip cores especially when this number of cores increases. On the other hand, "Concurrency" is the approach that has been traditionally used for the execution of compute intensive applications. In particular, the target of the "Concurrency" approach, is to split a single program into parallel entities, which are to be executed by different computation nodes. The main objective is to decrease the execution time of the application. If enough parallelism from the application is exposed to the hardware, it is possible to utilize the available resources, therefore decreasing the application's execution time as much as possible. While throughput is easily exploited in current small-scale multicore processors, the support for efficient concurrency will be the key issue to exploit the parallelism for the future large-scale multicore processors.

In addition to the parallel hardware, the key components for exploiting concurrency are the *execution model*, which allows the application to utilize multiple processors for its execution and the *programming model* in order for the programmers to develop such applications. An execution model appropriate for multicore processors must be a good match to the particular characteristics of the architecture. It must provide an efficient scheduling of the concurrent tasks, and at the same

time hide the details of the underlying system providing to the user and programmer a virtualized environment. This *virtualization* allows for programs to be developed without a particular system as target.

The programmability of a parallel system is another major issue. Although numerous research projects have focused in the past on building fully automated parallelizing compilers, such as Polaris [18], SUIF [128], Parafrase [41] and NCI [77], none of them is widely used today. In contrast, programmers use semi-automated solutions like the compiler directives of OpenMP [81] or the libraries for MPI [74] or pthreads [21]. This semi-automated approach is what seems to be the programming solution to be followed for the multicores architecture [11, 19]. To achieve high performance the programming model should enable the programmer to express a high degree of parallelism at a fine-grained level. In addition, this model should not require the programmer to develop applications with a particular machine configuration in mind.

According to the previous discussion, the main characteristics that a platform must have in order to allow for the applications to efficiently exploit the parallelism offered by a large-scale multicore are the following:

- Virtualization: The platform must offer to its user and programmer a virtualized environment that hides the details of the underlying system both at the hardware and software level. Consequently, programs do not need to be developed for a specific machine configuration. Instead, programmers must be able to develop and execute on all implementations of the proposed platform.

- **Performance:** It is required for the proposed platform to be able to achieve high levels of performance even for non explicitly parallel applications. In order to achieve this, the parallelization overheads incurred must be kept at minimum levels.

- **Scalability:** The performance of the proposed platform must scale to multicore systems with larger number of cores. In order to achieve this, the parallelism exposed by the model must not be limited in any way by the number of execution units.

- **Portability:** The proposed platform must require minimum effort for it to be ported to a new system. The system-specific code must be limited to only a small number of components of the proposed platform.

- **Programmability:** Programs for such a platform are to be developed using a fully- or semiautomated parallelization approach, *i.e.* with the use of a parallelizing compiler or by augmenting sequential code with special compiler directives. The programming model must allow the programmer to express any parallel construct in an intuitive way.

## 1.1 The TFlux Parallel Processing Platform

This work presents the *Thread Flux (TFlux)* Parallel Processing Platform, a parallel execution system that aims to deliver high performance on *commodity* multicore systems. *TFlux* is a complete system, from the hardware to the programming toolchain and includes a number of key components that allow it to meet the targets set for a successful parallel processing platform.

*TFlux* achieves high performance and scalability mainly due to its scheduling policy that follows the Data-Driven Multithreading (DDM) model of execution. This dataflow-like scheduling policy enables *TFlux* to exploit more parallelism compared to other models that enforce synchronization using barriers and locks. The careful design of the several components of *TFlux* reduce the parallelization overheads in a way that allows for applications with fine-grained parallel segments to scale well on systems with a large number of processing elements. It is a main goal of *TFlux* to provide dataflow-like scheduling to *commodity* systems. By using *commodity components TFlux* not only widens its impact but also is able to benefit from the improvements introduced in those components. In order to achieve its goal, *TFlux* follows a layered design. The top layer, which is the one programmers use to develop TFlux applications, abstracts all details of the underlying machine. TFlux applications are developed using ANSI-C together with TFlux compiler directives. The TFlux compiler directives are used to express the code of the parallel segments and the dependencies among those segments. The code of the TFlux program passes through the TFlux Preprocessor that outputs a C program, which may be compiled by a *commodity* C compiler resulting in an executable binary. The binary invokes the operations of the TFlux Runtime Support allowing execution under TFlux. The Runtime Support runs on top of an *unmodified* Unix-based Operating System and hides all TFlux specific details such as the particular implementation of the TFlux Thread Scheduler. More details about the purpose, design and operation of the different layers of TFlux will be given in Chapter 3 that focuses on the presentation of the TFlux Platform. As for the TFlux directives and the TFlux Preprocessor they are presented in Chapter 4.

This work presents two incarnations of TFlux: *TFluxHard* and *TFluxSoft*. The key component that differentiates these two incarnations is the TFlux Thread Scheduler. In particular, whereas for *TFluxHard* the functionality of the Scheduler is provided by a hardware unit, for *TFluxSoft* this functionality is provided at the software level. As such, although *TFluxHard* uses only commodity components, it requires the system to be augmented with extra hardware. *TFluxSoft* on the other hand is directly applicable to *off-the-shelf* multiprocessor systems. The details of these two systems are presented in Chapter 5 for *TFluxHard* and in Chapter 6 for *TFluxSoft*.

The key component of TFlux is its ability to provide the dataflow model of execution to its programmer. As such, evaluation of the platform needs to be made with a representative collection