## DEPARTMENT OF COMPUTER SCIENCE

# Task Data-flow Execution on Many-core Systems

Andreas Diavastos

A Dissertation Submitted to the University of Cyprus in Partial

Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

© Andreas Diavastos, 2017

#### **VALIDATION PAGE**

Committee Member:

**Doctoral Candidate:** Andreas Diavastos **Doctoral Dissertation Title:** Task Data-flow Execution on Many-core Systems The present Doctoral Dissertation was submitted in partial fulfillment of the requirements for the Degree of Doctor of Philosophy at the Department of Computer Science and was approved on the November 13, 2017 by the members of the Examination Committee. **Examination Committee:** Research Supervisor: Associate Professor Pedro Trancoso Committee Member: Professor Paraskevas Evripidou Committee Member: Associate Professor Yanos Sazeides Committee Member: Professor Leonel Sousa

Professor Dionisios N. Pnevmatikatos

# **DECLARATION OF DOCTORAL CANDIDATE**

| The present Doctoral Dissertation was submitted in partial fulfillment of the requirements     |

|------------------------------------------------------------------------------------------------|

| for the degree of Doctor of Philosophy of the University of Cyprus. It is a product of origina |

| work of my own, unless otherwise mentioned through references, notes, or any other state-      |

| ments.                                                                                         |

|                                                                                                |

| [Full Name of Doctoral Candidate]                                                              |

|                                                                                                |

| [Signature of Doctoral Candidate]                                                              |

# Περίληψη

Η αύξηση της επίδοσης με ταυτόχρονη μείωση της κατανάλωσης ενέργειας επιτυγχάνεται με την παράλληλη επεξεργασία. Προκειμένου να αξιοποιηθεί ο παραλληλισμός μέσα από τις εφαρμογές και να βελτιστοποιηθεί η ενεργειακή απόδοση μεγάλων συστημάτων, η τάση είναι να αυξάνωνται οι πυρήνες μέσα στους επεξεργαστές. Ωστόσο, η αύξηση του αριθμού των πυρήνων από μόνη της δεν έχει ως αποτέλεσμα την βελτιωμένη επίδοση των εφαρμογών. Από την άποψη του λογισμικού, αυτό δημιουργεί νέες προκλήσεις καθώς χρειαζόμαστε ένα πλαίσιο που να μπορεί να εκμεταλλεύεται αποτελεσματικά τον παραλληλισμό των εφαρμογών στους διαθέσιμους πόρους που προσφέρει το υλικού.

Η αύξηση της επίδοσης στα μελλοντικά συστήματα πολλαπλών πυρήνων θα επηρεαστεί από τους ακόλουθους παράγοντες: τον βαθμό παραλληλισμού στις εφαρμογές, τον τρόπο προγραμματισμού, τα χαμηλού κόστους συστήματα εκτέλεσης, την εκτέλεση των εργασιών με γνώμονα την τοποθεσία των δεδομένων, την αποτελεσματική χρήση των διαθέσιμων πόρων και τα επεκτάσιμα σχέδια αρχιτεκτονικής επεξεργαστών.

Σε αυτήν την Διατριβή, το μοντέλο εργασιών (Task model) χρησιμοποιείται ως υλοποίηση του μοντέλου ροής δεδομένων (Data-flow). Το μοντέλο ροης δεδομένων είναι το καταλληλότερο μοντέλο για την εκμετάλλευση μεγάλων ποσοτήτων παραλληλισμού, ενώ η υλοποίηση με τη χρήση εργασιών μειώνει το κόστος της εκτέλεσης και προσαρμόζεται εύκολα σε διαφορετικές εφαρμογές. Σε αυτή τη εργασία, η Συναλλακτική Μνήμη (Transactional Memory) ενσωματώνεται στο μοντελο ροής δεδομένων για να μειώσει την αυστηρότητα του, διερευνώντας τον εικαστικό παραλληλισμό όταν οι εξαρτήσεις μεταξύ εργασίων είναι πολύ περίπλοκες για να εφαρμοστούν ή ακόμα και όταν δεν ισχύουν.

Αυτή η Διατριβή παρουσιάζει την πρώτη εφαρμογή σε μεγάλους πολυ-επεξεργαστές

του μοντέλου πολλαπλών σπειρωμάτων (DDM), μια υλοποίηση του μοντέλου ροής δεδομένων. Το μοντελο πολλαπλών σπειρωμάτων επανασχεδιάζεται για να υποστηρίξει τον πρώτο επεξεργαστή πολλαπλών πυρήνων από την Intel(Single-chip Cloud Computer) που παρέχει ένα ενιαίο χώρο διευθύνσεων χωρίς υποστήριξη υλικού για συνεκτικότητα της κρυφής μνήμης (cache). Τα αποτελέσματα αυτής της εργασίας οδήγησαν στο σχεδιασμό και την ανάπτυξη ενός νέου πιο αποδοτικού, συστήματος εκτέλεσης που μπορεί να επεκταθεί σε ακόμα μεγαλύτερους επεξεργαστές.

Το προτεινόμενο σύστημα (SWITCHES) περιλαμβάνεται σε μια πλατφόμρα προγραμματισμού και εκτέλεσης εφαρμογών. Το SWITCHES είναι λογισμικό που υλοποιεί το μοντέλο ροής δεδομένων που βασίζεται σε εργασίες για επεξεργαστές πολλών πυρήνων. Απαιτεί ενιάιο χώρο διευθύνσεων αλλά όχι απαραίτητα μηχανισμούς συνεκτικότητας της κρυφής μνήμης που θα μπορούσαν να περιορίσουν την επεκτασιμότητα του επεξεργαστή. Το SWITCHES υλοποιεί ένα ελαφρύ στατικό κατανεμημένο σύστημα ενεργοποίησης για την επίλυση εξαρτήσεων κατά τη διάρκεια εκτέλεσης εργασιών. Υποστηρίζει μηχανισμούς κατανομής των πόρων του συστήματος και ενσωματώνει τεχνικές εκμάθησης μηχανών (machine-learning) για την αποτελεσματική αξιοποίηση τους. Για τη εύκολη υλοποίηση προγραμμάτων, το πλαίσιο υλοποιεί το πιο πρόσφατο πρότυπο από το (OpenMP) (ν4.5) και το επεκτείνει για να υποστηρίζει εργασίες σε βρόχους με εξαρτήσεις σε διαφορετικούς βρόχους. Παρέχει ένα εργαλείο (Translator) που παράγει αυτόματα κώδικα βασισμένο σε νήματα, ο οποίος μπορεί να μεταγλωττιστεί από οποιονδήποτε μεταγλωττιστή C/C++, εφαρμόζοντας όλες τις υπάρχουσες βελτιστοποιήσεις.

Χρησιμοποιώντας το σύστημα αυτό, η επίδοση εφαρμογών με διαφορετικά χαρακτηριστικα σε μια μηχανή με Intel Xeon Phi επεξεργαστή ξεπερνά την επίδοση του OpenMP κατά μέσο όρο κατά 32% και βελτιώνει την αποδοτικότητα της πετυχαίνωντας μέγιστη επίδοση χρησιμοποιώντας 30% λιγότερους πυρήνες σε εφαρμογές με σύνθετες εξαρτήσεις.

#### **Abstract**

Power-performance efficiency in High Performance Computing (HPC) systems is currently achieved by exploring parallel processing. Consequently, in order to exploit application parallelism and optimize energy efficiency, the trend is to include more cores in the processors. From the hardware perspective, many small and simple cores will be added in processor architectures, leading towards many-core chips with hundreds of cores. Nevertheless, scaling the number of cores alone does not result in improved application performance. From the software perspective, this creates new challenges as we need a framework that can efficiently exploit application parallelism on the available hardware resources.

Overall, performance scalability in future many-core systems will be affected by the following factors: the degree of parallelism, programmability, low-overhead runtime systems, locality-aware execution, efficient use of the available resources and scalable architecture designs.

In this thesis, the Task model is used as an implementation of the Data-flow paradigm. Data-flow is the most appropriate model for exploiting large amounts of software parallelism, while a task-based implementation reduces runtime overheads and easily adapts to different applications. In this work, Transactional Memory is integrated in Data-flow to reduce the strictness of the latter by exploring speculative parallelism when task dependences are too complex to apply or even when not applicable.

This thesis presents the first many-core implementation of the Data-Driven Multi-threading (DDM) model, a task-based implementation of Data-flow. DDM

is redesigned to support the first single-chip many-core processor from Intel (the Single-chip Cloud Computer) that provides a single address space with no hardware support for cache-coherence. The results from this work led to the design and development of a new more efficient, lightweight runtime system that is able to scale to larger many-core processors.

The proposed runtime system (called SWITCHES) is included in a complete programming and execution framework. SWITCHES is a software implementation of the task-based Data-flow model for many-core processors. It requires global address space but not necessarily a hardware cache-coherence mechanisms that could limit the scalability of the architecture. SWITCHES implements a lightweight distributed triggering system for runtime task dependence resolution and uses static scheduling and compile time assignment policies to reduce overheads. It supports explicit task resource allocation mechanisms and incorporates machine-learning techniques within the framework to efficiently utilize the underlying resources. To maintain high-levels of programming productivity, the framework implements the latest API standard from OpenMP (v4.5) and extends it to support variable granularity looptasks with dependences across different loops as to favor data-locality in loops with inter-dependences. It provides a source-to-source tool that automatically produces thread-based code that can be compiled by any off-the-shelf C/C++ compiler, applying all existing optimizations.

Performance evaluation of applications with different characteristics on an Intel Xeon Phi system shows good scalability that surpasses the state-of-the-art by an average of 32% and resource utilization is increased with maximum performance achieved using 30% fewer cores for applications with complex dependences.

# Acknowledgments

First of all, I would like to my advisor, Pedro Trancoso, for his continuous support and guidance throughout the years we worked together. Thank you for teaching me how to understand, how to review and how to do research. Thank you for teaching me how to behave and how to react to criticism and how to use it to become a better researcher and a better person. Thank you for being my mentor.

I would like to thank my parents, Yiannakis and Lenia and my sister Anthi for their unconditional love and support, through this long process. For understanding and withstanding, I dedicate this thesis to you.

A big thank you to all my friends for being there for me, whenever needed and for whatever needed. Thank you for bearing and tolerating me all these years and for being there in the good and the not so good times.

I would of course like to thank all the Casper group colleagues that I have had the pleasure to work with and produce research with, Kyriakos, Demos, Marios, Panayiotis, Constantinos and Giannos. Also, thank you to all the colleagues at the Department for all the conversations and discussions, work- or and work-related.

A special thank you to Constantinos Costa for the endless discussions during lunches and dinners at work. We 've come a long way and learned a lot since the day we started. Now it's your turn.

To everybody at the Department of Computer Science, thank you for the excellent cooperation all these years. Special thanks to Melina and Savvoula for taking care of us. Big thanks to the IT team, Savvas, Maria, Andry, Andreas and Loizos for providing all the support and even more.

To Giannis Koutsou and the operations team of the Cyprus Institute, George, Andreas and Thekla - a Big thank you for supporting the Phi cluster. Most of my experiments were done on the Phi cluster and with their support.

"I expect nothing and I accept everything."

"Treat others as you would want to be treated."

## Contributions of this Thesis

#### Journal publications:

- 1. **A. Diavastos** and P. Trancoso. "SWITCHES: A Lightweight Runtime for Dataflow Execution of Tasks on Many-Cores", ACM Transactions on Architecture and Code Optimization (TACO) 14, 3, Article 31, pp. 1-23, August 2017.

- 2. **A. Diavastos**, P. Trancoso, M. Luján, I. Watson, "Integrating Transactions into the Data-Driven Multi-threading Model using the TFlux Platform", International Journal of Parallel Processing (IJPP) 44(2): 257-277, April 2016.

#### Conference and workshop proceedings:

- 3. **A. Diavastos** and P. Trancoso, "Auto-tuning Static Schedules for Task Data-flow Applications", in Proceedings of the 1st ACM Workshop on AutotuniNg and aDaptivity AppRoaches for Energy efficient HPC Systems, (ANDARE), colocated with Parallel Architectures and Compilation Techniques (PACT), pp. 1-6, Portland, Oregon, USA, September 2017.

- 4. **A. Diavastos**, G. Stylianou, P. Trancoso, "TFluxSCC: Exploiting Performance on Future Many-Core Systems through Data-Flow", in Proceedings of the 23rd Euromicro International Conference on Parallel, Distributed and Networkbased Processing (PDP), pp. 190-198, Turku, Finland, March 2015.

- A. Diavastos, P. Trancoso, M. Luján and I. Watson, "Integrating Transactions into the Data-Driven Multi-threading Model using the TFlux Platform" in Proceedings of the Data-Flow Execution Models for Extreme Scale Computing (DFM) Workshop, pp. 19-27, Galveston, Texas, U.S.A., October 2011.

## **Technical reports:**

- 6. **A. Diavastos** and P. Trancoso, "Unified Data-Flow Platform for General Purpose Many-core Systems", Department of Computer Science, University of Cyprus, Nicosia, Cyprus, Technical Report UCY-CS-TR-17-2, pp. 1-22, September 2017.

- 7. **A. Diavastos**, G. Matheou, P. Evripidou and P. Trancoso, "Data-Driven Multithreading Programming Tool-chain", Department of Computer Science, University of Cyprus, Nicosia, Cyprus, Technical Report UCY-CS-TR-17-3, pp. 1-18, September 2017.

## Other Contributions beyond the scope of this thesis:

8. **A. Diavastos**, P. Petrides, G. Falcao and P. Trancoso, "LDPC Decoding on the Intel SCC" in Proceedings of 20th Euromicro International Conference on Parallel, Distributed and Network-Based Computing (PDP), pp. 57-65, Garching, Germany, February 2012.

# Contents

| G | lossa | ry      |                                                   | xvii |

|---|-------|---------|---------------------------------------------------|------|

| 1 | Intr  | oductio | on                                                | 1    |

|   | 1.1   | Motiv   | vation                                            | 1    |

|   | 1.2   | Proble  | em Statement                                      | 2    |

|   |       | 1.2.1   | Application Parallelism                           | 2    |

|   |       | 1.2.2   | Programmability                                   | 3    |

|   |       | 1.2.3   | Scalable Architectures                            | 3    |

|   |       | 1.2.4   | Scalable Runtime Systems                          | 4    |

|   |       | 1.2.5   | Efficient Utilization of Resources                | 4    |

|   | 1.3   | Thesis  | s Statement                                       | 5    |

|   | 1.4   |         | tives and Contributions                           | 5    |

|   |       | 1.4.1   | Goal                                              | 5    |

|   |       | 1.4.2   | Objective 1: Exploit more application parallelism | 5    |

|   |       | 1.4.3   | Objective 2: Programmability                      | 6    |

|   |       | 1.4.4   | Objective 3: Support for Scalable Architectures   | 6    |

|   |       | 1.4.5   | Objective 4: Low-overhead Runtime                 | 6    |

|   |       | 1.4.6   | Objective 5: Efficient Utilization of resources   | 7    |

| 2 | Bac   | kgroun  | nd                                                | 8    |

|   | 2.1   | The D   | Oata-flow Model                                   | 8    |

|   |       | 2.1.1   | Data-flow Runtime Implementations                 | 9    |

|   | 2.2   | The D   | Oata-Driven Multi-threading model                 | 12   |

|   | 2.3   | The T   | Flux Platform                                     | 14   |

|   |       | 2.3.1   | TFlux Programming Tool-chain                      | 16   |

|   | 2.4   | Transa  | actional Memory                                   | 18   |

|   | 2.5   | Many    | r-core Hardware                                   | 19   |

|   | 2.6   | Many    | r-core Software                                   | 22   |

| 3 | Spe | culativ | e Parallelism in Data-flow                   | 25       |

|---|-----|---------|----------------------------------------------|----------|

|   | 3.1 | Motiv   | ration                                       | 26       |

|   | 3.2 | Data-   | flow and Transactional Memory                | 27       |

|   |     | 3.2.1   | Data-flow                                    | 27       |

|   |     | 3.2.2   | Transactional Memory                         | 29       |

|   |     | 3.2.3   | Data-flow and Transactional Memory Combined  | 29       |

|   | 3.3 | Propo   | osed DDM+TM Implementation                   | 30       |

|   |     | 3.3.1   | TFlux System                                 | 30       |

|   |     | 3.3.2   | TinySTM Software Library                     | 31       |

|   |     | 3.3.3   | DDM+TM Implementation                        | 31       |

|   | 3.4 | Workl   | loads                                        | 34       |

|   |     | 3.4.1   | Random Counters                              | 35       |

|   |     | 3.4.2   | Labyrinth implementation of Lee's Algorithm  | 35       |

|   | 3.5 | Exper   | rimental Setup                               | 37       |

|   | 3.6 | Exper   | rimental Results                             | 38       |

|   |     | 3.6.1   | DDM+TM Applications Evaluation               | 38       |

|   |     | 3.6.2   | DDM+TM Overheads Analysis                    | 40       |

|   | 3.7 | Concl   | usions and Contributions                     | 43       |

| 4 | ъ.  | ъ.      |                                              | 4.4      |

| 4 |     |         | en Multi-threading on Many-core Systems      | 44       |

|   | 4.1 |         | ration                                       | 44       |

|   |     |         | SCC Architecture                             | 45       |

|   | 4.3 |         | SCC Implementation                           | 47       |

|   |     | 4.3.1   | TSU Implementations                          | 48       |

|   |     |         | Compilation Toolchain                        | 52<br>52 |

|   | 4.4 | -       | rimental Setup                               | 52<br>54 |

|   | 4.5 |         | rimental Results                             | 54       |

|   | 4.6 | Conci   | usions and Contributions                     | 55       |

| 5 | A S | calable | Framework for Task-based Data-Flow Execution | 56       |

|   | 5.1 | Motiv   | ration                                       | 56       |

|   | 5.2 | The S   | WITCHES System                               | 58       |

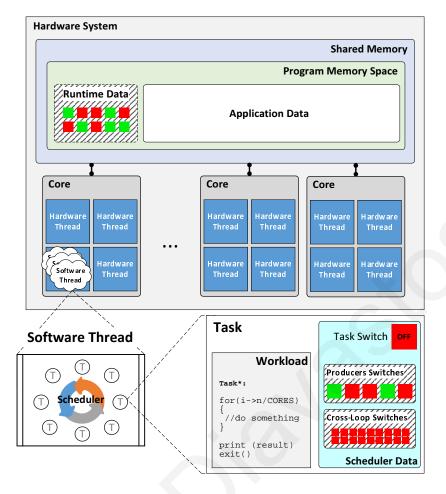

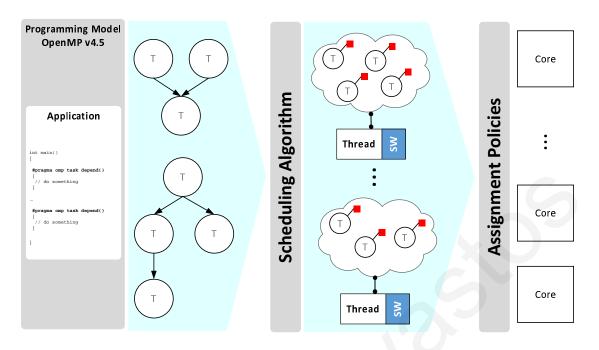

|   |     | 5.2.1   | The Execution Model                          | 59       |

|   |     | 5.2.2   | The Runtime                                  | 60       |

|   |             | 5.2.3  | The Scheduler                                       | 61 |

|---|-------------|--------|-----------------------------------------------------|----|

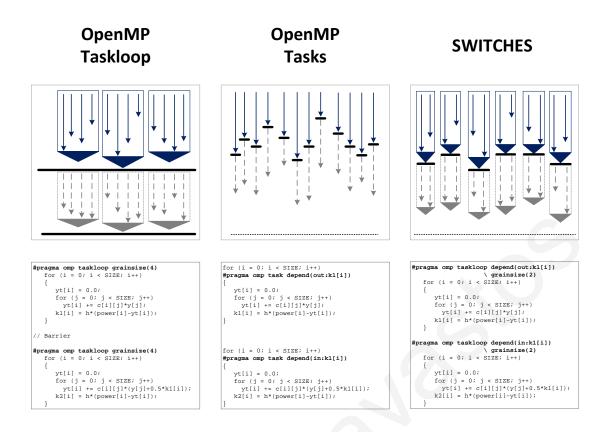

|   | 5.3         | The SV | WITCHES API                                         | 63 |

|   |             | 5.3.1  | Compiler Directives                                 | 63 |

|   |             | 5.3.2  | Cross-Loop Iteration Dependences                    | 66 |

|   |             | 5.3.3  | Task Resource Allocation                            | 67 |

|   |             | 5.3.4  | Example                                             | 67 |

|   | 5.4         | The Tr | ranslator                                           | 69 |

|   | 5.5         | Exper  | imental Setup                                       | 71 |

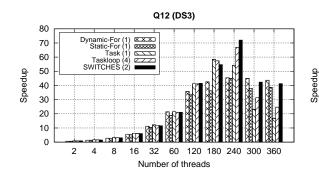

|   | 5.6         | Exper  | imental Evaluation                                  | 73 |

|   |             | 5.6.1  | Data-Parallel Application                           | 73 |

|   |             | 5.6.2  | Task-Parallel Applications                          | 75 |

|   |             | 5.6.3  | Explicit Task Resource Allocation                   | 77 |

|   |             | 5.6.4  | Discussion                                          | 78 |

|   | 5.7         | Concl  | usions and Contributions                            | 81 |

| 6 | Aut         | onomia | Mapping for Efficient Utilization of Resources      | 82 |

| • | 6.1         |        | ation                                               | 82 |

|   | 6.2         |        | nizing Task Scheduling                              | 84 |

|   | o. <b>_</b> | 6.2.1  | The NSGA-II Genetic Algorithm                       | 85 |

|   | 6.3         |        | tuning Static Scheduling                            | 86 |

|   | 6.4         |        | imental Results                                     | 88 |

|   |             | •      | Experimental Setup                                  | 88 |

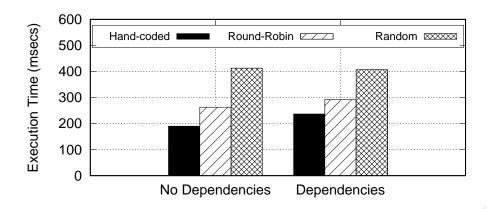

|   |             | 6.4.2  | Synthetic Applications                              | 89 |

|   |             | 6.4.3  | Data-Parallel Applications                          | 90 |

|   |             | 6.4.4  | Task-Parallel Applications                          | 90 |

|   |             | 6.4.5  | Seed Optimization                                   | 92 |

|   |             | 6.4.6  | Discussion                                          | 93 |

|   | 6.5         | Concl  | usions and Contributions                            | 94 |

| _ |             |        |                                                     |    |

| 7 |             |        | ns and Future Work                                  | 95 |

|   | 7.1         |        | ved Objectives and Contributions                    | 95 |

|   | 7.2         | _      | Research Directions                                 | 97 |

|   |             | 7.2.1  | Direction 1: Speculative Parallelism on Many-cores  | 97 |

|   |             | 7.2.2  | Direction 2: Inter-node Scalability using Data-flow | 98 |

|   |     | 7.2.3  | Direction 3: Dynamic Rescheduling of Static tasks    | 98  |

|---|-----|--------|------------------------------------------------------|-----|

|   |     | 7.2.4  | Direction 4: Heterogeneous Many-cores                | 98  |

|   |     | 7.2.5  | Direction 5: Extension of the programming tool-chain | 99  |

|   |     | 7.2.6  | Direction 6: Fault-tolerance                         | 99  |

| A | SWI | TCHES  | S Compiler Directives                                | 111 |

|   | A.1 | SWITC  | CHES API                                             | 111 |

|   |     | A.1.1  | Master                                               | 111 |

|   |     | A.1.2  | Global variables                                     | 112 |

|   |     | A.1.3  | Parallel                                             | 112 |

|   |     | A.1.4  | For                                                  | 113 |

|   |     | A.1.5  | Sections                                             | 114 |

|   |     | A.1.6  | Section                                              | 114 |

|   |     | A.1.7  | Task                                                 | 115 |

|   |     | A.1.8  | Taskloop                                             | 116 |

|   |     | A.1.9  | Parallel For                                         | 117 |

|   |     | A.1.10 | Parallel Sections                                    | 118 |

|   | A.2 | SWITC  | CHES Examples                                        | 119 |

|   |     | A.2.1  | Example 1: Tasks Dependences                         | 119 |

|   |     | A.2.2  | Example 2: Cross-Loop Dependences                    | 120 |

|   |     |        |                                                      |     |

# List of Figures

| 2.1  | The layered design of the TFlux system                           | 15 |

|------|------------------------------------------------------------------|----|

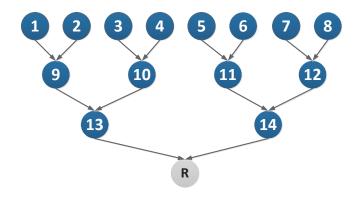

| 3.1  | A Data-flow graph for calculating a reduction operation          | 28 |

| 3.2  | Random Counters implementation with DDM+TM directives            | 34 |

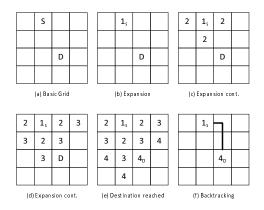

| 3.3  | Lee's algorithm example                                          | 35 |

| 3.4  | Lee's Algorithm pseudo-code with TFlux DDM+TM directives         | 36 |

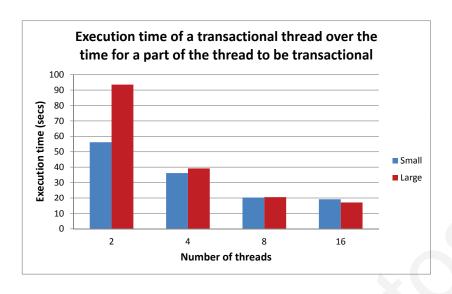

| 3.5  | Comparison of complete and partially transactional threads       | 39 |

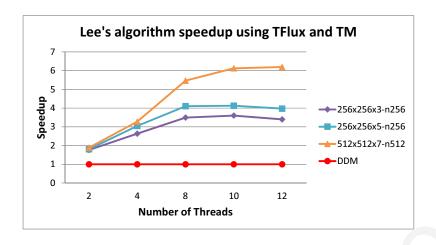

| 3.6  | Scalability of Labyrinth's DDM+TM implementation                 | 40 |

| 3.7  | Overheads of monitoring one versus all shared variables          | 41 |

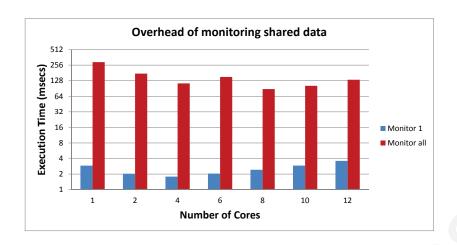

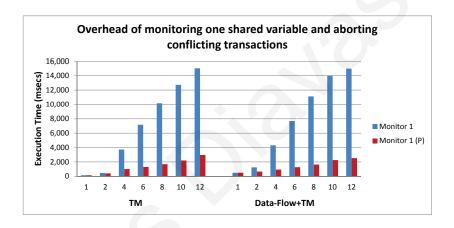

| 3.8  | Overheads of aborting conflicting transactions                   | 41 |

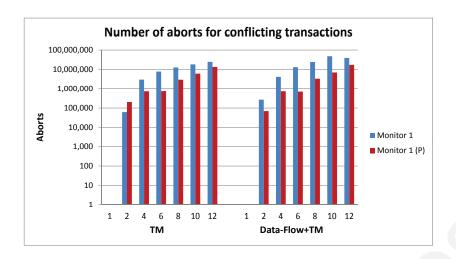

| 3.9  | Number of aborts of conflicting transactions                     | 42 |

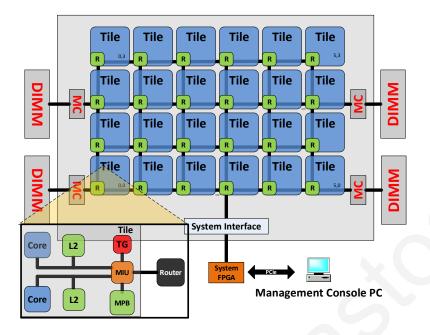

| 4.1  | Intel SCC top-level and tile top-level architecture              | 46 |

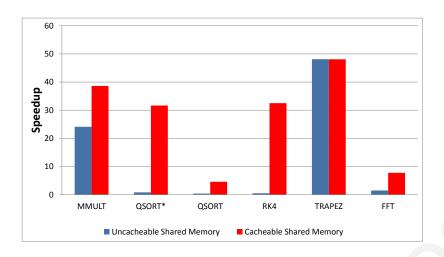

| 4.2  | Speedup comparison of uncacheable versus cacheable shared memory | 48 |

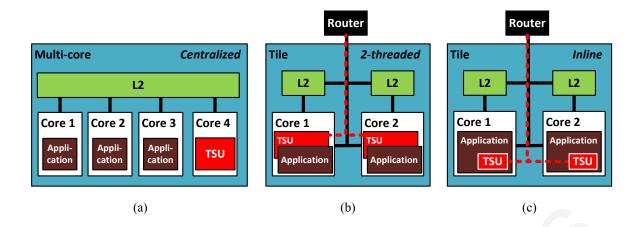

| 4.3  | The TSU Evolution                                                | 49 |

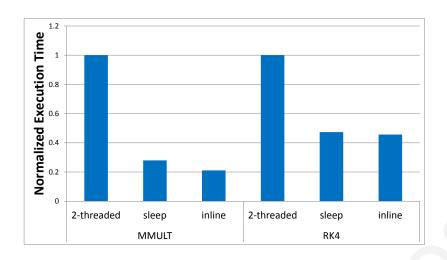

| 4.4  | TSU implementations execution time                               | 50 |

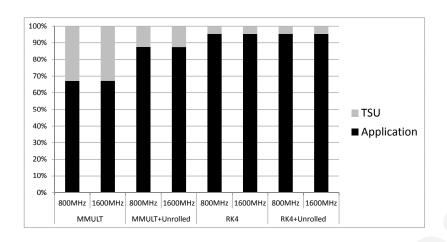

| 4.5  | Execution time breakdown for different frequencies               | 51 |

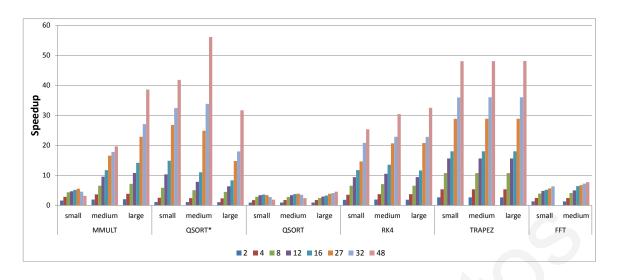

| 4.6  | Performance scalability of TFluxSCC                              | 53 |

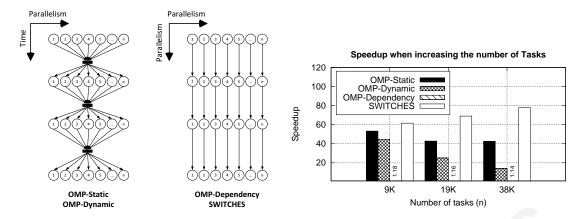

| 5.1  | SWITCHES motivation                                              | 58 |

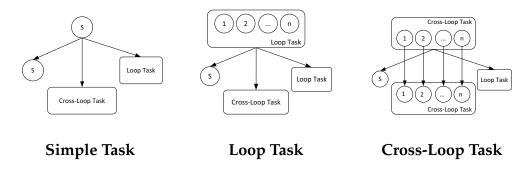

| 5.2  | Types of SWITCHES tasks                                          | 59 |

| 5.3  | The architectural design of SWITCHES                             | 60 |

| 5.4  | Cross-Loop Iteration Dependences                                 | 66 |

| 5.5  | Cross-loop Iteration Dependences example                         | 68 |

| 5.6  | The SWITCHES layered design                                      | 69 |

| 5.7  | Assignment policies                                              | 70 |

| 5.8  | Application translation procedure                                | 70 |

| 5.9  | Q12 speedup on the KNC                                           | 74 |

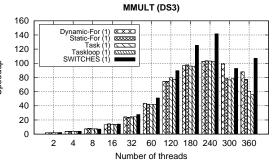

| 5.10 | MMULT speedup on the KNC                                         | 74 |

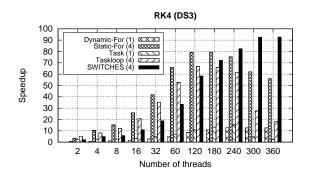

| 5.11 | RK4 speedup on the KNC                                           | 75 |

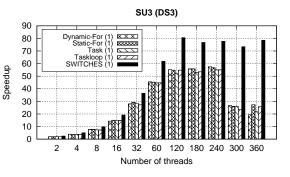

| 5 12 | SU3 speedup on the KNC                                           | 75 |

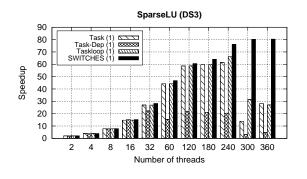

| 5.13 | LU speedup on the KNC                                    | 76  |

|------|----------------------------------------------------------|-----|

| 5.14 | Ocean speedup on the KNC                                 | 76  |

| 5.15 | Poisson2D speedup on the KNC                             | 76  |

| 5.16 | Cross-Loop dependence performance evaluation             | 77  |

| 5.17 | Best speedup achieved on the Intel KNC                   | 78  |

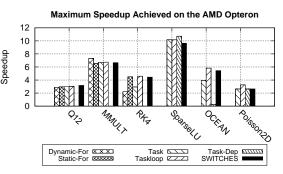

| 5.18 | Best speedup achieved on the AMD Opteron                 | 78  |

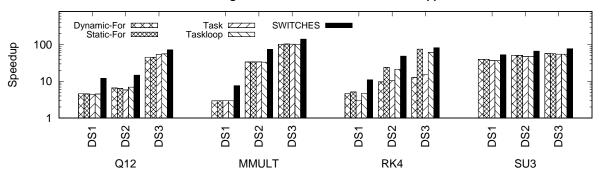

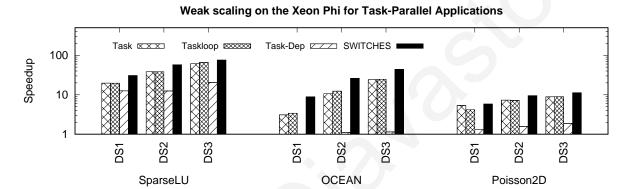

| 5.19 | Weak scaling on the KNC for data-parallel applications   | 80  |

| 5.20 | Weak scaling on the KNC for task-parallel applications   | 80  |

|      |                                                          |     |

| 6.1  | Auto-tuning motivation                                   | 83  |

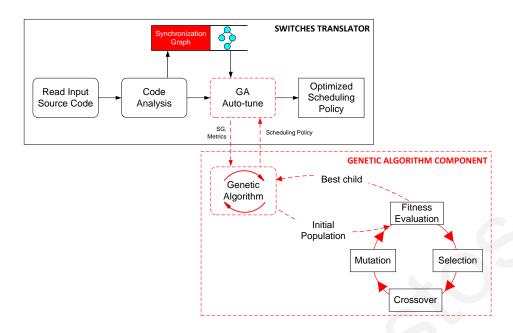

| 6.2  | Auto-tuning architectural design                         | 86  |

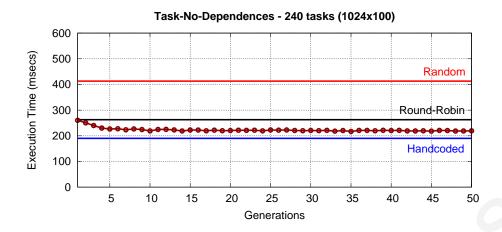

| 6.3  | Execution time of No-Dependences kernel with auto-tuning | 89  |

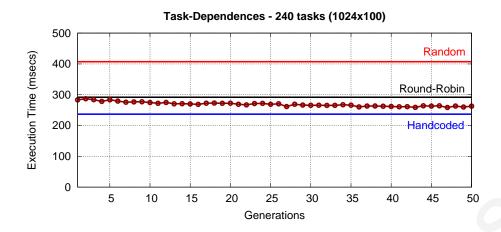

| 6.4  | Execution time of Dependences kernel with auto-tuning    | 90  |

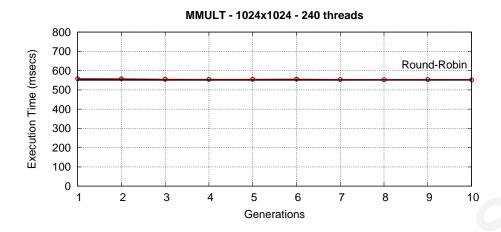

| 6.5  | Execution time of MMULT with auto-tuning                 | 91  |

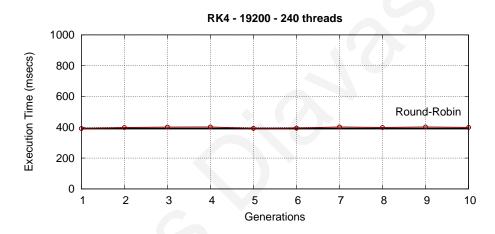

| 6.6  | Execution time of RK4 with auto-tuning                   | 91  |

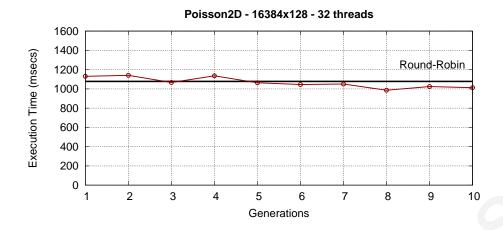

| 6.7  | Execution time of Poisson2D-32 threads with auto-tuning  | 92  |

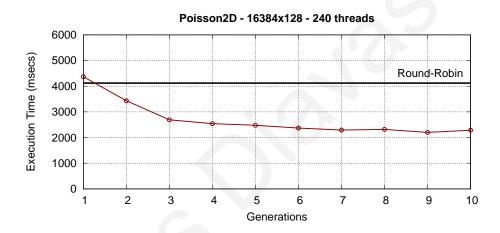

| 6.8  | Execution time of Poisson2D-240 threads with auto-tuning | 92  |

| 6.9  | Auto-tuning seed optimization results                    | 93  |

| A.1  | Task Dependences example                                 | 119 |

| A.2  | Cross-loop Iteration Dependences example                 | 120 |

# List of Tables

| 2.1 | Data-flow background implementations 1              | 10 |

|-----|-----------------------------------------------------|----|

| 2.2 | Data-flow background implementations 3              | 12 |

| 2.3 | DDM background implementations 1                    | 13 |

| 2.4 | DDM background implementations 2                    | 14 |

| 2.5 | TFlux DDM pragma directives                         | 16 |

| 2.6 | DDMVM pragma directives extensions                  | 17 |

|     |                                                     |    |

| 3.1 | TFlux DDM+TM pragma directives                      | 32 |

| 3.2 | DDM+TM directives correspondence with TinySTM calls | 33 |

| 3.3 | TFluxTM experimental workloads and data sizes       | 37 |

| 3.4 | Random Counter Commits/Aborts for TM and DDM+TM     | 38 |

| 3.5 | Labyrinth Commits/Aborts for TM and DDM+TM          | 39 |

| 4.1 | TFluxSCC experimental workloads and data sizes      | 52 |

|     |                                                     |    |

| 5.1 | The SWITCHES API                                    | 64 |

| 5.2 | SWITCHES experimental workloads description         | 72 |

| 5.3 | Execution time of each SWITCHES execution scenario  | 79 |

| 61  | Auto-tuning experimental workloads and data sizes   | 88 |

# Glossary

**Data-flow** The Data-flow Model of Execution

**Thread** A software unit of execution (*i.e.* a pthread).

**Task** A unit of work to be executed (*e.g.* a loop iteration).

**Performance** How fast a task finishes in relation to execution time.

**Runtime** Runs during execution of an application.

**Many-core** A processor with 100s of hardware execution units.

**Scalability** Increase in relation to the number of hardware units.

**Asynchronous** Tasks execute freely without interactions with each other.

**Granularity** The scale or size of a task.

**Off-the-shelf** Taken from existing/commodity systems.

**Source-to-source** Takes as input and produces as output a source code.

**Auto-tuning** Automatically tunes the execution without programmer intervention.

**TFluxHard** The hardware implementation of the TFlux runtime system.

**TFluxSoft** The software implementation of the TFlux runtime system.

**TFluxTM** The implementation of the TFlux Platform that includes support for Transactional Memory.

**TFluxSCC** The implementation of the TFlux Platform for the Intel SCC processor.

**SWITCHES** The system that we propose and includes a runtime scheduler and a programming platform.

**HPC** High Performance Computing

**GPU** Graphic Processing Unit

MIC Many Integrated Core

**DDM** Data-Driven Multithreading

**TM** Transactional Memory

**API** Application Programming Interface

**SCC** Single-chip Cloud Computer

**NLA** Numerical Linear Algebra

**SG** Synchronization Graph

**TSU** Thread Scheduling Unit

**PPE** Power Processor Element

**SPE** Synergistic Processor Element

**DMA** Direct Memory Access

**DDMVM** Data-Driven Multithreading Virtual Machine

**FPGA** Field-Programmable Gate Array

**DDMCPP** Data-Driven Multithreading C Pre-Processor

**SMCC** Software Managed Cache Coherence

LDPC Low-Density Parity Check

FEB Full/Empty Bits

**OCR** Open Community Runtime

**MPB** Message Passing Buffer

MIU Message Interface Unit

**LUT** Lookup Table

**MC** Memory Controller

**SPMD** Singe Program Multiple Data

**KNC** Knights Corner

**GA** Genetic Algorithm

NSGA Non-dominated Sorting Genetic Algorithm

GAC Genetic Algorithm Component

**TSX** Transactional Synchronization Extentions

Chapter 1

## Introduction

Improving application performance in an efficient and effective way is a joint task between both the hardware and the software. Performance scaling is determined by a combination of the following factors: the degree of parallelism, programmability, low-overhead runtime systems, locality-aware execution, efficient use of the available resources and scalable architecture designs. In this thesis we focus on the Task Data-flow model as the most appropriate for exploiting large amounts of parallelism and explore ways to address the above mentioned factors in order to scale application performance on commodity hardware, from conventional multi-cores to future many-cores with hundreds of cores. Our efforts brought the implementation of parallel programming and execution platform that is publicly available for download in [1].

### 1.1 Motivation

Performance improvement is the principal driver in High Performance Computing (HPC). This improvement was achieved by increasingly adding more nodes to the large-scale systems. Nevertheless, as suggested by M. Resch [2], the number of nodes in future exascale systems may not change dramatically compared to those of today because of the prohibitive cost. It is the number of cores in a single node that will increase with the use of single-chip many-core processors leading to large-scale HPC machines with millions of processing units. Most HPC facilities today use many-core processors such as the Graphic Processing Units (GPUs) [3] and the Intel Many Integrated Core (MIC) processors [4] as to achieve high-performance within a certain power budget. Nevertheless, programing a million units is an extremely

difficult task as can be seen in HPC centers today. Message-passing models are most commonly used but they will become a bottleneck for intra-node performance as they are designed for only a few thousands of processing units and their programming is already a challenging task. Therefore, new parallel programming frameworks and runtime systems are needed to support the future HPC large-scale machines [2].

#### 1.2 Problem Statement

There has recently been a renewed interest in the Data-flow model as a way to efficiently exploit large-scale parallel computation. The work in this thesis is based on the task-based Data-flow model of execution that is the most appropriate for exploiting large amounts of parallelism. Nevertheless, existing runtime systems offer limited performance scalability (see Chapter 2). The main factors that affect the scaling of application performance on large-scale many-core systems are: the degree of parallelism, programmability, low-overhead runtime systems, locality-aware execution, efficient use of the available resources and scalable architecture designs. To address these factors and achieve performance that scales in the many-core era it is essential to answer the questions presented in the following sections.

### 1.2.1 Application Parallelism

The Data-flow model is an asynchronous (non-blocking) model capable of exploiting large amounts of parallelism as the execution follows the path of the data, thus a natural paradigm for expressing parallelism. Whenever the input operands of an instruction in a Data-flow program is produced, the instruction can be executed. Despite the simplicity of the idea, extracting producer/consumer relationships in applications described by complex algorithms is proven to be a difficult task, even for highly experienced programmers. Partly, this is because of the strictness of the model as it doesn't allow shared state in Data-flow programs, even in cases where this is a fundamental operation. Therefore, a different approach must be followed in order to keep the benefits of the Data-flow model and at the same time not burden the users with the difficult task of extracting all dependences from complex algorithms.

**RESEARCH QUESTION 1:** Is it possible to relax the definition of dependences and increase the parallelism exploited, without loosing the benefits of Data-flow?

#### 1.2.2 Programmability

Message-passing models that are most commonly used in HPC systems will become a bottleneck for intra-node performance as they are designed and optimized for large-scale distributed systems [2,5]. But even so, programing a million units is an impossible task as can be seen in HPC centers today [2]. Although HPC users are highly experienced programmers, there is a lack of compelling motivation for switching programming environments unless the performance gains are high and the development effort is low [5]. Therefore, existing parallel execution frameworks need to be extended for large-scale many-core systems and provide user-friendly programming tools, already familiar to the HPC community.

**RESEARCH QUESTION 2:** Is it possible to provide the programming community with tools that can exploit large degrees of parallelism using well known language constructs based on highly adopted environments?

#### 1.2.3 Scalable Architectures

Shared-memory multi-core processors with powerful cores have been holding the largest share in the HPC industry the past decade. The architectural design of such processors is guided (among others) by its ability to produce more performance with legacy software. Parallel processing has become the de-facto standard for increasing application performance and in order to continue and optimize power-performance efficiency in such systems the trend today is to include more cores in a single processor [2]. From the hardware design perspective, many simple cores will be added, leading towards single-chip large-scale many-core processors. But, as the number of cores in a processor gradually increases, simpler designs must be explored by the vendors in order to reduce hardware costs and improve energy-efficiency [6]. Therefore, lightweight cores will be included and expensive mechanisms such as cache-coherence might be removed from future many-core designs as to allow the scalability of the architectures to continue [7,8].

**Research Question 3:** How do low-cost scalable architectures with many lightweight cores impact runtime systems and application performance?

#### 1.2.4 Scalable Runtime Systems

Scaling the number of cores alone does not result in reduced execution time. From the software perspective, many-core processors create new challenges as there is a need for scheduling systems that can efficiently exploit parallelism without incurring runtime overheads and are able to increase speedup regardless of the number of cores. Most Data-flow runtime systems that exist today (presented in Chapter 2) follow a centralized approach, creating a single-point of communication for parallel tasks that will become a bottleneck on large-scale processors. A centralized runtime implementation implies sharing of scheduling data structures that requires locking and coherence mechanisms in order to ensure correct execution. As previously explained in Section 1.2.3, the use of such techniques results in large performance overheads and limits the scalability of both the software and the hardware [6]. Also, almost all current runtime systems use dynamic scheduling that provides adaptability to irregular executions, but results in large runtime overheads, especially in applications with complex dependences on large-scale many-cores.

**RESEARCH QUESTION 4:** Is it possible to develop a low-overhead runtime system that scales regardless of the number of cores and requires minimum hardware support?

#### 1.2.5 Efficient Utilization of Resources

It is particularly common in large-scale systems to have under-utilized hardware resources that result in wasted performance and energy [5]. Efficiently mapping tasks from a parallel application with irregular data access patterns and complex dependences to a large-scale system is an extremely difficult task, even for highly experienced programmers. A runtime system with a dynamic scheduling policy could be a possible solution to such a problem but as explained earlier, finding a better scheduling at runtime incurs in significant overheads that will not scale on future many-core processors. Therefore, new scheduling techniques and tools are needed that can utilize large number of hardware resources and provide optimized power-performance efficiency.

**RESEARCH QUESTION 5:** Is it possible to develop a tool that automatically provides scheduling policies, able to efficiently utilize the underlying resources?

#### 1.3 Thesis Statement

In order to achieve application performance scalability for processors with large number of cores (many-cores) you need to collectively address parallelism, programmability, runtime system, resource utilization, and architecture design limitations.

# 1.4 Objectives and Contributions

#### 1.4.1 Goal

The main goal of this thesis is to address the factors that affect the scalability of application performance on large-scale many-core processors. To achieve this goal, the task-based Data-flow model is used and in particular the Data-Driven Multi-threading (DDM) [9] model, a higher-granularity execution model of the Data-flow paradigm. In order to hide scheduling and communication latencies, DDM applies dependences across threads (collection of instructions) instead of single instructions as in the original implementations of Data-flow. To present our findings we evaluate our implementations with applications from different domains that exhibit the characteristics we want to show for each objective. The objectives and contributions of this Thesis are stated below.

### 1.4.2 Objective 1: Exploit more application parallelism

To answer *Research Question 1* (Section 1.2.1), the Data-flow model is to be extended to support speculative parallelism by incorporating Transactional Memory (TM). More precisely, explore shared mutable data by integrating transactions in Data-flow in order to execute more tasks in parallel that would otherwise be serialized. Therefore, further parallelism can be exploited while mutable shared state can be introduced to the Data-flow model in a composable way.

**CONTRIBUTION:** This work is the first software integration of transactions into a task-based Data-flow implementation as a way to introduce shared state in the Data-flow model. It offers software support for developing Data-flow applications with TM support [10], while it provides an overhead analysis of the integration of the two models [11]. More details on the implementation and results of this work are presented in Chapter 3.

#### 1.4.3 Objective 2: Programmability

In order to address *Research Question 2* (Section 1.2.2) and maintain high-levels of programming productivity, a unified Data-flow platform is to be developed that will support different DDM runtime systems and different types of hardware processors [12,13] (see Chapter 2). To provide for easy to program environments, the most commonly used Application Programming Interface (API), the OpenMP v4.5, must be implemented.

**CONTRIBUTION:** This work extends the OpenMP v4.5 API to support explicit task resource allocation mechanisms and variable loop task granularity to increase data-locality even for loop tasks with inter-dependences. It provides a source-to-source tool that automatically produces thread-based code that can be compiled by any off-the-shelf C/C++ compiler, applying all existing optimizations [14]. Details on the API supported and the extensions implemented are presented in Chapter 5.

### 1.4.4 Objective 3: Support for Scalable Architectures

To address *Research Question 3* (Section 1.2.3), the DDM model [9], is to be ported on the Intel Single-chip Cloud Computer (SCC) many-core system [15]. Intel SCC is an experimental processor for many-core software development that does not provide support for cache-coherence in order to scale the architecture design to a large number of cores.

**CONTRIBUTION:** The work presented in Chapter 4 is the first DDM implementation for a many-core processor [16]. It provides low-overhead software support for shared-memory execution without requiring hardware cache-coherence mechanisms as to avoid factors that can limit the scalability of the architectures [6–8].

### 1.4.5 Objective 4: Low-overhead Runtime

To answer *Research Question 4* (Section 1.2.4) a new runtime system that implements the task-based Data-flow model, is to be designed and developed in order to exploit large degrees of parallelism and at the same time addresses the trade-offs of *Research Question 3* (Section 1.2.3) as to be more efficient, lightweight and scale regardless of the number of cores used.

Contribution: This work proposes a software runtime system for many-core

processors that supports global address space without the need for hardware cachecoherence mechanisms [14]. It implements a lightweight distributed triggering system for task runtime dependence resolution and uses static scheduling and compile time assignment policies to reduce overheads. More details on the implementation of the runtime system are presented in Chapter 5.

#### 1.4.6 Objective 5: Efficient Utilization of resources

To address the issue of under-utilized execution presented in *Research Question 5* (Section 1.2.5), we will employ a machine-learning technique to automatically map tasks to the underlying hardware. Using machine-learning, the scheduling policy can be automatically optimized for execution time, power consumption, temperature or any combination of the three. At the same time, the hardware can be utilized to achieve maximum performance using fewer resources than what common scheduling policies use.

**CONTRIBUTION:** The main contribution of this work is the integration of a machine-learning algorithm in a real parallel framework that produces an autotuning scheduling tool for task-based parallel applications [17]. Details on the implemented auto-tuning tool are presented in Chapter 6.

# Background

The work presented in this thesis is based on the Task model, where tasks are scheduled in a Data-flow fashion. More precisely, we use the DDM model of execution [9] as a baseline for this work. In the following sections the background of this work that is related to the Data-flow model is presented along with the software runtime systems that implement it (Section 2.1), the DDM model and its implementations to date (Section 2.2), the TFlux Platform [18] that is the framework used as a starting point for this work (Section 2.3) and finally software frameworks that exist today for various HPC-based many-core systems (Section 2.5). The DDM model is also implemented as a hardware runtime unit [18,19] but these implementations are out of the scope of this work as we focus on a software solution that can execute on commodity hardware.

#### 2.1 The Data-flow Model

The original Data-flow model was proposed by Jack Dennis in the early 1970s [20, 21] as an alternative to the Control-flow (von Neumann) model. Instructions in a Data-flow program are executed when all their input operands are available, creating an asynchronous (non-blocking) execution. The availability of the operands is expressed using data dependences, that define a Data-flow graph representing the order of the execution. Using the Data-flow graph and the input operands required by each instruction, one can expose parallelism in a program. Many systems today try to explore fine-grain parallelism by using Data-flow-like models as a way to achieve high performance and utilization on large-scale many-core systems with hundreds to thousands of cores [22–25].

The main advantage of the Data-flow model is the ability to exploit maximum parallelism from an application by exposing fine-grain tasks. This large degree of parallelism can be exploited to hide the latency of memory accesses. Unlike other models, Data-flow does not require synchronization mechanisms as the correctness of the execution is assured by enforcing the data dependences. Nevertheless, exploiting fine-grain parallelism was also the limiting factor in the success of this model in past implementations, mostly due to the overheads in enforcing the data dependences at the instruction level. More recent attempts managed to overcome these overheads by adopting the model at a coarser granularity (*e.g.* tasks), consequently achieving high performance [9,22–24].

Another relevant factor towards using Data-flow for increasingly large systems is its disciplined access to shared data. Assuming a task-based implementation of Data-flow, it is ensured by the model that no concurrent tasks will be modifying the same data, as this would result in a data dependence violation [20, 21, 26]<sup>1</sup>. Therefore, in a shared-memory system the Data-flow model doesn't require a hardware implementation of a cache-coherence protocol as access on shared data may be coordinated by the model itself. Correctness of the application may be assured simply by updating cached data to and from main memory on completion of a task, *i.e.* flushing updated values to memory and invalidating cached copies in other cores. The fact that hardware cache-coherence is not required by the Data-flow model, allows for increasing performance scalability on many-cores as shown in [16], reducing hardware costs and improving energy-efficiency [6].

## 2.1.1 Data-flow Runtime Implementations

Recently, there has been renewed interest in the Data-flow approach to computation that was pioneered in late 70s and 1980s [27–31]. These projects demonstrated that it was feasible to express sufficiently large amounts of parallelism but a significant problem was how to throttle and schedule it. Subsequent projects, like DDM [9], OmpSs [22], etc. showed that coarsening granularity (from instructions to tasks) could result in more a controllable and efficient parallel execution.

Numerical Linear Algebra (NLA) is one area where Data-flow ideas have recently

<sup>&</sup>lt;sup>1</sup>This is according to the strict Data-flow definition while in Chapter 3 a relaxed version that uses Transactional Memory to handle the use of shared context between tasks is explored.

*Table 2.1: Data-flow implementations on multi-cores from the literature.*

| Description     | OmpSs [22] | Triggered         | Serialization Sets [33] | OpenDF [34]  |

|-----------------|------------|-------------------|-------------------------|--------------|

|                 |            | Instructions [32] |                         |              |

| Implementation  | Software   | Hardware          | Software                | Hardware     |

| Scheduling      | Dynamic    | Dynamic           | Dynamic                 | -            |

| Memory Model    | Shared     | Shared            | Shared                  | -            |

| Cache-coherence | Yes        | No                | Yes                     | -            |

| Dependences     | Pragma     | Inserted          | Writable and read-only  | -            |

|                 | Directives | triggers          | variables               |              |

| Parallelism     | Task-based | Spatial           | Serialization sets of   | Data-flow    |

|                 |            |                   | dependent operations    | Instructions |

| Description     | DTT/CDTT [35] | SEED [36]     | Statically          | WaveScalar [38] |

|-----------------|---------------|---------------|---------------------|-----------------|

|                 |               |               | Sequential [37]     |                 |

| Implementation  | Software      | Hardware      | Software            | Hardware        |

| Scheduling      | Dynamic       | Dynamic       | Dynamic             | Dynamic         |

| Memory Model    | Shared        | Shared        | Shared              | Shared          |

| Cache-coherence | -             | -             | Yes                 | Yes             |

| Dependences     | Macro-based   | -             | Functions, shared   | tokens/tags     |

|                 | triggers      |               | objects, read/write |                 |

|                 |               |               | sets, sequential    |                 |

|                 |               |               | segments            |                 |

| Parallelism     | Data-flow     | Hybrid        | Statically          | Data-flow       |

|                 |               | Data-flow +   | sequential          | instructions    |

|                 |               | von- programs |                     |                 |

|                 |               | Neumann       |                     |                 |

been adopted. This is apparent in both LAPACK and BLAS functionality (PLASMA project [39]), for sparse matrices [40]. NLA constitutes one of the main kernels for scientific computing and their main next challenge is how to scale to petaflop-scale high performance systems. The new generation of NLA algorithms are moving towards expressing parallelism but leaving the scheduling to the runtime trying to harness the available combination of resources (multi-cores, many-cores, clusters, GPUs). It has been demonstrated that a Data-flow execution using Parallel Linear Algebra for Scalable Multi-core Architectures (PLASMA) can easily generate millions of tasks. Convolutional networks in computer vision [41–43] have been using GPUs for performance exploitation but it has recently been investigated for parallelism exploitation on single shared memory CPU machines as the task dependency graph

implies linear speedup in within the PRAM model of parallel computation [44].

There is a clear relation between Data-flow computations and parallelization of functional languages. Another highly prominent use of functional programming techniques can be observed in the MapReduce frameworks [45]. Provided the map and reduce operations are side-effect free, we can automatically parallelize their execution using a Data-flow approach.

Tables 2.1 and 2.2 present recent work from the literature that use Data-flow concepts in programming multi-core systems. The tables present the type of each implementation (software or hardware), the scheduling policy used by each runtime system, the underlying memory model, whether it requires hardware support for cache-coherence, the way dependences are expressed and the type of parallelism exploited in each system. We focus our attention on OmpSs [22], SWARM [24] and Intel TBB [23], as they are the closest to the model we use and the runtime we implement in this thesis.

OmpSs is a software task-based programming model based on the OpenMP [46] and the StarSs [47]. Its target is heterogeneous multi-core architectures, thus it incorporates the use of OpenCL and CUDA kernels. OmpSs outperforms OpenCL or OpenMP in some applications for the same platforms while it offers a more flexible programming environment to exploit multiple accelerators. The basic differences of OmpSs with what is proposed in this work is that the dependences of the parallel tasks are resolved at runtime and the scheduling is decided by the scheduling unit also at runtime. OmpSs is also built as a shared memory model, thus it needs a hardware cache-coherence mechanism in order to provide correct execution.

Intel TBB is another software implementations that uses Data-flow concepts for scheduling parallel tasks. TBB is following a dynamic scheduling policy and is using a task stealing approach to distribute the tasks to the available cores. The programming model of TBB is using macro-statements in a C++ environment that makes the programming non-trivial compared to other systems with the more programmer-friendly compiler directives.

Finally, SWARM is an implementation of a Data-flow system for both shared and distributed memory systems. It uses a dynamic scheduling policy with a runtime system design that doesn't require hardware support for cache-coherence. The programming of SWARM is done using C-based macros that require from the programmer to re-write the entire application to be compatible with the runtime system

*Table 2.2: Data-flow implementations on multi-cores from the literature (cont.).*

| Description     | SWARM [24] | Intel TBB [23] | CnC [48]          | Maxeler [49] |  |

|-----------------|------------|----------------|-------------------|--------------|--|

| Implementation  | Software   | Software       | Software          | Hardware     |  |

| Scheduling      | Dynamic    | Dynamic        | Dynamic           | Static       |  |

| Memory Model    | Hybrid     | Shared         | Shared            | -            |  |

| Cache-coherence | No         | Yes            | Yes               | -            |  |

| Dependences     | Codelet    | Explicit task  | Input/Output      | Input/Output |  |

|                 | macros     | dependence     | declaration       | variables    |  |

|                 |            | macros         |                   |              |  |

| Parallelism     | Codelets   | Concurrent     | Data-flow and     | Data-flow,   |  |

|                 |            | Containers     | Stream-processing | Spatial and  |  |

|                 |            |                |                   | Stream       |  |

#### of SWARM.

TERAFLUX [25] was a project funded by the European Union aiming to solve the challenges of programmability, manageable architecture design and reliability of a 1000+ core chips by using the Data-flow principles. The idea was to develop new programming models, compiler analysis and optimization technologies in order to build a scalable architecture based mostly on off-the-shelf components while simplifying the design of such Tera-device systems. TERAFLUX used the TFlux platform as a programming and execution system for DDM programs on the proposed machine.

## 2.2 The Data-Driven Multi-threading model

DDM is a Data-flow model where the granularity of the Data-flow code is a thread and the synchronization part of the program is separated from the communication part as to overcome the synchronization and communication overheads imposed by the dynamic scheduling process [9,50] on multi-core execution. DDM programs are composed of Data-Driven Threads (DThreads) that contain an arbitrary number of instructions. Within a DThread the instruction execution follows the classic control-flow model, thus allowing any other runtime or compile-time optimizations to be performed. The programming of the DDM model is done explicitly by the programmer by defining the DThreads in a program and the dependences between them, either by declaring a direct dependence on other DThreads or by declaring the

*Table 2.3: Data-Driven Multithreading implementations.*

| Description     | $D^2NOW$    | $DDMVM_c$   | $DDMVM_s$  | $DDMVM_d$   | $DDMVM_{FPGA}$ |

|-----------------|-------------|-------------|------------|-------------|----------------|

| Date Introduced | 1999        | 2011        | 2011       | 2013        | 2014           |

| Implementation  | Hardware    | Software    | Software   | Software    | Hardware       |

| Scheduling      | Static      | Static and  | Static and | Static      | Static and     |

|                 |             | Dynamic     | Dynamic    |             | Dynamic        |

| Memory Model    | Distributed | Distributed | Shared     | Shared and  | Shared         |

|                 |             |             |            | Distributed |                |

| Cache-coherence | -           | No          | Yes        | Yes         | No             |

| Dependences     | Macros      | Macros      | Directives | Macros      | Directives     |

inputs and outputs of the DThreads. The dependences and the inputs/outputs form a producer/consumer relationship between the DThreads in a program and their combination creates the Synchronization Graph (SG) of the DDM program. The parallel execution of the all DThreads in a DDM program is managed by a centralized Thread Scheduling Unit (TSU) that uses the SG in order to correctly synchronize the firing of ready DThreads and the update of waiting DThreads.

Table 2.3 presents all DDM systems implemented to date. D<sup>2</sup>NOW [51] is a hardware implementation for a distributed system of single-core nodes. D<sup>2</sup>NOW is the first DDM simulated hardware distributed implementation that also incorporated the CacheFlow technique, a deterministic data prefetching scheme using data-driven caching policies [52]. DDMVM<sub>c</sub> is also a DDM implementation for a heterogeneous processor (the IBM CELL/BE). DDMVM<sub>c</sub> uses a centralized TSU that is executed on the Power Processor Element (PPE) of the processor, while the Synergistic Processing elements (SPEs) were used for executing the application threads. The communication between the TSU and the application threads is done explicitly using Direct Memory Access (DMA) commands. DDMVM<sub>c</sub> was the first to implement a software version of the CacheFlow technique for moving data close to the cores prior to their reference. DDMVM<sub>c</sub> is also the first implementation of DDM that uses a dynamic scheduling policy for assigning the parallel threads to the cores of the system. The same implementation was also ported to SMP processors with shared memory and was called DDMVM<sub>s</sub> [53]. As DDMVM<sub>s</sub> is using shared memory to store its scheduling data structures and requires hardware cache-coherence support and simultaneous access protection mechanisms (locks) to protect the shared data structures from simultaneous from parallel DThreads. DDMVM was implemented

*Table 2.4: TFlux DDM implementations.*

| Description     | TFluxSoft  | TFluxHard  |

|-----------------|------------|------------|

| Implementation  | Software   | Hardware   |

| Scheduling      | Static     | Static     |

| Memory Model    | Shared     | Shared     |

| Cache-coherence | Yes        | Yes        |

| Dependences     | Directives | Directives |

in software for a distributed system (DDMVM $_d$  [54]) and became the first software distributed implementation of DDM. The scheduling unit was hierarchically distributed to the nodes with one TSU instance on each participating node. To measure the actual overheads and communication costs DDM was implemented on an FPGA unit. DDMVM $_{FPGA}$  [19] is the first implementation of DDM on real hardware with a TSU connected on the bus of the processor for communicating with the cores of the system. DDMVM $_{FPGA}$  also uses shared memory for storing data but as the entire system is implemented in hardware, no cache-coherence mechanism is needed.

### 2.3 The TFlux Platform

The TFlux Platform [18] is another system implementation of the DDM model that was developed with both software (TFluxSoft) and hardware (TFluxHard) implementations for the scheduling unit. It uses the shared-memory model and follows a static scheduling policy for assigning DThreads to the execution kernels. TFlux is the first DDM implementation of a SMP system on commodity hardware and the first to implement a more user-friendly programming interface with compiler pragmadirectives. As shown in Table 2.4, both TFlux implementations use static assignment of DThreads, while they dynamically monitor dependences resolution and release ready DThreads for execution. Both use a centralized scheduling unit and require hardware cache-coherence in order to provide a safe execution environment.

TFlux is a complete platform that includes a programming environment for DDM applications using compiler directives, a source-to-source preprocessor that translates the application augmented with the directives into DDM parallel code and a TSU that handles the Data-flow execution of the DThreads at runtime. An important advantage of TFlux is that it is not built for a specific machine but rather

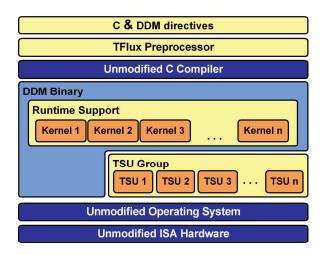

Figure 2.1: The layered design of the TFlux system [18].

works as a virtualization platform for DDM program execution on a variety of computing systems. Figure 2.1 shows the layered design of the TFlux system. To abstract details of the underlying hardware, the programmer uses only the top layer to develop DDM applications.

TFlux also requires a TSU to enforce the Data-flow execution of the DThreads. The TSU loads the SG of a DDM application, initiates and schedules the execution of all DThreads in a Data-flow manner, according to the dependences described by the SG. In the first implementation of DDM, the  $D^2NOW$  [9], each processor needed to have its own private TSU since the execution nodes were independent machines. In the TFlux implementation the TSUs were unified in a single unit named the TSU Group. This unit is logically split in n+1 parts. One part per core (totaling n) for the core's own TSU operations and one common part which is located on a dedicated core and manages the common operations of the TSU for all cores.

In addition it is necessary to define the inputs and outputs of a thread or the producer and consumer relationships between the DThreads in order for the TFlux preprocessor to produce the SG of the application and print the parallel source. The TSU also manages the counters that control the firing of threads. Each time a producer thread terminates its execution, the consumer's counter is decremented by one. When the counter reaches zero, all needed results have been produced and thus the thread is ready for execution. All these operations are part of the TFlux runtime system, which includes all data structures required to manage the thread scheduling as well as the scheduling code itself. In TFluxHard, the TSU is implemented as a separate unit attached to the processor, while in TFluxSoft the execution of the TSU

*Table 2.5: TFlux DDM pragma directives [55].*

| DDM Pragma Directives                                                                | Description                                             |  |

|--------------------------------------------------------------------------------------|---------------------------------------------------------|--|

| #pragma ddm startprogram                                                             | Define the start and the end of a DDM program           |  |

| #pragma ddm endprogram                                                               | Define the start and the end of a DDM program           |  |

| #pragma ddm block ID                                                                 | Define the start and the end of a block of threads with |  |

| #pragma ddm endblock                                                                 | identifier ID                                           |  |

| <pre>#pragma ddm thread ID kernel NUMBER import(VAR : FROM) export(type : VAR)</pre> | Define the boundaries of a DDM thread with              |  |

| #pragma ddm endthread                                                                | identifier ID and the kernel NUMBER                     |  |

| <pre>#pragma ddm for thread ID depends(ID)</pre>                                     | Define the boundaries of a DDM loop thread with         |  |

| #pragma ddm endfor                                                                   | identifier ID                                           |  |

| #pragma ddm kernel NUMBER                                                            | Declare the number of kernels to be used                |  |

| #pragma ddm var TYPE NAME                                                            | Declare a shared variable with NAME and TYPE            |  |

| #pragma ddm private var TYPE NAME                                                    | Declare a private variable with NAME and TYPE           |  |

is explicitly handled by one core of the multi-core system.

## 2.3.1 TFlux Programming Tool-chain

DDM applications in TFlux are developed using ANSI-C with pragma compiler directives [55]. The directives are used to define the code of the DThreads and to express the dependences between them. This section presents the programming style for developing DDM application with TFlux. This is supported by the DDM C Pre-Processor (DDMCPP) [55] that is included in the TFlux Platform. The main objective of the directives is to allow the programmer to define the boundaries, the type and the dependences of all DThreads in a DDM application.

Table 2.5 shows the most relevant directives used to write a DDM program. A simple thread is defined by enclosing its code in a #pragma ddm thread and a #pragma ddm endthread. These directives mark the start and the end of a thread and also define its unique identifier. Because TFlux supports a static scheduling technique, the programmer must also define the kernel that each thread will execute on. The definition of loops is supported in a similar way. By enclosing the code of a for loop in #pragma ddm for and #pragma ddm endfor directives, all iterations of the loop will be executed in parallel. The kernel construct is not necessary in loop threads as iterations will be evenly distributed to all participating kernels.

In order for the runtime system to know when a thread is ready for execution a counter variable is kept that denotes the number of consumers a thread is waiting upon being scheduled for execution. This counter is called *readycount*. For TFlux implementations (TFluxSoft and TFluxHard) this field is not mandatory, as the number of consumers will be automatically inferred by the declaration of the

Table 2.6: DDMVM pragma directives extensions [13].

| DDMVM <sub>s</sub> Constructs                                      | Description                                                        |  |

|--------------------------------------------------------------------|--------------------------------------------------------------------|--|

| kernel(SCHED_POLICY:SCHED_VALUE)                                   | Define the scheduling policy that the specified thread will follow |  |

| arity NUMBER                                                       | Define the number of nested loops that a thread represents         |  |

| readycount NUMBER                                                  | Explicitly define the number of consumers of thread                |  |

| update(THREAD_ID:START:END)                                        | Update the ending threads' consumers                               |  |

| <pre>import(address:size:flag:expression:reference_variable)</pre> | Define the variables that will be imported in a thread             |  |

| <pre>export(address:size:flag:expression:reference_variable)</pre> | Define the variables that will be exported by a thread             |  |

#### explicit dependences.

To define the producer/consumer relationships between threads in a DDM application the data that the threads consume and produce must be considered. Using the import and export statements on a thread directive the preprocessor will know which variables each thread will consume and produce. Thus, it will automatically create a dependence between the thread that produced the declared variable and the thread that will consume it. In some cases expressing the data dependences through the produced and consumed data is not possible, such as arrays elements. To explicitly define dependences between threads the depends construct is used. This construct denotes the producers of a thread. Note that for a loop thread only the depends statement can be used to define the producers of that loop.

Any type of thread in a DDM program must be enclosed in a DDM block at all times. This can be done by enclosing the definitions of threads in a set of #pragma ddm block and #pragma ddm endblock directives. Any number of blocks can be used. The threads within a block will be executed in parallel as long as the dependences among them allow it but blocks are strictly executed sequentially between them. To define a complete DDM program all DDM blocks must be enclosed in a pair of #pragma ddm startprogram and #pragma ddm endprogram directives. Finally, before executing the preprocessor to create the DDM application, the user must also define the number of kernels that will be used in the execution using the #pragma ddm kernel directive.

#### **Support for DDMVM systems**

Table 2.6 shows the extensions developed in the DDMCPP [55] in order to support the DDMVM<sub>s</sub> and the DDMVM<sub>FPGA</sub> systems. In the DDMVM implementations the kernel parameter is a pair of numbers that defines the scheduling policy the programmer wants to use on the specific thread and a value that might be needed,

depending on the scheduling policy used. The kernel statement in DDMVM is also used in a loop thread as to define the scheduling policy that the user wishes to apply on the execution of the loop iterations. The arity parameter describes the depth of the nested loops that are to be parallelized. Currently this is used on the declaration of a simple thread while the user removes the for loop statements from the code and only keeps the body of the loop. This parameter is used to expand the parallelism to the internal loops in the case of nested loops.

In contrast to TFlux implementations, in DDMVM the user declares the consumers of a thread (either simple or loop). This is done using the update statement on the #pragma ddm endthread and the #pragma ddm endfor directives. The START and END parameters are used to update multiple iterations of the consumer loop. The import and export directives have the same meaning as in TFlux, with the difference that in DDMVM you are also allowed to use expressions as to whether you will import or export a specific variable.

More details on the DDMVM $_s$  and DDMVM $_{FPGA}$  runtime systems and application examples can be found in [19,53].

# 2.4 Transactional Memory

Transactional Memory (TM) [56] is a model for manipulating mutable shared data which attempts to reduce complexity by eliminating the need for explicit synchronization. It works by allowing the programmer to specify that certain sections of a program must be executed atomically but without the need to consider any of the synchronized control that might be required. Execution of atomic sections takes place optimistically, that is with an assumption that any shared data within the section will not be changed by any other concurrent execution. If such a conflict does occur, the underlying runtime system ensures that only one execution succeeds while others are transparently re-executed. This leads to the important property of isolation. A thread always proceeds as though it has exclusive access to any shared data within an atomic section. All synchronization complexity is removed and it is unnecessary to serialize accesses to achieve correct execution. Although, in practice, some serialization may occur due to the resolution of conflicts, the optimistic nature of the model ensures that maximal parallelism is achieved. Although TM was originally proposed to reduce the complexity in the context of conventional threaded

programming languages, the isolation property makes it an ideal way of introducing mutable state into Data-flow or functional approaches.

A common example used for motivating TM illustrates the need for mutable shared state [57]. Consider a computation which is trying to perform concurrent credit/debits between bank accounts. Firstly, the state is fundamental to the problem. The account balances must be globally accessible variables which can be updated and persist. The credit/debit operations must be atomic to preserve the overall correctness of the balances. Assuming that we do not know the identity of the accounts when specifying the problem, it is clear that the accounts might overlap and conflicts could occur. A conventional locking approach would need to deal with the cases where overlap might occur by taking explicit locks and dealing with complex interactions such as deadlock. The problem could, of course, be greatly simplified by serializing all the operations but this would defeat the desire to exploit parallelism. However, in many cases, there will be no overlap and an optimistic approach can proceed with maximal parallelism. We can envisage a Data-flow solution where threads have been generated to perform calculations on each account using a purely functional approach and then invoking a transaction to perform a balance transfer. Any number of such threads can be generated to operate in parallel without any need to consider how they interact.

# 2.5 Many-core Hardware

The inclusion of multiple cores in the same chip has become the de-facto standard for the processor architecture. This multi-core approach has resulted as a solution to the power- and complexity-walls of previous monolithic single core processors. The need to optimize performance per watt combined with the continuous advances in technology results in an increase of the need for more cores in processor chips [15]. To retain the power-performance efficiency to an acceptable level we are currently exploring large-scale parallel processing as the way to scale performance. Consequently, in order to exploit the software parallelism and optimize the performance per watt, the trend today is to include more cores in a single die resulting in what is known as many-core processors [15].

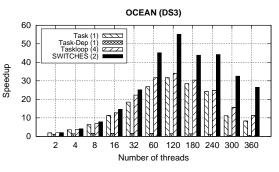

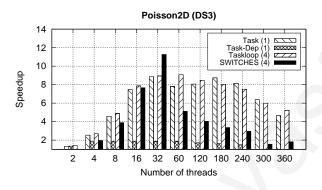

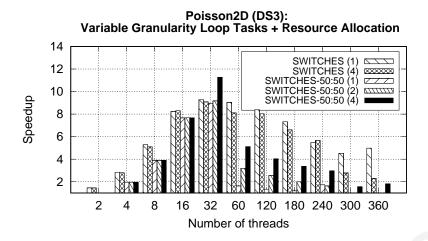

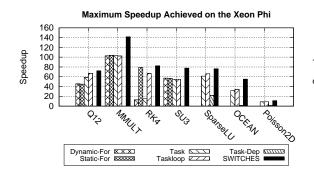

Today we observe two major trends of hardware designs for general purpose many-core processors: cache-coherent, shared-memory and distributed-memory, clustered architectures. Each architecture has different characteristics that target different application domains. There are also various parallel programming systems today that are used to develop parallel applications, both shared- and distributed-memory. The latter has proven to be a good solution for large clustered systems but memory-demanding process-based execution, non-trivial message-passing programming style and high cost for fine-grain parallelism prohibit their use on single-chip many-core processors. Shared-memory programming systems achieve good performance results on multi-cores but little evaluation exists on a many-core processor. In addition, most software systems require cache-coherence to work correctly but some works [7, 8] show that scaling hardware coherence on future many-core processors may be an issue for performance and network traffic. It also requires a significant amount of chip area to implement and will increase the complexity of the hardware to levels that the time for validation is increased substantially [58].