# DEPARTMENT OF COMPUTER SCIENCE

# Improving the Performance of Single and Multi-Application Workloads on Heterogeneous Clustered Many-Core Platforms

**Panayiotis Petrides**

A Dissertation Submitted to the University of Cyprus in Partial

Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

May, 2018

© Panayiotis Petrides, 2018

## VALIDATION PAGE

Doctoral Candidate: Panayiotis Petrides

**Doctoral Dissertation Title:** Improving the Performance of Single and

Multi-Application Workloads on Heterogeneous Clustered Many-Core Platforms

The present Doctoral Dissertation was submitted in partial fulfillment of the requirements for the Degree of Doctor of Philosophy at the Department of Computer Science and was approved on the **May 4, 2018** by the members of the Examination Committee.

#### **Examination Committee:**

Research Supervisor:

Associate Professor Pedro Trancoso

Committee Member:

Professor Constantinos Pattichis

Committee Member:

Professor Paraskevas Evripidou

Committee Member:

Professor João Cardoso

Committee Member:

Professor Dimitris Gizopoulos

# **DECLARATION OF DOCTORAL CANDIDATE**

The present Doctoral Dissertation was submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy of the University of Cyprus. It is a product of original work of my own, unless otherwise mentioned through references, notes, or any other statements.

...... [Full Name of Doctoral Candidate]

..... [Signature of Doctoral Candidate]

# Περίληψη

Τα τελευταία χρόνια οι αρχιτεκτονικές επεξεργαστών έχουν αναπτυχθεί προς την κατεύθυνση των πολλαπλών πυρήνων, με αποτέλεσμα την βελτίωση της επίδοσης τους αποφεύγοντας ταυτόχρονα τους περιορισμούς από την κατανάλωση ενέργειας. Ο αυξανόμενος αριθμός πυρήνων σε ένα ολοκληρωμένο κύκλωμα δεν προσφέρει μόνο τα πλεονεκτήματα της δυνητικής μαζικής παραλληλίας αλλά ταυτόχρονα δίνει την δυνατότητα στους κατασκευαστές να εξερευνήσουν νέες αρχιτεκτονικές, όπως την ενσωμάτωση στο ίδιο ολοκληρωμένο κύκλωμα πυρήνων διαφορετικών χαρακτηριστικών. Τα οφέλη αυτών των αρχιτεκτονικών συνοδεύονται όμως και με προκλήσεις.

Ο αυξανόμενος αριθμός πυρήνων σε μια πολυπύρηνη αρχιτεχτονιχή μπορεί να τύχει εκμετάλλευσης από εφαρμογές με υψηλό βαθμό παραλληλίας. Η μεταφορά μιας εφαρμογής σε αυτού του είδους τις αρχιτεχτονιχές δεν είναι μια απλή διαδιχασία αλλά μια ευρύτερη εργασία που λαμβάνει υπόψιν τόσο την αρχιτεχτονιχή του συστήματος όσο και τα χαραχτηριστιχά της εφαρμογής. Ως μελέτη περίπτωσης (case study), χρησιμοποιήθηχαν εφαρμογές συστημάτων υποβοήθησης λήψης αποφάσεων (Decision Support System), οι οποίες μεταφέρθηχαν σε αρχιτεχτονιχή πολλαπλών πυρήνων χρησιμοποιώντας την χοινή ενσωματωμένη στο χύχλωμα μνήμη (on-chip shared memory) για την προεπεξεργασία δεδομένων (prefetching buffer). Τα αποτελέσματα δείχνουν ότι όταν οι αιτήσεις για δεδομένα αντιμετωπίζονται ιχανοποιητιχά τότε γίνεται εχμεταλλεύσιμη χαι η παραλληλία των εφαρμογών.

Ενώ κάποιες εφαρμογές επωφελούνται από τον αυξανόμενο αριθμό παράλληλων πυρήνων, σε πολλές περιπτώσεις η χρήση πολυπύρηνων επεξεργαστών στοχεύει στην παράλληλη εκτέλεση πολλαπλών εφαρμογών. Αυτό μπορεί να οδηγήσει σε παρεμβολές μεταξύ των υπό εκτέλεση εφαρμογών. Για την αντιμετώπιση αυτής της πρόκλησης, προτάθηκε μια απλή και μη παρεμβατική προσέγγιση χρησιμοποιώντας τεχνολογία εικονικοποίησης (virtualization techniques) στον ίδιο επεξεργαστή. Οι διαφορετικές εικονικές μηχανές μπορούν να θεωρηθούν ως Τομείς Επίδοσης (Performance Domains) προσφέροντας προβλεψιμότητα επίδοσης για τις διάφορες εφαρμογές. Τα πειραματικά αποτελέσματα δείχνουν ότι επιτυγχάνεται απομόνωση της εκτέλεσης των εφαρμογών σε ένα εικονικοποιημένο περιβάλλον και ταυτόχρονα μειώνονται οι παρεμβολές μεταξύ των εφαρμογών.

Οι μελλοντικοί επεξεργαστές πολλαπλών πυρήνων μεγάλης κλίμακας αναμένεται να είναι μια συλλογή συμπλεγμάτων ετερογενών πυρήνων για να ικανοποιήσουν τις απαιτήσεις των εφαρμογών. Προκειμένου να ικανοποιηθεί η δυναμική συμπεριφορά των εφαρμογών, προτείνεται ένα σύστημα χρόνου εκτέλεσης (run time system) το οποίο είναι υπεύθυνο για την εύρεση ενός καλύτερου πόρου που ταιριάζει σε μια εφαρμογή σε κάθε διαφορετική φάση της εκτέλεσής τους. Ο προτεινόμενος ετερογενής χρονοπρογραμματιστής (scheduler) αξιολογήθηκε τόσο σε πραγματική αρχιτεκτονική πολλαπλών πυρήνων (Intel SCC48 πυρήνων) όσο και με τη χρήση προσομοιωτή (Sniper) για εφαρμογές από τη σουίτα αναφοράς SPEC CPU2006. Τα αποτελέσματα δείχνουν ότι η μεταφορά εφαρμογών σε πυρήνες που ταιριάζουν καλύτερα στις απαιτήσεις τους, οδηγούν σε μείωση του χρόνου εκτέλεσης τους μεταξύ 15% και 36% σε σύγκριση με τυχαίο στατικό χρονοπρογραμματισμό.

Δεδομένης της αυξανόμενης πολυπλοκότητας και πολυμορφίας των πυρήνων του επεξεργαστή, καθώς και των απαιτήσεων της εφαρμογής, θα χρειαστεί η ανάπτυξη περισσότερων από τις προαναφερόμενες τεχνικές για την αντιμετώπιση των προκλήσεων. Επομένως, οι μελλοντικοί ετερογενείς επεξεργαστές πολλαπλών πυρήνων θα πρέπει να περιλαμβάνουν ένα στρώμα εικονικοποίησης το οποίο θα μπορούσε να αποτελείται από όλες τις προτεινόμενες τεχνικές αλλά και άλλες με ένα αρθρωτό τρόπο ούτως ώστε να υποστηρίζει και πυρήνες που αλλάζουν δυναμικά τα χαρακτηριστικά τους.

iv

## Abstract

In recent years processor architectures have evolved towards chips with multiple cores, thus delivering the expected performance while avoiding the power wall. Increasing the number of devices on a chip will not only offer the benefit of increasing the potential for parallelism but will also allow manufacturers to explore new designs such as including in the same chip cores of different characteristics. The benefits will come also with challenges in exploiting the performance both for single and multiapplication workloads.

The increasing number of cores on a clustered many-core architecture can be exploited by applications with high degree of parallelism. Porting an application for such architectures is not trivial but a joint task of considering both the underlying architecture and the applications' behavior. Memory-bound applications with high degree of parallelism can create an increasing number of memory requests, which must be satisfied without becoming a performance bottleneck. As a case study, a Decision Support System (DSS) workloads was ported to a clustered manycore architecture and the on-chip memory, shared among all cores, was used as a prefetching buffer. The results show that parallelism can be well exploited when the memory requests are well handled.

While some applications benefit from the increasing number of parallel cores, in many cases the use of many-core processors will be for the co-execution of multiple applications. This might happen because of the limited degree of parallelism of the applications or in order to achieve higher throughput and resource utilization. Nevertheless, this can lead to application interference. To address this, a simple and non-intrusive approach using virtualization on the same processor was proposed. The different Virtual Machines can be seen as Performance Domains since the isolation offers performance predictability for the different applications. The experimental results show that the performance overhead of executing on a virtualized environment is not significant.

While Performance Domains provide isolation, they are static containers that do not adapt well to the dynamic behavior of applications. Future large-scale manycore processors are expected to be organized as a collection of NUMA clusters of heterogeneous cores as to satisfy applications demands. In order to satisfy the applications' dynamic behavior, a runtime system (monitor and scheduler), is proposed. This system is responsible for finding a best matching resource for an application at a certain execution phase. The proposed heterogeneous and NUMA-aware scheduler was evaluated both on a real many-core architecture (48-core Intel SCC) and using a simulator (Sniper) for workloads composed of applications from the SPEC CPU2006 benchmark suite. The results indicate that even when all cores are busy, migrating processes to cores that match better the requirements of applications results in a reduction of the execution time between 15% and 36% compared to a random static scheduling.

Given the increasingly complexity and diversity in the hardware resources, as well as the application demands, more and more of the above-mentioned techniques should be developed to address the challenges. Therefore, the vision is for future heterogeneous many-core processors is to include a virtualization layer which could be composed of all of the proposed techniques and others in a modular way and thus also be able to even support hardware that changes dynamically at runtime.

vi

# Acknowledgments

A long journey full of experiences and knowledge has been completed. A journey that provided me with knowledge not only in the field of this thesis, but also knowledge and experience of how to overcome difficulties and how to get the most of each experience. This journey would have never been completed without the continuous support and believe in this work by my advisor, Pedro Trancoso. His contribution and advice were valuable both in terms of completing this thesis but also to help overcoming the difficulties and challenges which this road was full of. Thank you for believing in this journey and holding the compass as my mentor.

The ones I owe the most of appreciation and I am thankful for believing in me are my parents, Petros and Eleni. I thank you for being in my life and providing me with your advices and support. I am grateful of having you in my life and with your own way are supporting me not only during this journey but to my whole life.

Also I wanted to thank my two sisters, Irene and Katerina. With your support and help you helped to this journey each one with your own way. Your help was continuous and valuable to me.

A big thank you to a special person in my heart, Eleni. I could see in your eyes your believe of succeeding through this journey and I can assure you that it was of the greatest help. Thank you for your patience, your support and your love.

I also wanted to thank two little guys. Chuck and Bass. You both changed my world and taught me how to become a better person. I will always be grateful for the time spent together and your unconditional devotion.

Finally, I wanted to thank all the CASPER group members that I have had the

pleasure to work together, Kyriakos, Demos, Marios, Andreas and Constantinos. Our collaboration means a lot and my memories from CASPER group will accompany me.

To everybody at the Department of Computer Science, thank you for the excellent cooperation all these years. Special thanks to Melina and Savvoula and to the IT team, Savvas and Maria for providing all the support and even more.

Rayours

# Contributions of this Thesis

#### Conference and workshop proceedings:

- 1. **P. Petrides** and P. Trancoso. *"Heterogeneous- and NUMA-aware Scheduling for Many-core Architectures"*, in Proceedings of the 10th ACM International Systems and Storage Conference (SYSTOR 2017), pp. 2:1-2:12, Haifa, Israel, May 2017.

- 2. **P. Petrides** and P. Trancoso. *"Addressing the Challenges of Future Large-Scale Many-core Architectures"*, in Proceedings of the ACM International Conference on Computing Frontiers (CF '13), pp. 1-4, Ischia, Italy, May 2013.

- 3. **P. Petrides**, A. Diavastos, C. Christofi, and P. Trancoso. *"Scalability and Efficiency of Database Queries on Future Many-Core Systems"*, in Proceedings of the 21st IEEE Euromicro international Conference on Parallel, Distributed, and Network-Based Processing (PDP), pp. 24-28, February 2013.

- 4. **P. Petrides**, G. Nicolaides and P. Trancoso. "*HPC Performance Domains on Multicore Processors with Virtualization*", in Proceedings of the 25th International Conference on Architecture of Computing Systems (ARCS 2012), pp. 123-134, Munich, Germany, February 2012.

- 5. **P. Petrides**, A. Diavastos, and P. Trancoso. *"Exploring Database Workloads on Future Clustered Many-Core Architectures"*, in Proceedings of the 3rd Many-core Applications Research Community Symposium (MARC 2011), Ettlingen, Germany, July 2011.

- 6. **P. Petrides**, F. Pratas, L. Sousa, and P. Trancoso, *"Virtualization for Morphable Multi-Cores"*, in Proceedings of the 2nd Workshop on Parallel Programming and Run-Time Management Techniques for Many-core Architectures (PARMA 2011), Lake Como, Italy, February 2011.

#### **Technical reports:**

- 7. **P. Petrides**, F. Pratas, L. Sousa, P. Trancoso. *"Exploiting Location-Aware Task Execution on Future Large-scale Many-core Architectures"*, University of Cyprus Technical Report TR-12-4, Computer Science Department, on May 24, 2012.

- 8. **P. Petrides**, F. Pratas, L. Sousa, P. Trancoso, *"Virtualization for Morphable Multi-Cores"*, HiPEAC Technical Report, TR-HiPEAC-0013, July 2010.

# Contents

| 1 | Intr | oductio | on                                                             | 1        |

|---|------|---------|----------------------------------------------------------------|----------|

|   | 1.1  | Motiv   | vation                                                         | 1        |

|   | 1.2  | Proble  | em Statement                                                   | 2        |

|   |      | 1.2.1   | Applications Parallelism                                       | 3        |

|   |      | 1.2.2   | Performance Domains                                            | 3        |

|   |      | 1.2.3   | Clustered Many-Core Architectures                              | 4        |

|   |      | 1.2.4   | Modular Virtualization Layer                                   | 5        |

|   | 1.3  | Thesis  | s Statement                                                    | 6        |

|   | 1.4  | Objec   | tives and Contributions                                        | 6        |

|   |      | 1.4.1   | Goal                                                           | 6        |

|   |      | 1.4.2   | Objective 1: Parallelism on a Clustered Many-Core Architecture | 6        |

|   |      | 1.4.3   | Objective 2: Guarantee Performance                             | 7        |

|   |      | 1.4.4   | Objective 3: Heterogeneous and NUMA-aware Scheduling           | 7        |

|   |      | 1.4.5   | Thesis Vision for the Future                                   | 8        |

| _ | -    |         |                                                                | _        |

| 2 |      |         | load Parallelism on a Clustered Many-Core Architecture         | 9        |

|   | 2.1  |         | vation                                                         | 10       |

|   | 2.2  |         | ed Work                                                        | 11       |

|   | 2.3  |         | SCC Clustered Many-Core Architecture                           | 12       |

|   |      | 2.3.1   | On-Chip Shared Memory                                          | 14       |

|   | 2.4  | Datab   | pase Workloads                                                 | 15       |

|   | 2.5  | Algor   | ithms Implementations                                          | 17       |

|   |      | 2.5.1   | Data-Parallel Sequential Scan (DPSS)                           | 17       |

|   |      | 2.5.2   | Parallel Nested-Loop Join                                      | 17       |

|   |      | 2.5.3   | Hash Join                                                      | 19       |

|   |      | 2.5.4   | Data Prefetching                                               | 20       |

|   | 2.6  | Exper   | rimental Setup                                                 | 21       |

|   | 2.0  | LAPCI   | 1                                                              |          |

|   | 2.0  | _       | rimental Results                                               | 22       |

|   |      | _       | -                                                              | 22<br>22 |

|   | 2.8 | Summary                                                          | 28 |

|---|-----|------------------------------------------------------------------|----|

| 3 | Mu  | lti-Core Performance Domains for HPC Applications                | 30 |

|   | 3.1 | Motivation                                                       | 31 |

|   | 3.2 | Related Work                                                     | 33 |

|   | 3.3 | Virtual Machines, HPC and Performance Domains on Multi-core Pro- |    |

|   |     | cessors                                                          | 34 |

|   | 3.4 | Experimental Setup                                               | 35 |

|   | 3.5 | Experimental Results                                             | 39 |

|   | 3.6 | Summary                                                          | 44 |

| 4 | Het | erogeneous and NUMA-aware Scheduling                             | 48 |

|   | 4.1 | Motivation                                                       | 49 |

|   | 4.2 | Related Work                                                     | 51 |

|   | 4.3 | Challenges of Clustered Many-Core Architectures                  | 54 |

|   |     | 4.3.1 Clustered Many-Core Architectures                          | 54 |

|   |     | 4.3.2 Non-Uniform Memory Latency                                 | 56 |

|   |     | 4.3.3 Asymmetric Cores                                           | 58 |

|   |     | 4.3.4 Aggregate Off-chip Bandwidth                               | 60 |

|   |     | 4.3.5 Understanding and Classifying Applications Behaviour       | 61 |

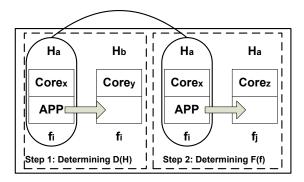

|   | 4.4 | Scheduling Policy                                                | 64 |

|   |     | 4.4.1 Classification Phase                                       | 64 |

|   |     | 4.4.2 Applications Scheduling                                    | 65 |

|   |     | 4.4.3 Implementation Details                                     | 67 |

|   | 4.5 | Experimental Setup                                               | 69 |

|   | 4.6 | Experimental Results on the Intel SCC                            | 70 |

|   | 4.7 | Simulating Clustered Many-core Architectures                     | 74 |

|   |     | 4.7.1 Scaling the Number of Cores within a Cluster               | 74 |

|   |     | 4.7.2 Changing Cores Diversity within a Cluster                  | 76 |

|   | 4.8 | Discussion                                                       | 78 |

|   | 4.9 | Summary                                                          | 79 |

| 5 | Мос | dular Virtualization Layer                                       | 81 |

|   | 5.1 | Motivation                                                       | 81 |

|   | 5.2 | Multi-core Architectures                                         | 83 |

|   |     |                                                                  |    |

|   |     | 5.2.1                                 | Static Multi-core Configurations                 | 83  |

|---|-----|---------------------------------------|--------------------------------------------------|-----|

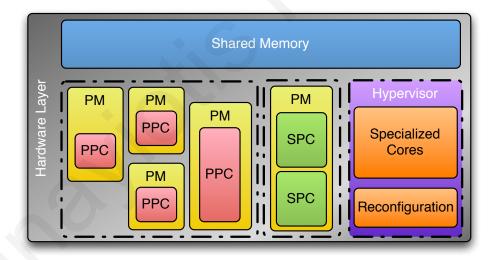

|   |     | 5.2.2                                 | Dynamic Multi-core Configurations                | 86  |

|   | 5.3 | Virtua                                | lization of Morphables Multi-Cores               | 90  |

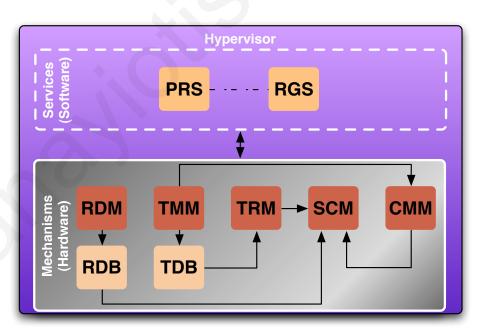

|   |     | 5.3.1                                 | Hypervisor Mechanisms and Services               | 91  |

|   | 5.4 | Integr                                | ration of the Proposed Techniques                | 96  |

|   | 5.5 | Sumn                                  | nary                                             | 97  |

| 6 | Con | clusio                                | ns and Future Work                               | 98  |

|   | 6.1 | Achieved Objectives and Contributions |                                                  |     |

|   | 6.2 | Open Research Questions               |                                                  | 100 |

|   |     | 6.2.1                                 | Direction 1: Machine Learning Algorithms         | 100 |

|   |     | 6.2.2                                 | Direction 2: Dynamic Heterogeneous Many-Cores    | 101 |

|   |     | 6.2.3                                 | Direction 3: Fault-tolerance                     | 101 |

|   |     | 6.2.4                                 | Direction 4: Morphable Many-Cores Runtime System | 102 |

# List of Figures

| 2.1  | Intel SCC Architecture                                                      | 13 |

|------|-----------------------------------------------------------------------------|----|

| 2.2  | Intel SCC Memory Architecture as used by the programmer through             |    |

|      | the RCCE message passing API                                                | 14 |

| 2.3  | TPC-H Q6. The parameters used were: DATE=2005, DISCOUNT=10,                 |    |

|      | and QUANTITY=1000000                                                        | 16 |

| 2.4  | Simplified version of TPC-H Q12. The parameters used were: SHIP-            |    |

|      | MODE1=1, SHIPMODE2=2 and DATE=2009                                          | 16 |

| 2.5  | Simplified version of TPC-HQ3. The parameters used were: DATE=2007          | ,  |

|      | and SEGMENT=3                                                               | 17 |

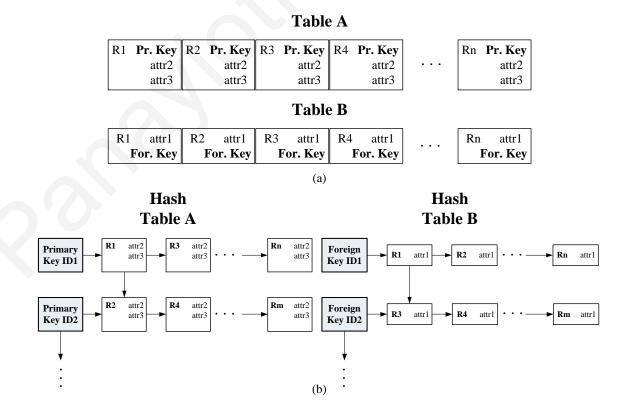

| 2.6  | Table A: (a) logical and (b) physical data organization for parallel        |    |

|      | nested-loop join operation.                                                 | 18 |

| 2.7  | Table A: (a) logical and (b) physical data organization for hash join       |    |

|      | operation.                                                                  | 18 |

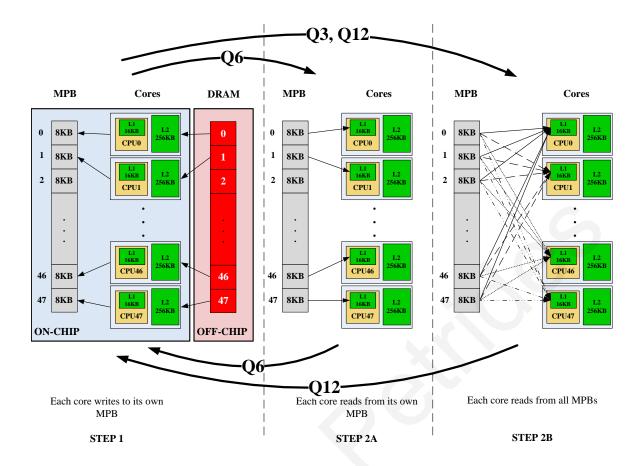

| 2.8  | Description of data prefetching using the MPB                               | 19 |

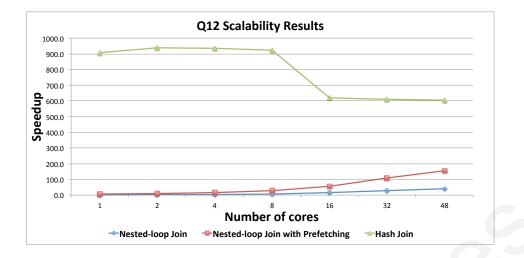

| 2.9  | Normalized scalability of Q12 query.                                        | 23 |

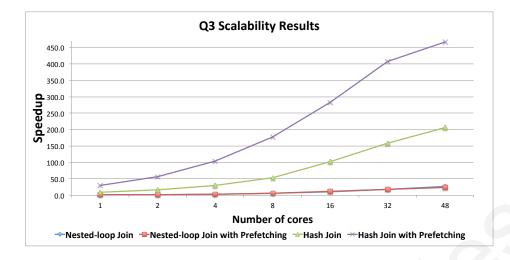

| 2.10 | Normalized scalability of Q3 query                                          | 24 |

| 2.11 | Data-parallel sequential scan (Q6) normalized execution time and            |    |

|      | breakdown.                                                                  | 25 |

| 2.12 | Normalized power-performance efficiency of Q3 query                         | 26 |

| 2.13 | Normalized power-performance efficiency of Q12 query                        | 27 |

| 2.14 | Normalized power-performance efficiency of Q6 query                         | 28 |

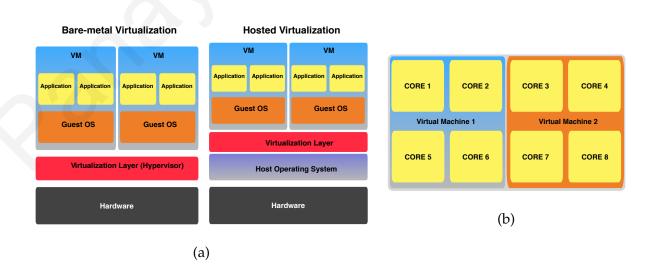

| 3.1  | (a) Virtualization techniques bare-metal and hosted and (b) perfor-         |    |

|      | mance domains on a multi-core system.                                       | 34 |

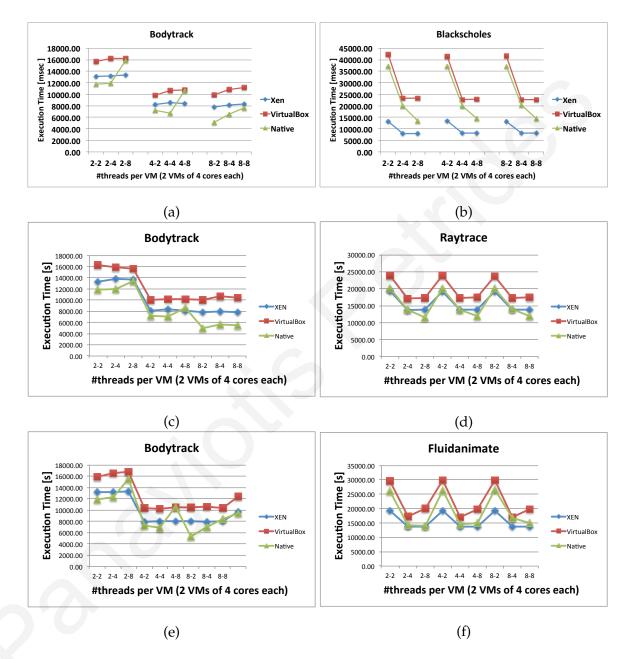

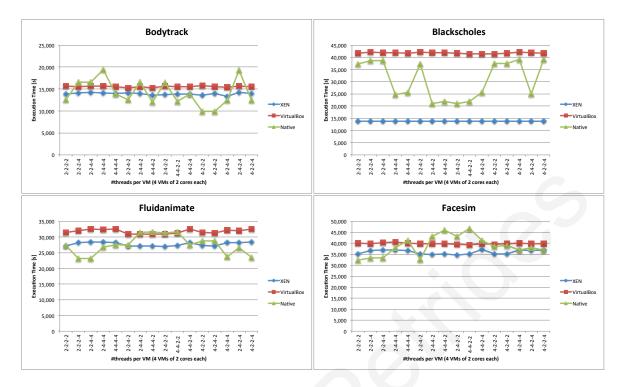

| 3.2  | Execution Variance on VirtualBox Native and Xen for: Scenario 1 (a)         |    |

|      | and (b), Scenario 2 (c) and (d), Scenario 3 (e) and (f).                    | 40 |

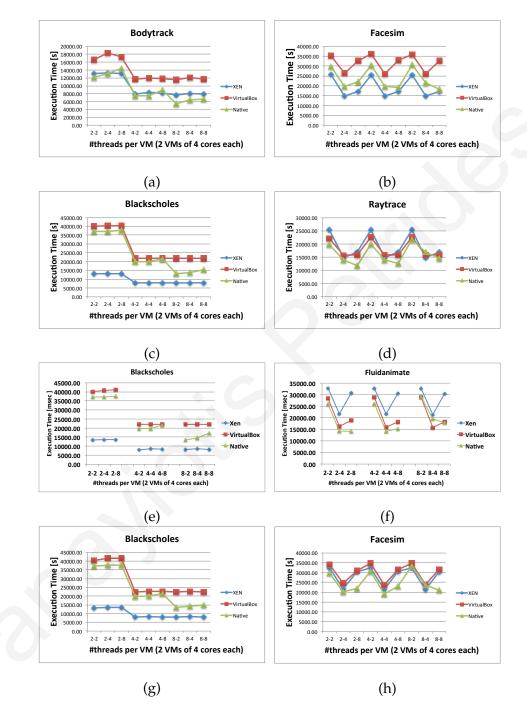

| 3.3  | Execution Variance on VirtualBox Native and Xen for: Scenario 4 (a)         |    |

|      | and (b), Scenario 5 (c) and (d), Scenario 6 (e) and (f), Scenario 7 (g) and |    |

|      | (h)                                                                         | 41 |

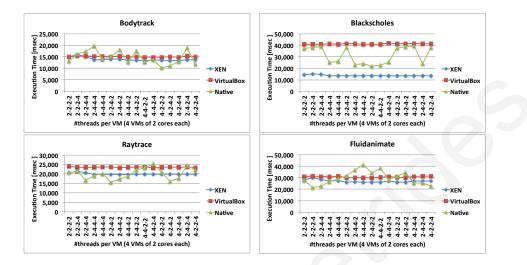

| 3.4  | Execution Variance on VirtualBox Native and Xen for Scenario 8              | 43 |

| 3.5  | Execution Variance on VirtualBox Native and Xen for Scenario 9                | 44 |

|------|-------------------------------------------------------------------------------|----|

| 3.6  | Execution Variance on VirtualBox Native and Xen for Scenario 10.              | 45 |

| 3.7  | Execution Variance on VirtualBox Native and Xen for Scenario 11.              | 45 |

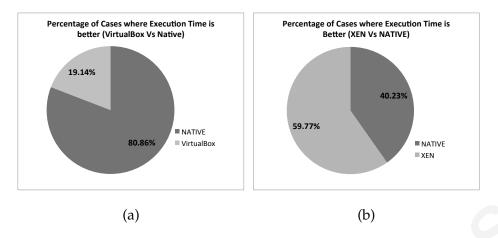

| 3.8  | Performance comparison between: (a) VirtualBox and Native Execu-              |    |

|      | tion and (b) Xen and Native Execution.                                        | 46 |

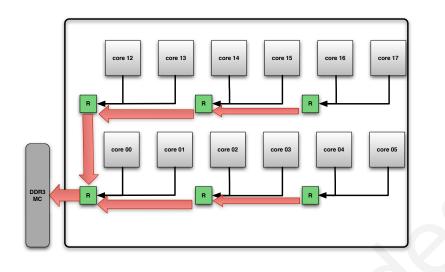

| 4.1  | Cluster of a Many-Core Processor. The arrows show the distance                |    |

|      | of a core to the memory controller and their thickness represent the          |    |

|      | accumulated bandwidth on the links.                                           | 50 |

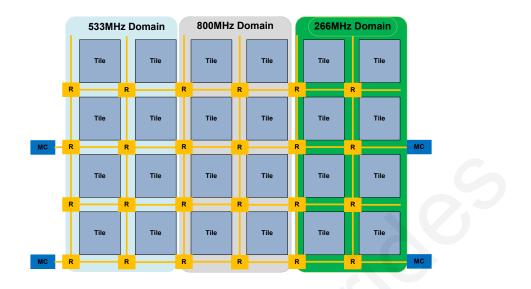

| 4.2  | Core Clock Frequency System Configuration                                     | 55 |

| 4.3  | Core to Memory Controller Distance Model Execution Performance                |    |

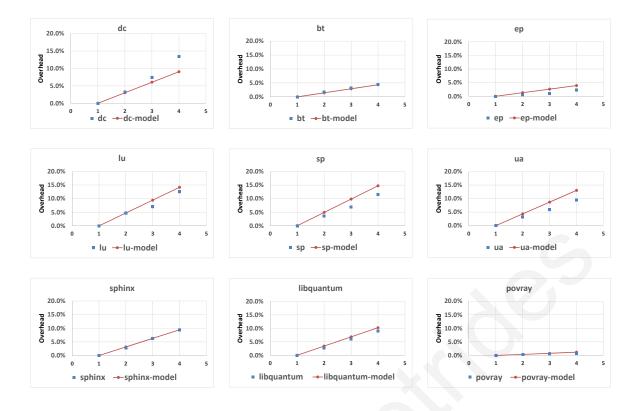

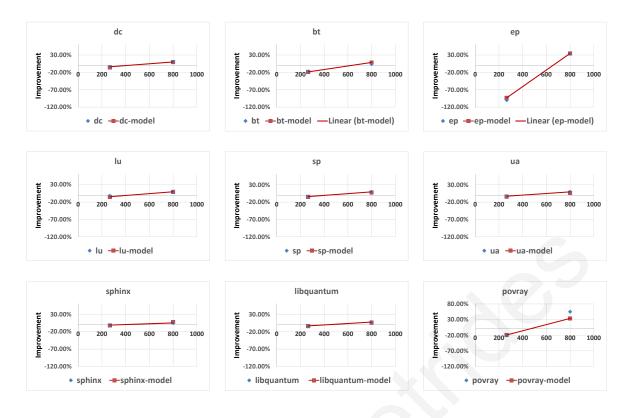

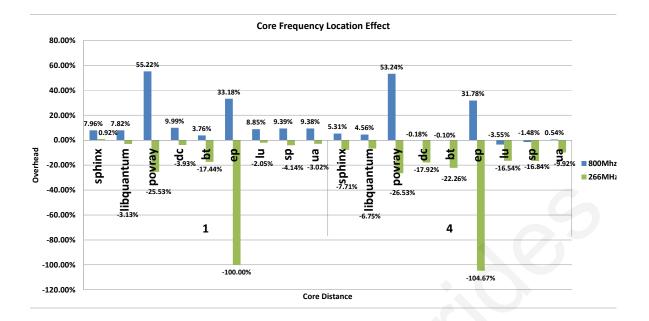

|      | Influence for SPEC and NAS applications.                                      | 57 |

| 4.4  | Core to Memory Controller Distance Effect Simulated Execution Per-            |    |

|      | formance Influence for SPEC applications.                                     | 58 |

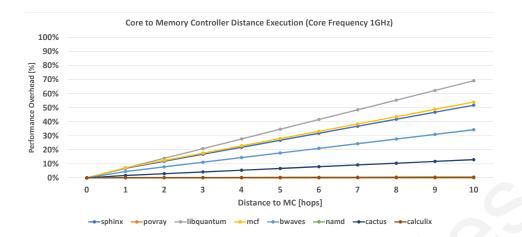

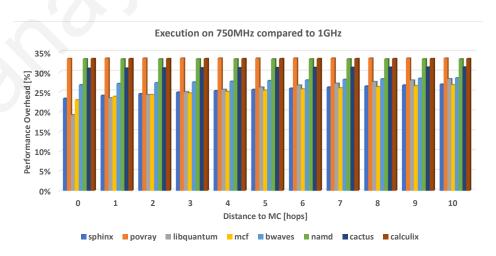

| 4.5  | Non-Uniform Execution Influence for SPEC and NAS applications.                | 59 |

| 4.6  | Core Frequency and Location Effect for Simulated Execution of SPEC            |    |

|      | applications.                                                                 | 59 |

| 4.7  | Core Frequency and Location Effect                                            | 60 |

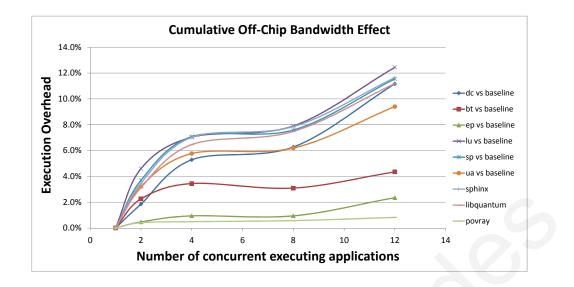

| 4.8  | Cumulative Bandwidth Performance Influence for SPEC CPU2006                   |    |

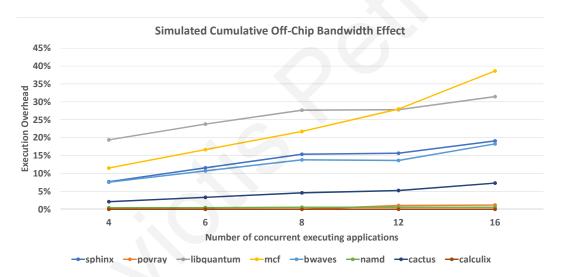

|      | and NAS applications.                                                         | 61 |

| 4.9  | Simulated Cumulative Bandwidth Performance Influence for SPEC                 |    |

|      | CPU2006                                                                       | 61 |

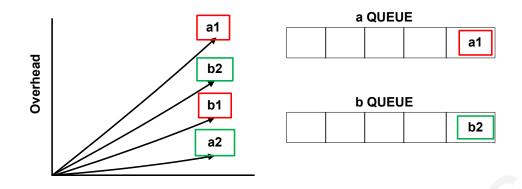

| 4.10 | ) Applications Classification comparing coefficients a and b                  | 64 |

| 4.11 | Applications to Resources Assignment.                                         | 66 |

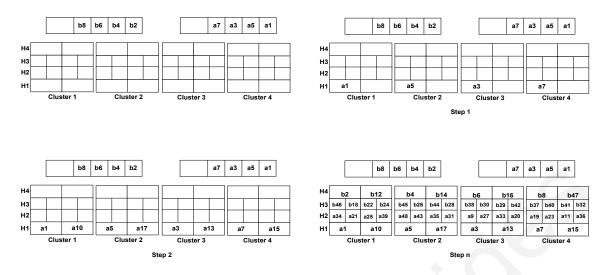

| 4.12 | 2 Classification Steps for Distance and Frequency.                            | 67 |

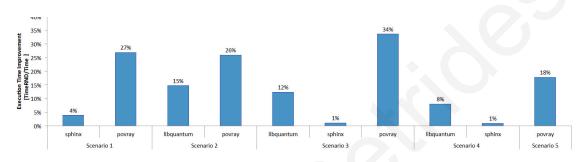

| 4.13 | <sup>3</sup> Proposed Scheduler Execution Time Improvement compared to a Ran- |    |

|      | dom Static Task Assignment Policy                                             | 67 |

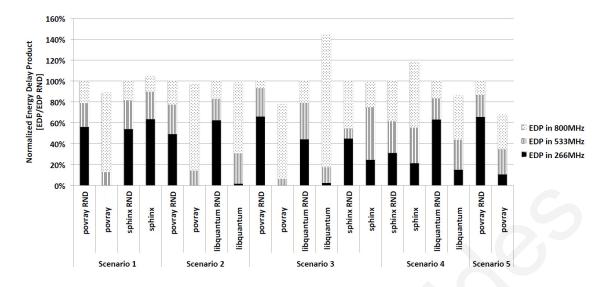

| 4.14 | Energy Delay Product Comparison between a Random Static Assign-               |    |

|      | ment Policy and the Proposed Dynamic Scheduling Policy                        | 73 |

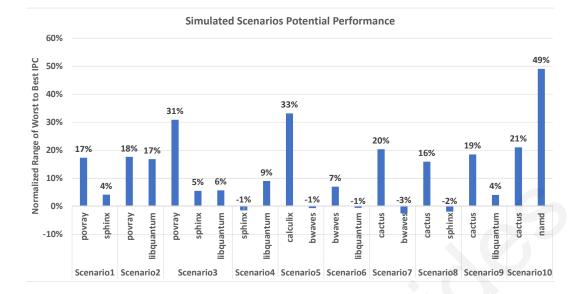

| 4.15 | 5 Simulated Scenarios Potential Performance                                   | 76 |

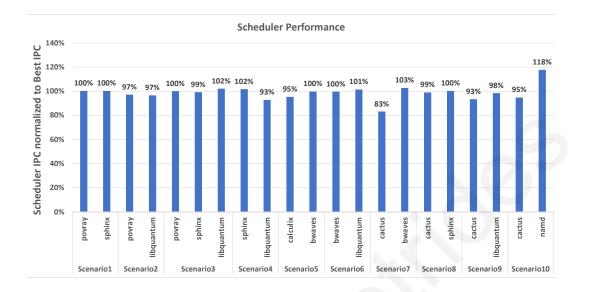

| 4.16 | 5 Simulated Scheduler Scenarios Achieved Performance                          | 77 |

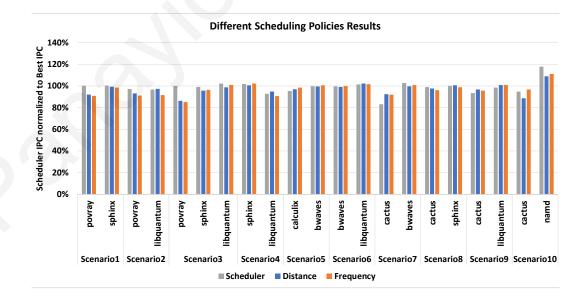

| 4.17 | 7 Different Policies Performance                                              | 77 |

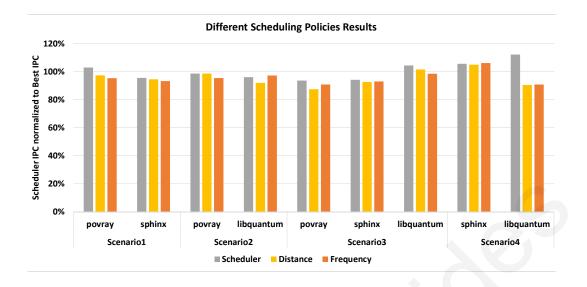

| 4.18 | 3 Different Policies Performance                                              | 78 |

| 5.1  | System layers                                                                 | 83 |

| 5.2 | Classification of Static Architectures                              | 84 |

|-----|---------------------------------------------------------------------|----|

| 5.3 | Static Architecture                                                 | 85 |

| 5.4 | Morphable Architecture and its Components: Private Memory (PM), Se- |    |

|     | quential Processing Core (SPC), Parallel Processing Core (PPC)      | 87 |

| 5.5 | Hypervisor Architecture                                             | 92 |

| 5.6 | Bandwidth demands for short executing applications                  | 93 |

| 5.7 | Bandwidth demands for long executing applications.                  | 93 |

# List of Tables

| 2.1 | TPC-H Queries input sizes.                                        | 22 |

|-----|-------------------------------------------------------------------|----|

| 3.1 | PARSEC Application Description.                                   | 36 |

| 3.2 | Experiments scenarios for 2 and 4 instances of virtual machines.  | 38 |

| 4.1 | Applications classification memory or compute-bound based on co-  |    |

|     | efficients a and b                                                | 63 |

| 4.2 | SPEC CPU2006 Applications Scenarios and Execution Times Variance. | 69 |

| 4.3 | Clustered Many-Core Architectures Environments.                   | 70 |

| 4.4 | Moving memory-bound applications closer to the memory controller, |    |

|     | Scenario 1                                                        | 72 |

| 4.5 | Simulated SPEC CPU2006 Applications Scenarios.                    | 75 |

# Chapter

# Introduction

Achieving high levels of application performance on a many-core architecture environment considering the characteristics of both available resources and applications demands is not a trivial task. Different approaches exist in order to exploit the increasing number of resources and at the same time target on high performance of applications. In particular, one approach is to target single application performance by exploiting its own parallelism while another approach is to target multiple application performance by exploiting throughput parallelism. Both approaches result in different challenges, which are identified as: *(i)* tuning single application performance by considering both many-core underlying resources and application characteristics, *(ii)* minimizing interference between co-executing applications and *(iii)* satisfying the dynamic demands of applications when executing on a clustered heterogeneous many-core environment.

## 1.1 Motivation

The current *de-facto* standard in processor design is the multi-core architecture which emerged as a way to provide at the same time energy efficiency and increasing computing power. Moreover, as technology and on-chip integration keeps evolving, the number of cores per chip tends to increase resulting in what is known as manycore architectures. At the same time, processors start integrating cores of different characteristics and include features to change their characteristics dynamically at runtime as to improve their efficiency. While the increasing number of cores may result in a larger degree of parallelism, improving an application performance by exploiting its parallelism should be a joint task of considering both underlying architecture and applications behavior. Additionally, throughput performance of such systems will raise the challenges of co-executing multiple applications of different demands, both in terms of memory and computational resources, within the same chip. Considering processors evolution, they are becoming very complex systems and as the number of cores increases some features make the execution non-uniform across different cores. Cores grouped into clusters are a way to overcome design complexity but in turn it leads to new challenges. The key for determining the best matching core for a certain application is to find out the application's memory and computational requirements. Given that no previous knowledge of the application is assumed, whenever an application enters the system, it is important to have the mechanisms to acquire enough information about its behaviour in terms of resource requirements. A runtime environment, which considers both application demands and available resources, is needed for hiding the underlying architecture to running applications and at the same time to satisfy applications demands and utilize the available resources.

### 1.2 Problem Statement

As the number of cores increases in a single chip processor, several challenges arise: wire delays, contention for out-of-chip accesses, and core heterogeneity. In order to address these issues and satisfy the demands of the applications, future large-scale many-core processors are expected to be organized as a collection of Non-Uniform Memory Accesses (NUMA) clusters of heterogeneous cores. The work in this thesis is focused on many-core clustered architectures and more specifically to study: *(i)* how to achieve single application performance by exploiting the underlying architecture characteristics, *(ii)* resource isolation by forming performance domains which will guarantee applications performance and *(iii)* satisfy applications dynamic behavior on heterogeneous clustered many-core architecture. To address these issues but at the same time achieve high levels of applications performance in a clustered many-core architecture it is essential to answer the questions presented in the following sections.

#### **1.2.1** Applications Parallelism

The increasing number of cores on a clustered many-core architecture can be exploited by applications with high degree of parallelism resulting in performance improvement. Porting an application for such architectures is not a trivial task but a joint task of considering both underlying architecture and application behavior. Memory-bound applications with high degree of parallelism can create an increasing number of memory requests, which must be satisfied without becoming a performance bottleneck. Decision Support System (DSS) workloads are known to be one of the most time-consuming database workloads that process large data sets. Traditionally, DSS queries have been accelerated using large-scale multiprocessors. Clustered many-core architectures provide specific benefits which could be exploited in order to achieve high levels of performance of such workloads. Different implementations of these workloads result on different performance, therefore architecture characteristics should be considered to achieve high levels of performance. In addition, enhancements of such architectures, *i.e.* on-chip memory shared among all cores, could be used as a prefetching buffer resulting on further improvement of the performance for such workloads.

**Research Question 1:** How is it possible to achieve high levels of scalability and efficiency of memory demanding applications exploiting many-core architecture characteristics?

#### **1.2.2** Performance Domains

The use of virtualization has traditionally been as to divide the physical machine into different domains for three major purposes. First, to allow the installation of different Operating Systems (OS) on the same machine. Second, to provide isolation between users logged on to the different domains. Third, to improve the overall system utilization by offering more virtual processors than the ones available physically. The objective of virtualization was the better management of the complex underlying hardware as well as improving the utilization but not compromising on isolation. Nevertheless, these benefits usually come with a price - performance overhead. Obviously, the addition of an intermediate layer between the hardware and the application leads to some performance degradation, which should be minimized.

As the number of cores increases in multi-core processors, more applications execute at the same time. This may lead to interference between the different applications, and consequently a negative impact on their performance. The isolation properties provided by virtualization methods may offer performance predictability for the executed applications by eliminating in some cases the negative effects of coexecution interference. Therefore, introducing the benefits of applications isolation offered by virtualization techniques on HPC applications can result on performance guarantee and system utilization.

**Research Question 2:** How is it possible to offer performance guarantees for the coexecution of multiple high-performance computing applications on many-core systems without adding significant overheads?

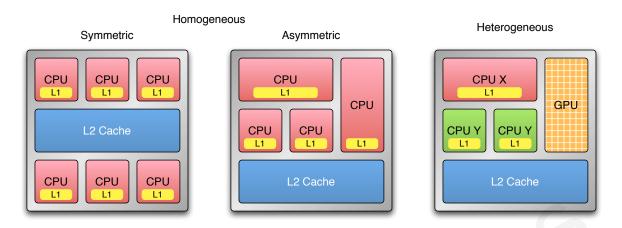

#### 1.2.3 Clustered Many-Core Architectures

The increasing number of processing units per chip results in a higher demand for "feeding" those units with both instructions and data. At the same time, neither the number of pins on the chip, nor the links to memory improve at the same rate as the number of cores. Moreover, the complexity of the interconnection network of large-scale multi-core architectures increases with the number of cores. The above mentioned multi-core issues result in limiting the scalability in terms of number of cores of these architectures. The proposed large scale clustered many-core architecture by Intel, also known as the Intel SCC [1] addresses the above limitations. Clustered many-core architectures consist of tiles of cores with private L1 and L2 cache, interconnected by a 2D-grid network. Off-chip memory requests are served by a number of memory controllers which are dedicated to a cluster of cores. In such architectures specific factors should be studied to define their impact to applications performance and consequently system throughput. More specifically, as the number of cores per cluster increases, so does their distance to the memory controller. This factor leads to non-uniform memory accesses (NUMA) and consequently influences the application execution time. Future clustered many-core architectures may consist of resources of different computational capabilities. This configuration can result on different performance and power efficient domains, which can satisfy different application requirements and therefore increasing system throughput and power efficiency. Given the application, determining appropriate resources for power-performance efficiency is not a trivial task. In addition, given the architecture characteristics of a clustered heterogeneous many-core architecture it is very difficult in practice to coordinate the scheduling operations during runtime. The key for determining the best matching core for a certain application is to find out the application's memory and computational requirements.

**Research Question 3:** How can a runtime system dynamically chracterize and assign the best matching resources for multiple high-performance applications on a heterogeneous clustered many-core system?

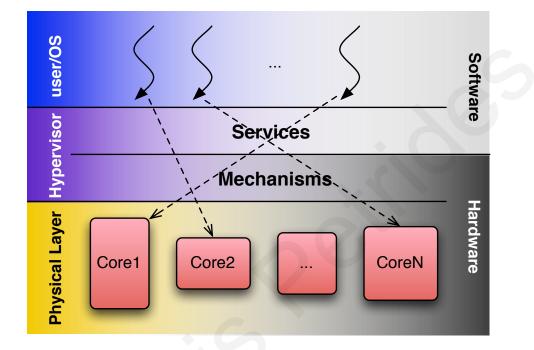

#### 1.2.4 Modular Virtualization Layer

As technology advances and architectures change, tuning the same applications over and over for the new architectures becomes an overwhelming task. Also, by using the same core designs, manufacturers are able to produce many different processors, depending on the number of available cores and their configuration. A virtualization layer or hypervisor can hide the complexity and diversity of the hardware. This virtualization layer can operate as the manager of the underlying hardware hiding some complexity of the system from the Operating System. In other words, by offering this virtualization layer along with the hardware it is possible to offer a standard set of core services to the upper layers, such as thread scheduling, memory prefetching, and hardware reconfiguration. For example a regular Operating System could use the scheduling services provided by the virtualization layer to do the mapping of the tasks among the available cores. This mapping could be as simple as just randomly distributing the threads among the different cores or as complex as making architecture-aware decisions that, based on online monitoring information of the application behavior, are able to select the best matching cores available. The mentioned services are supported by a group of mechanisms transparent to the user and/or the Operating System.

#### 1.3 Thesis Statement

In order for applications to exploit the performance benefits of multiple heterogeneous cores in a system you need a runtime environment that can help with different tasks such as data prefetching, performance isolation between co-execution, and best matching of resources determined dynamically. The vision is that future many-core chips will have a virtuallization layer that will support these and many more services transparently to the user.

#### 1.4 Objectives and Contributions

#### 1.4.1 Goal

The main goal of this thesis is to address the challenges raised for future many-core architectures. *First*, the architectural characteristics of clustered many-core architectures are exploited as to achieve high performance efficiency. *Secondly*, virtualization technique are explored as a way to achieve isolation and minimize the impact of interference on shared resources for co-executing applications. *Finally*, a scheduling policy is proposed for clustered many-core architectures having as an objective to satisfy the requirements of the applications in terms of available resources during runtime. To present the findings the proposed implementations are evaluated using applications from different domains. The objectives and contributions of this thesis are stated below.

## 1.4.2 Objective 1: Parallelism on a Clustered Many-Core Architecture

To answer *Research Question 1* (Section 1.2.1), the benefits of using future many-core architectures are exploited, more specifically on-chip clustered many-core architectures, on memory demanding applications. To achieve this goal the performance of the basic database algorithms parallelized are analyzed using the RCCE programming API [2] provided for the Intel SCC. Different implementations for the data parallel sequential scan, nested-loop and hash join query algorithms were implemented. Additionally, the impact on performance using a shared on-chip memory message passing buffer (MPB) as a prefetching buffer is also studied. The algorithms

are the basis for the execution of standard representatives DSS queries taken from the TPC-H benchmark suite [3]. Real database workloads were selected, which represent different database algorithms, and their performance is evaluated on a real system, the Intel SCC experimental processor [4], using the proposed method of data prefetching.

<u>Contribution</u>: This work exploits the characteristics of clustered many-core architectures for the benefit of memory demanding applications. More specifically, the on-chip message passing buffer is used as a prefetching mechanism which stores data for all cores to be used when needed. Therefore, the off-chip memory accesses are minimized and eviction of useful data from L2 caches. The MPB is used in two ways: (*i*) as a whole, where each core writes only to its own MPB and reads from all and (*ii*) as 48 different buffers, where each core writes and reads only to and from its own MPB [5,6]. More details on the implementation and results of this work are presented in Chapter 2.

#### **1.4.3 Objective 2: Guarantee Performance**

To address *Research Question 2* (Section 1.2.2), virtualization is used as a way to split the multi-core processor into different *Performance Domains*. The objective is to provide a way for several applications to execute on the multi-core processor but at the same time to guarantee performance isolation. Therefore, an application executing on a certain performance domain will maintain its performance independently of the load in the rest of the multi-core processor. In addition, this solution is non-intrusive, *i.e.* it does not require any changes to the application and can thus be applied to any existing executable.

*Contribution:* The contribution of this work is firstly the analysis of the feasibility of such a solution and secondly to study the different virtualization methods, *i.e.* hosted and bare-metal virtualization. Performance penalty suffered by HPC applications when co-executing on top of different VMs is also studied [7]. More details on the implementation and results of this work are presented in Chapter 3.

#### 1.4.4 Objective 3: Heterogeneous and NUMA-aware Scheduling

To address *Research Question 3* (Section 1.2.3), a runtime system is proposed for clustered many-core architectures which should determine the best matching core for a certain application by identifying the application's memory and computational requirements. It is important to acquire enough data to perform application classification and to classify the application as memory- or compute-bound so it is given the best matching core. In addition to the placement, the runtime should constantly monitor the behaviour of the applications. If changes are observed, for example resulting from an application entering a new phase, a classification phase is triggered in order to determine a new better placement. Since classification of applications is applied on a system with applications co-executing, this is achieved by indirectly observing how the performance is affected from the interference on shared resources.

<u>Contribution</u>: The main contributions of this work is: (*i*) propose a dynamic online classification methodology by determining the degree of memory- and computebound for each application, (*ii*) propose and implement a scalable dynamic scheduling policy for future heterogeneous many-core architectures, (*iii*) evaluate the scheduler using real applications applications (from SPEC benchmark suite) on a real many-core architecture (the 48-core Intel SCC processor) and (*iv*) study its scalability and extension over a simulated many-core architecture [8,9]. More details on the implementation and results of this work are presented in Chapter 4.

#### **1.4.5** Thesis Vision for the Future

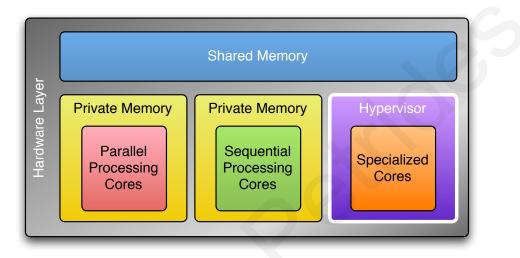

Future multi-core processors will be composed of cores with different computational and memory capabilities, which are also able to change their configuration at runtime resulting in Morphable architectures. Morphable multi-core architectures are composed of several asymmetric cores which have the capability of changing their configuration at different levels for both their logic and memory elements. This results in a more efficient hardware platform that besides being able to adapt the application execution to the hardware underneath, is also able to adapt the hardware to the demands of the different applications and/or phases. Managing and exploiting such future large-scale systems, not only in terms of software but also the hardware architecture and design, is not a trivial task. The vision of this thesis for future manycore processors is that they will be coupled with a Virtualization Platform, which will be able to wrap the complexity of the underlying hardware and manage its resources transparently to achieve an improvement of the overall system efficiency [10].

# Chapter 2

# DSS Workload Parallelism on a Clustered Many-Core Architecture

The increasing number of cores on a clustered many-core architecture can be exploited by applications with high degree of parallelism resulting in performance improvements. Porting an application for such architectures is not a trivial task but a joint task of considering both underlying architecture and applications behavior. Memory-bound applications with high degree of parallelism can create an increasing number of memory requests, which must be satisfied without becoming a performance bottleneck. Decision Support System (DSS) workloads are known to be one of the most time-consuming database workloads that process large data sets [11]. Traditionally, DSS queries have been accelerated using large-scale multiprocessors. In this work the benefits of using future many-core architectures are exploited, more specifically on-chip clustered many-core architectures. To achieve this goal different representative data parallel versions of the original database scan and join algorithms are proposed. Additionally, the impact on the performance when on-chip memory, shared among all cores, is used as a prefetching buffer is also studied. For the experiments of this work the behaviour of three queries from the standard DSS benchmark TPC-H executing on the Intel Single chip Cloud Computer experimental processor (Intel SCC) is studied. Results show that parallelism can be well exploited by such architectures and how important it is to have a balance between computation and data intensity. Moreover, the experimental results show that performance improvement of 5x and 10x for the corresponding query implementation without data prefetching. Finally this work shows how the system could be used efficiently to achieve high power-performance efficiency when using the proposed prefetching buffer.

#### 2.1 Motivation

The multi-core architecture is the *de-facto* standard in processor design. This architecture offers the benefit of an increased degree of parallelism to provide better performance, without the drawbacks of previous monolithic designs, such as high power consumption and complex design. As technology improves, the integration level increases leading to an increase in the number of cores per chip. While this results in a further increase of the degree of parallelism, it may not necessarily lead to improved performance, even when considering highly parallel applications. The increasing number of processing units per chip results in a higher demand for "feeding" those units with both instructions and data. At the same time, neither the number of pins on the chip, nor the links to memory improve at the same rate as the number of cores. Moreover, the complexity of the interconnection network of large-scale multi-core architectures increases with the number of cores. The above mentioned multi-core issues result in limiting the scalability in terms of number of cores of these architectures. The proposed large scale many-core architecture by Intel, also known as the Intel SCC [1] addresses the above limitations.

Database applications are of the most demanding workloads. More specifically, Decision Support Systems (DSS) database applications combine the processing of large data sets along with the computation of statistical information extracted from data. The goal is first to show the advantages that a future clustered many-core architecture, like the Intel SCC experimental processor [1], could have in a large scale data center that handles DSS applications. Secondly, the benefits of prefetching are presented for the studied workloads when a shared on-chip memory is used as a prefetching buffer. Finally the power-performance efficiency analysis of the system for the different query implementations is shown.

This work analyzes the performance of the basic database algorithms parallelized using the RCCE programming API [2] provided for the Intel SCC. Different implementations for the data parallel sequential scan, nested-loop and hash join query algorithms were selected. For the proposed implementations the impact on performance when a shared on-chip memory is used as a prefetching buffer is also studied. The algorithms are the basis for the execution of standard representatives DSS queries taken from the TPC-H benchmark suite [3]. Real database workloads, which represent different database algorithms, were selected and their performance is evaluated on a real system, the Intel SCC experimental processor, using the proposed method of data prefetching. Results show performance improvement by factors of 5x to 10x when data prefetching is used. Moreover, with a small performance loss high benefits in power consumption are gained resulting to high power-performance efficiency.

#### 2.2 Related Work

Different works study the performance evaluation and optimization of database workloads. Porting and evaluating the performance of such workloads in different systems is being of a large interest due to the fact that large data centers are executing such workloads and performance and power efficiency is of their most interest. Data prefetching is a technique widely used for reducing the memory latencies by fetching data to the processors cache before it is requested in order to avoid misses that would otherwise occur. Data prefetching can be done automatically in hardware [12], where the prefetcher predicts the next data to be requested, or in software where data requests are explicitly placed by the programmer of the compiler in the code [13]. An example of data prefetching for accelerating the execution of database workloads is in [14]. Pre-execution [15] is an alternative prefetching mechanism using an extra thread called helper thread that executes portions of the code ahead of the execution threads. Trancoso et al. [11] investigated the acceleration of decision support queries when executed on Cell/Be [16] and GPUs using Rapidmind [17] as a common platform. For their evaluation they used different workloads from the TPC-H benchmark suite. They implemented a nested loop join and a hash join algorithm exploiting the streaming processing model in order to optimize the performance of the queries. Their experimental results show speedups up to 21x. In [18] the authors presented an efficient way of memory copy operations on the Intel SCC experimental processor where they manage to use the LUT entries of each core in order to direct forward the necessary data to the corresponding core. In [19] the authors investigate the performance behaviour of a pipelined parallel sorting ported for the Intel SCC experimental processor showing that a combination of pipelined mergesort and sample sort best fits in such architectures.

Different works have focused on dynamic voltage and frequency scaling [20]. Isci *et al.* in [21] show multiple power domains offer power savings in CMP systems over a single power domain. Ioannou *et al.* in [22], propose a hierarchical power management scheme applicable to reduce the energy consumption on many-core architectures by reducing the running frequency/voltage of the cores. The experiments conducted by the authors on an Intel SCC machine show that their power management scheme is capable of an average reduction of energy consumption by 11.4% while the execution time is increased on average by 7.7% compared to the baseline execution without the use of the power management scheme. In [23] the authors presented an analysis of power and energy consumption of Intel SCC research processor. The authors used time and power profiling of a very simple parallel application. They also study the effects of power and energy consumption of the system by varying the number of cores, clock frequency and voltage level.

This work studies the performance and parallelism scalability of database queries algorithms using different techniques in order to optimize their performance like data prefetching. Moreover, power-performance efficiency analysis of database algorithms using different implementations is presented. Finally, experiments were executed on a representative many-core architecture platform, the Intel SCC, and they show how the selected workloads can be benefit in such architectures.

## 2.3 Intel SCC Clustered Many-Core Architecture

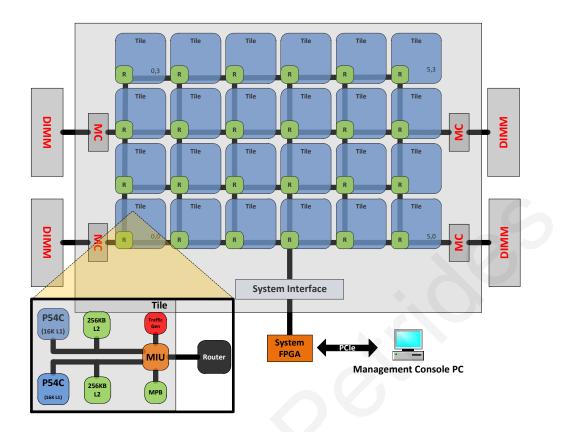

The Intel SCC experimental processor is a 48-core 'concept vehicle' created by Intel Labs as a platform for many-core software research [1]. This processor consists of 24 dual-core tiles interconnected by a 2D-grid network. The tiles are organized in a 6x4 mesh with each tile containing:

- Two P54C cores with 16KB L1 and 256KB L2 cache dedicated to each core;

- A 16KB Message Passing Buffer (MPB) for storing messages to be sent to other cores (8KB per core);

- A Traffic Generator for testing the performance capabilities of the mesh network;

- A Mesh Interface Unit (MIU) to connect to the network;

Figure 2.1: Intel SCC Architecture

The MIU connects each tile to a router, to finally create a mesh interconnection network. The MIU is responsible for packetizing data that will go onto the network and de-packetizing data that come from the network. This unit is shared by the two cores in a round-robin scheme [24].

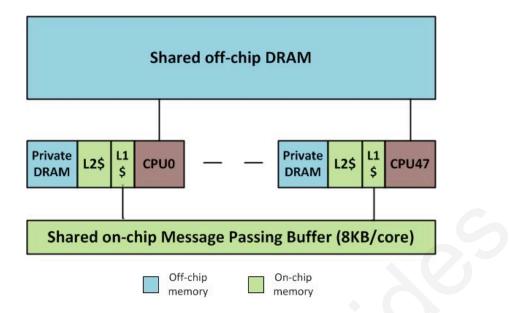

The maximum main memory the system can support is 64GB. The 32-bit memory addresses of the core are translated into system addresses by the MIU through a lookup table (LUT) [24]. The systems' main memory is located outside the chip and four DDR3 Memory Controllers (MC) are used to move data on and off chip. Figure 2.2 presents an overview of the SCC Memory Architecture and how the programmer can view the system and the core's memory through the RCCE message passing API [24]. The SCC supports both distributed and shared memory programming models and the systems' memory is configured and separated in four regions:

• Private off-chip memory: Each core's LUT is configured such that a specific region of the off-chip DRAM (equally divided to all) is only accessible by that core.

*Figure 2.2: Intel SCC Memory Architecture as used by the programmer through the RCCE message passing API*

- Shared off-chip memory: This region of the off-chip DRAM is mapped by all LUTs and all cores have direct access to it through any MC. These data are not cached as the system does not provide cache-coherence;

- Shared on-chip memory: Also called Message Passing Buffer (MPB), this onchip SRAM is cached in the L1 caches of the cores;

- L2 cache: used only by the private off-chip memory

#### 2.3.1 On-Chip Shared Memory

As described above the shared on-chip memory (MPB) is used for messages exchanged between cores where each core has a chunk of 8KB adding in a total 384KB of shared on-chip memory. Data from MPB are cached in cores' L1 cache. Except from a small amount of the MPB that is used by the system, it is possible to use the rest of it to move data closer to the cores and therefore minimize the delays of accessing data previously located to the off-chip memory.

In this work is studied how this shared on-chip memory can be used as a prefetching buffer. More specifically, it studies how data for all cores can be stored in this buffer in order to be used when needed. Therefore minimizing the off-chip memory accesses and eviction of useful data from L2 caches. MPB size is limited to 384KB and each core writes to its own chunk of 8KB. Therefore the MPB is used in two ways: (i) as a whole, where each core writes only to its' own MPB and reads from all and (ii) as 48 different buffers, where each core writes and reads only to and from its' own MPB. Section 2.5 describes in detail how the MPB is used as a prefetching buffer for the different query algorithms.

#### 2.4 Database Workloads

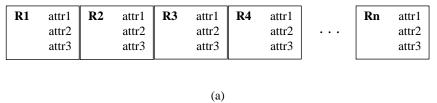

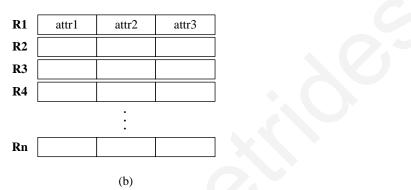

This work is focused on the execution of the basic database algorithms and their parallel implementation. As such, the queries analyzed in this work were implemented as programs that execute the operations determined by the queries and their results were validated. Three different queries from TPC-H benchmark suite [3] of different complexity and demands have been ported. More specifically Queries 3, 6 and 12, which from now on are referenced as Q3, Q6 and Q12. Figures 2.3, 2.4 and 2.5 describe the three queries in the original SQL code. The selected queries are of different complexity both in terms of the amount of data uses and in terms of the operations performed on the data [25]. More specifically, the selected queries include representative operations performed in DSS workloads. In particular, simple table scan performing an aggregate sum on specific field is included in Q6, whereas Q12 joins two tables and performs a count on the items satisfying the query condition. Finally, Q3 joins three tables and selects a specific field when the query conditions are satisfied. Therefore, the selected query algorithms that encapsulate the representative operations of DSS workloads both in terms of operations and in terms of combining different data sets for obtaining the desired results. The processing data is formatted in two ways in order to evaluate different implementations of the query algorithms.

In the first format data are stored row-wise, *i.e.* all attributes of a particular record are stored in the same *row* of a two-dimensional array. Let's consider a table (Table A) which is composed of records containing three attributes: attr1, attr2, and attr3. For each record a new row is created that stores all its attributes.

Another format of data is hashing the data according to the key, primary or foreign, on which tables can be joined. More specifically, discrete linked lists of records are created based on the tables' key on which the join operation is performed.

For example, consider Figure 2.6 (c) and (d), Tables' A records are hashed according to their primary key whereas Tables' B records are hashed according to

```

select

sum(l_extendedprice*l_discount)

as revenue

from

lineitem

where

l_shipdate >= date '[DATE]'

and l_shipdate < date '[DATE]'

+ interval '1' year

and l_orderkey = o_rderkey

and l_discount between

[DISCOUNT] - 0.01 and + 0.01

and l_quantity < [QUANITIY];</pre>

```

*Figure 2.3:* TPC-H Q6. *The parameters used were:* DATE=2005, DISCOUNT=10, and QUAN-TITY=1000000.

```

select

sum(case when

o_orderpriority = '1-URGENT' or

o_orderpriority = '2 - HIGH'

then 1 else 0 end)

as high_line_count

from

orders, lineitem

where

o_rderkey = l_orderkey

and l_shipmode in

('[SHIPMODE1]', '[SHIPMODE1]')

and l_commitdate < l_receiptdate

and l_shipdate < l_commitdate

and l_receiptdate > date '[DATE]'

and l_receiptdate > date '[DATE]'

+ interval '1' year;

```

*Figure 2.4: Simplified version of TPC-H Q12. The parameters used were: SHIPMODE1=1, SHIP-MODE2=2 and DATE=2009.*

their foreign key. The join operation between Table A and B can then be performed directly.

*Figure 2.5: Simplified version of TPC-H Q3. The parameters used were: DATE=2007 and SEG-MENT=3.*

### 2.5 Algorithms Implementations

The query algorithms implemented for the purpose of this work are: (*i*) data-parallel sequential scan, (*ii*) nested-loop join and (*iii*) hash join. More details on their implementation follows.

#### 2.5.1 Data-Parallel Sequential Scan (DPSS)

Given the data layout as presented above, for this work, the simple sequential scan algorithm is used as to exploit both load balancing and locality while traversing the data. For the purpose of this work, all records are traversed and the records' attributes are checked against a certain condition. The condition may be a simple attribute comparison or a complex boolean function. This operation is mapped to the Intel SCC by implementing the condition to be tested and by sending to each core the input parameters which are the data streams that are used to evaluate the scan condition.

#### 2.5.2 Parallel Nested-Loop Join

For the join operation the nested-loop join algorithm is used. Each table has a number of rows equal to the number of records and the data of each record are organized in columns. To perform this operation each record of the outer loop is compared with all the records of the inner loop in an iterative way. Parallelization is achieved by splitting the data of the outer loop to all cores.

Figure 2.6: Table A: (a) logical and (b) physical data organization for parallel nested-loop join operation.

*Figure 2.7: Table A: (a) logical and (b) physical data organization for hash join operation.*

Figure 2.8: Description of data prefetching using the MPB.

### 2.5.3 Hash Join

Another implementation of the join operation that is evaluated for the selected queries algorithms is the hash-join algorithm. In this case all records of each table are organized according to the key that the join operation is performed on as described in Section 2.4. Therefore the join operation is performed on each lists' key and if the condition is satisfied then all its records are examined. In the case of Q12 where only two tables are joined this operation is performed only once and if the condition is satisfied then it proceeds with the operations defined in the where clause of the query. In the case of Q3 although there are three joined tables. First Tables A and B are joined, as in Q12, and the results produced from this operation are forwarded to the second step where these results are joined with Table C using the same method of hashed data. Parallelization of the hash join implementation of the queries algorithms is achieved by splitting the data in the first level of join. Meaning each core takes a chunk of data of the first table that is joined in the algorithm. For example in Q12 where Tables A and B are joined, A and B are joined and B are joined for the first table that is point in the algorithm.

the case of Q3 where Tables A, B and C are joined Table A is split among cores.

## 2.5.4 Data Prefetching

In order to use data prefetching and minimize the number of off-chip memory accesses the MPB of the system is used. To achieve this the previously mentioned algorithms in Sections 2.5.1, 2.5.2 and 2.5.3 are implemented using the MPB as a prefetching and storing buffer for most commonly used data, in an effort to optimize the performance. Data fetched or read from the MPB are controlled at user level by specifying which data and when are to be used.

For the Q6 query which is a simple scan operation, the MPB of each core is used to fetch and store portions of data, 8KB long, from main memory. From there on these data are copied directly to L1 cache and the necessary operations are performed. In this case each core writes and reads data only to and from it's own MPB. In Figure 2.8 the representation of this algorithm is depicted. In Step 1 each core copies data from the off-chip main memory to its' local MPB and in Step 2A it copies those data to its' L1 cache for calculation. These two steps are iterative steps until all data are processed.

For the Q12 query the data prefetching scheme is used only for the nested-loop join implementation. The reason that the prefetching could not be used on the hashjoin implementation is related to the organization of the data and that moved data are moved from one table to the MPB then the hashing implementation would no longer exist. On the other hand if the hash table is moved into the MPB there would still be a need to go off-chip in order to access the data directed by the hash table (currently located in the main memory). This would result in a larger overhead, minimal cache misses reduction and eviction of necessary data from L2 cache, since main memory is cached in L2. For the nested-loop join algorithm of Q12 the MPB is used to store data from the inner-most table (Table B) and let the outer-most table (Table A) to be cached in L2. In Figure 2.8, Q12 algorithm for data prefetching uses Steps 1 and 2B. Each core will copy data from Table B to its' local MPB (Step 1) and then each core will read and perform calculations on data from all the MPB chunks (Step 2B). Step 1 and 2B are iterative because Table B cannot fit in the total of 384KB of the systems' MPB, so as soon as all cores finish Step 2B they will repeat this process again until all data are processed.

For the Q3 query the data prefetching is used on both nested-loop join and a hybrid implementation of hash-join and nested-loop join. For the nested-loop algorithm the inner-most table (Table C) is stored in the MPB. Table C is chosen to be prefetched and stored in the MPB since it is the table that is most frequently used and thus resulting in a significant reduction of the last level cache misses. Also, it has the smallest size and in this case it could fit for both input sizes in the MPB of the system. For the hybrid implementation, where both hash-join and nested-loop join are used, the hash-join operation is performed for the first join operation (Tables A and B) and for the records satisfying the query condition a nested-loop join with Table C is performed. In Figure 2.8 Steps 1 and 2B depict this implementation showing that Step 1 in Q3 will only be executed once and each core will copy a portion of Table C to its' local MPB. In the case that Table C does not fit in the MPB the algorithm will become iterative and continue fetching data from main memory just as it happens with Q12. Finally in Step 2B each core will read and perform calculations on data from all the MPBs of the system.

## 2.6 Experimental Setup

For the evaluation of this work the Intel SCC experimental processor is used, RockyLake version [1]. The operating system used for the Intel SCC cores is the default Linux kernel provided by the RCCE SCC Kit 1.4.0 [2]. The host PC, responsible for controlling the applications execution on the Intel SCC processor, is configured with Intel Core i7 processor 3.7GHz and 4GB of main memory. For porting and executing the applications on the SCC the RCCE 1.4.0 toolchain was used.

The workloads used for this work were selected from the TPC-H queries as described in Section 2.5. Different input sizes were used for evaluation in order to study their performance scalability. The input data sets were generated using the *dbgen* tool. The input sizes 0.01 and 01 as well as the number of tables used for each query execution are: (*i*) Q3 use of 3 Tables of total size of 4.24MB and 93.56MB, (*ii*) Q6 use 1 Table of size 4.24MB and 93.56MB and (*iii*) Q12 use of 2 Tables of total size 3.74MB and 91.14MB.

For the purpose of this work the power consumption is also measured of the system in order to calculate the power-performance efficiency of the system. In terms of calculating the power consumption of the chip an application is developed

| Query | Tables | Input Size 0.01 | Input Size 0.1 |

|-------|--------|-----------------|----------------|

| Q3    | 3      | 4.24MB          | 93.56MB        |

| Q6    | 1      | 3.71MB          | 74.24MB        |

| Q12   | 2      | 3.74MB          | 91.14MB        |

Table 2.1: TPC-H Queries input sizes.

that measures the power consumption using the same technique used by the SCC GUI performance meter and involves reading the FPGA emulated registers that hold the appropriate values. The measurement is calculated using the product of the total SCC chip voltage and the total current flowing through the chip. To enhance the precision of the used meter the power measurement is being collected several times every second during the whole execution time of each scenario. At the end of the scenario execution the average power consumption was calculated from the measurements done during the execution. For the experiments of this work the frequency of the cores is scaled to three different frequencies: (i) 100MHz, (ii) 266MHz and (iii) 533MHz. The frequency scaling is performed before the execution of each scenario using the library provided by the RCCE toolchain. In order to calculate the power-performance efficiency of the system the following metric is used:

$$NormalizedEfficiency = \frac{ExecutionTime*Power_{baseline}}{ExecutionTime_i*Power_i}$$

(2.1)

The experimental results were normalized using the formula in 2.1 for the different implementations to the single core execution of the base line scenario of each query executing at 533MHz (where *i* are the different implementations of the query algorithms, *i.e.* Nested-Loop Join, Hash Join etc). Higher the results the better.

## 2.7 Experimental Results

#### 2.7.1 Performance Evaluation

For the first analysis the performance behaviour is compared of the different queries algorithms executed on the Intel SCC experimental processor as described in Section 2.5 and their scalability is studied for the target architecture. Moreover, it is

*Figure 2.9: Normalized scalability of Q12 query.*

studied how the data prefetching scheme proposed can improve their performance. The results presented herein are for 533MHz cores' frequency due to the limited space available, even though 266MHz and 100MHz show the same behavior.

In Figure 2.9 the performance behavior and scalability of the different implementations of Q12 query is presented. In Figure 2.9 execution times are normalized to the corresponding execution of the nested-loop join implementation for a single core. Results show first of all the hash join algorithm outperforms the nested-loop join implementation by a factor more than 10x. This performance difference can be explained from the way data are mapped and the efficiency of the hash join implementation. In the case of the loop-join implementation each record of the outer table must be compared with all the records of the inner table, therefore resulting to more comparisons in contrast to the hash join implementation. The second important observation is when the prefetching scheme is used for the nested-loop join algorithm. It can be observed that up to 5x performance improvement can be gained compared to the nested-loop implementation as a result of devoting MPB for data that are mostly used. In particular data are prefetched to MPB and these data are stored without being influenced from evictions of L2 cache, therefore data reuse can be achieved without any additional main memory accesses. Using performance counters and monitoring the L2 cache of the core it was observed that the data prefetching implementation reduces the L2 cache misses by a factor of 700. Even though using data prefetching, the performance of the hash join implementation could not be outperformed as a result of their significant difference to their data organization and algorithm implementation. As for the scalability of the different implementations,

*Figure 2.10: Normalized scalability of Q3 query.*

it is possible to see that nested-loop join (with or without data prefetching) scales well whereas hash join implementation is stable to the number of cores. This can be explained from the fact that the hash join implementation algorithm complexity is limited and data transfers dominate the computation time, in a ratio of 1:20 computations over data transfers, resulting in no performance improvement as the number of cores increases.

In Figure 2.10 the performance behaviour and scalability of the different implementations of Q3 query is presented. In Figure 2.10 execution times are normalized to the corresponding nested-loop join implementation on a single core. The first observation is that the nested-loop join implementation using data prefetching does not improve the performance compared to the implementation without data prefetching. This is explained from the fact that the table stored in the MPB can fit in the L2 cache of the core compared to the limited size of the MPB. This results in higher overheads on fetching data from the main memory to the MPB until all data are processed. The difference to the execution times when using data prefetching is due to two main factors. First in the case of scenarios with 4,8 and 48 cores, records are equally divided among cores, as explained previously, but the number of each cores records that satisfy the condition varies among cores in an average of 20%. In addition, there is the overhead of the prefetching scheme. More specifically, data chunks of 8KB are always read from MPB regardless if they satisfy or not the where clause condition. Instead in the nested loop-join implementation data from main memory will only be read until the where condition is satisfied. In the case where the condition is not satisfied or all data must be read the two implementations converge.

*Figure 2.11: Data-parallel sequential scan (Q6) normalized execution time and breakdown.*

Another important observation is the fact that the hash join implementation outperforms the nested-loop implementation having the behaviour of Q12. The most important observation is the fact that the hybrid implementation of Q3 using first hash join and the data that satisfy the condition are then passed to a nested-loop join where the table on which they are compared are already stored in the MPB. This implementation shows important performance improvement over the other implementations as a result of gaining the most from both the hash join implementation but also from the prefetching scheme.

It is also important to observe the scalability of the different implementations of the Q3 query. A good scalability can be observed, but not at the same level as the scalability of Q12 query. This could be explained by comparing the two queries algorithm complexity over the data sizes processed. More specifically Q12 is a well balanced query between computation and data size and therefore shows a better scalability compared to Q3 which has near the same data size but higher complexity than Q12. More specifically the ratio of computation over data transfers of Q12 is 5x larger than the one of Q3.

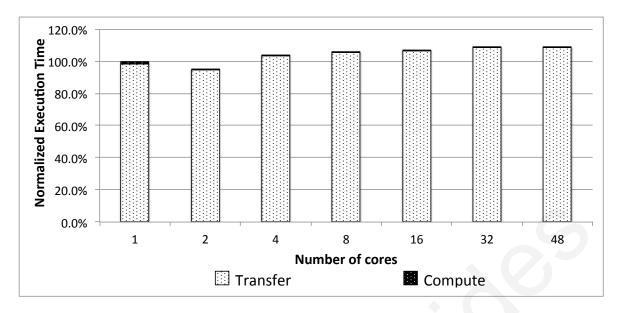

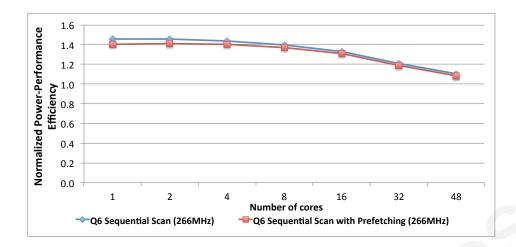

In Figure 2.11 the normalized execution time of the data-parallel sequential scan implementation for Q6 is presented. The execution time is normalized to the execution time of the corresponding sequential scan on a single core. It can be observed that no significant performance improvement can be achieved with the use of data prefetching. This is a result of the simplicity of the query algorithm where data accesses dominate the computation time with a ratio of 1:30 of computations over data

Figure 2.12: Normalized power-performance efficiency of Q3 query.

transfers. Also the fact that no data reuse is made in this algorithm does not allow the prefetching scheme to improve its performance opposed to the data prefetching implementations of Q3 and Q12 queries.

#### 2.7.2 Power and Performance Efficiency

Another aspect of this work is to study the power-performance efficiency of the executed query implementations on the Intel SCC research processor. For this set of experiments the frequency of cores is scaled to 266MHz and 100MHz. As defined in equation 2.1 the higher the results the better for the different scenarios investigated. The most relevant results are depicted.

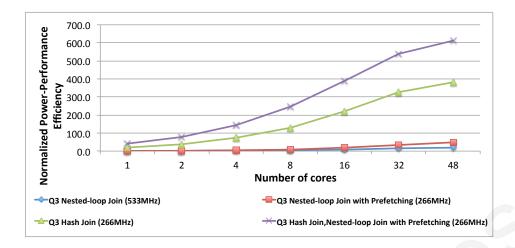

In Figure 2.12 the power-performance efficiency results of Q3 implementations is presented using as a baseline the nested-loop join implementation without data prefetching. Results show that high power-performance efficiency can be achieved if the proposed hybrid implementation is used, which is consist of the hash join and nested-loop join using prefetching. The results of the proposed hybrid implementation of Q3 query show that even if the frequency of cores is scaled to 266MHz high power-performance efficiency can be achieved compared to the other implementations of the same query. More specifically it can be observed that 600 more power-performance efficiency improvement can be achieved with the hybdrid implementation using data prefetching, where even though there is a small loss in performance high benefits in power consumption are gained.

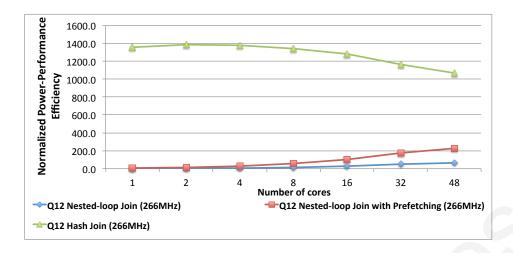

In Figure 2.13 the power-performance efficiency results of Q12 implementations is presented using as a baseline the nested-loop join implementation without data

Figure 2.13: Normalized power-performance efficiency of Q12 query.