## DEPARTMENT OF COMPUTER SCIENCE

# Harnessing CPU Electromagnetic Emanations for Power-Delivery Network Characterization

Zacharias Hadjilambrou

A dissertation submitted to the University of Cyprus in partial fulfillment of the requirements for the degree of Doctor of Philosophy

November, 2019

©Zacharias Hadjilambrou, 2019

# **VALIDATION PAGE**

Doctoral Candidate: Zacharias Hadjilambrou

**Doctoral Dissertation Title: Harnessing CPU Electromagnetic Emanations for Power-Delivery Network Characterization**

The present Doctoral Dissertation was submitted in partial fulfillment of the requirements for the Degree of Doctor of Philosophy at the **Department of** Computer Science and was approved on the 8/11/2019 by the members of the **Examination Committee**.

#### **Examination Committee:**

| Research Supervisor: | man                                               |

|----------------------|---------------------------------------------------|

| Research Supervisor: | Yiannakis Sazeides                                |

| Committee Member:    | Shidhartha Das                                    |

| Committee Member:    | Constantinos S. Pattichis<br>Elias Athanasopoulos |

| Committee Member:    | Maria Michael                                     |

| Committee Member:    | Ranar and                                         |

Ramon Canal

# **DECLARATION OF DOCTORAL CANDIDATE**

The present doctoral dissertation was submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy of the University of Cyprus. It is a product of original work of my own, unless otherwise mentioned through references, notes, or any other statements.

Zacharias Hadjilambrou

## Περίληψη

Ο επαγωγικός θόρυβος τάσης είναι μια από τις σημαντικές αυξανόμενες ανησυχίες στους σύγχρονους επεξεργαστές. Η υπερβολική πτώση της τάσης μπορεί να προκαλέσει μη ορθή λειτουργία. Ενώ η υπερβολική αύξηση της τάσης αυξάνει την κατανάλωση ενέργειας, τη διάχυση της θερμότητας και μπορεί να επιταχύνει τη γήρανση του υλικού. Ο θόρυβος τάσης προκαλείται από ξαφνικές μεταβολές στην κατανάλωση ρεύματος. Σύγχρονες τάσεις σχεδίασης όπως οι τεχνικές μεταβολές στην κατανάλωση ρεύματος. Σύγχρονες τάσεις σχεδίασης όπως οι τεχνικές χαμηλής κατανάλωσης ενέργειας (π.χ. power-gating, clockgating), οι γρήγορες συχνότητες και η υψηλή κατανάλωση ρεύματος, επιδεινώνουν τον θόρυβο τάσης. Για την αντιμετώπιση του προβλήματος είναι υψίστης σημασίας να αναπτυχθούν εργαλεία που επιτρέπουν τον χαρακτηρισμό των δικτύων παροχής ισχύος (ΔΠΙ) και την παρακολούθηση του επαγωγικού θορύβου τάσης. Τέτοια εργαλεία παρακολούθησης είναι χρήσιμα κατά τη διάρκεια των δοκιμών για να βοηθούν στον επαρκή καθορισμό των περιθωρίων τάσης που θα επιτρέπουν την ομαλή και ενεργειακά αποδοτική λειτουργία του επεξεργαστή. Επίσης, αυτά τα εργαλεία παρακολούθησης χρησιμοποιούνται στην κατασκευή κυκλωμάτων μετριασμού του θορύβου τάσης που προστατεύουν τον επεξεργαστή από χαμηλή τάση και εξασφαλίζουν αξιόπιστη λειτουργία.

Αυτή η διδακτορική θέση προτείνει μια νέα μεθοδολογία για τον χαρακτηρισμό ΔΠΙ. Η προτεινόμενη μεθοδολογία βασίζεται στην ασύρματη ανίχνευση της ηλεκτρομαγνητικής ακτινοβολίας (HA) που εκπέμπεται από το ΔΠΙ χρησιμοποιώντας μια κεραία και ένα όργανο για την ανάλυση των ληφθέντων σημάτων (όπως ένας αναλυτής φάσματος). Η προτεινόμενη προσέγγιση έχει τρία σημαντικά πλεονεκτήματα σε σύγκριση με κλασικές προσεγγίσεις χαρακτηρισμού ΔΠΙ: α) είναι μη παρεμβατική και βολική καθώς δεν φορτίζει, διακόπτει ή παρεμποδίζει το σύστημα με οποιονδήποτε τρόπο επιτρέποντας την παρακολούθηση του συστήματος ως έχει, β) θεωρητικά, είναι συμβατή με οποιαδήποτε πλατφόρμα καθώς οποιοδήποτε υλικό υπολογιστών εκπέμπει HA, γ) δεν επιβάλει επιπλέον

κόστος στον κατασκευαστή καθώς δεν απαιτεί υλικούς πόρους πάνω στον επεξεργαστή. Η προτεινόμενη μεθοδολογία βασίζεται στην παρατήρηση ότι η ΗΑ μεγάλης ισχύος κοντά στη συγνότητα συντονισμού του ΔΙΠ συσχετίζεται με υψηλό θόρυβο τάσης. Αυτή η δουλειά παρέχει τη θεωρητική βάση και την απόδειξη ότι αυτή η παρατήρηση ισχύει. Εκμεταλλευόμαστε αυτή την παρατήρηση με δύο τρόπους: α) για να μετρήσουμε τη συγνότητας συντονισμού του ΔΠΙ και β) για να θέσουμε αποδοτικά περιθώρια τάσης με τη βοήθεια ειδικών προγραμμάτων που μεγιστοποιούν το θόρυβο τάσης, αυτά τα προγράμματα παράγονται μέσω ενός γενετικού αλγόριθμου που μεγιστοποιεί την ΗΑ. Η προσέγγιση μας αξιολογείται σε διάφορους σύγγρονους επεξεργαστές. Σε όλους τους δοκιμασμένους επεξεργαστές με την προτεινόμενη μεθοδολογία μπορέσαμε να παρακολουθήσουμε με επιτυχία τον θόρυβο τάσης, να αναγνωρίσουμε τη συχνότητα συντονισμού, να δημιουργήσουμε προγράμματα που προκαλούν υψηλό θόρυβο τάσης και να θέσουμε αποδοτικά περιθώρια τάσης που μειώνουν την κατανάλωση ενέργειας. Επίσης, αυτή η διδακτορική θέση προσφέρει την πρώτη δημόσια διαθέσιμη εφαρμογή για αυτόματη δημιουργία στρες προγραμμάτων. Η εφαρμογή βασίζεται σε γενετικούς αλγόριθμους και έγει δοκιμαστεί με επιτυχία σε πολλούς διαφορετικούς επεξεργαστές.

## Abstract

Inductive dI/dt voltage-noise is a growing concern in modern processors. Voltage-noise is caused by sudden transitions in current consumption. Voltage-noise is manifested as large voltage droops and overshoots below and above the nominal supply-voltage. These events are a threat to reliability, robust execution and hardware longevity. Voltage droops may cause unreliable execution, whereas voltage overshoots increase power consumption, heat dissipation and may accelerate the hardware aging. Modern design trends such as: a) aggressive low-power techniques (e.g. power-gating, clock-gating), b) high dynamic-power range of multicore processors, and c) high current consumption, exacerbate voltage-noise rendering power-delivery a critical concern. Tools for characterizing Power Delivery Networks (PDN) and monitoring inductive dI/dt voltage-noise are required for: a) processor voltage and frequency margining at the post-silicon chip testing phase and b) for designing voltage-noise mitigation circuits that protect processor from voltage droops and ensure reliable operation.

This thesis proposes a novel methodology for PDN characterization. The proposed methodology is based on wirelessly sensing the PDN emanated electromagnetic (EM) radiation using an antenna and an instrument for analyzing the received signals such as a spectrum analyzer. The proposed approach has three major advantages compared to state-of-the art PDN characterization approaches: a) it is non-intrusive and convenient as it doesn't load, interrupt or physically interfere with the system in any way allowing monitoring the system as it is, b) it is cross-platform as all hardware emanates EM radiation, c) it adds zero-overhead as it does not require development effort nor on-chip/on-package resources. The proposed EM methodology is based on the observation that high amplitude EM emanations at the PDN resonance frequency are correlated with high voltage-noise. This thesis provides the theoretical basis and conclusive evidence that this correlation holds

true. We exploit this correlation for measuring the PDN resonance frequency and for voltage margining CPUs with the help of dI/dt stress-tests generated with a genetic algorithm (GA) that maximizes the amplitude of EM emanations. The EM approach is successfully evaluated on five different processors. On all tested processors we are able to successfully monitor PDN oscillations, identify the resonance-frequency and generate dI/dt stress-tests that cause higher voltage-noise and have higher minimum operational voltage (V<sub>MIN</sub>) than conventional workloads.

Additionally, this thesis delivers GeST (Generating Stress-Tests), a GA based framework for automatic stress-test generation that is developed for the needs of this thesis. To the best of our knowledge GeST is the first publicly available framework for stress-test generation. The key strengths of GeST are its flexibility and extensibility as it provides an easy interface for using and extending the framework.

#### Acknowledgements

This PhD thesis would have not been possible without the help of many great people that I had the fortune to meet and work with during the last 7 years. First and foremost, I would like to thank my advisor Yiannakis Sazeides with whom I had the pleasure to work since 2012. Yanos was my advisor during my BSc, MSc and PhD studies. In parallel with my studies, Yanos gave me the opportunity to work for large impact European research projects such as EuroCloud, Harpa and Uniserver. I cannot thank him enough for giving me these opportunities. All these years we had an excellent cooperation. Yanos is characterized by his strong work ethics and tremendous passion for science. These aspects compose the exceptional advisor, scientist and person he is.

I also consider myself extremely fortunate to have cooperated with another remarkable man; my other advisor Shidhartha Das. The first time I met Sid was during my first internship in Arm in 2013. Since then we had a continuous cooperation and the epitome of our efforts is this PhD thesis. Sid was my manager during my last internship in Arm (from Sep 2017 – Dec 2017). The work performed during that internship contributed significantly in delivering this thesis.

Next, a big thank you is devoted to Marco A Antoniades and Kyriakos Neophytou. With their expertise in antennas and electromagnetic waves, they provided invaluable help and support. They constructed all the antennas used in this thesis and assisted in gathering all the necessary equipment for setting up the EM experimental setup.

I would like to thank people who I cooperated with during my time in Xi Computer Architecture research group. I would like to thank Chrysostomos Nicopoulos with whom we have cooperated closely for the Eurocloud and Harpa projects. I would like to thank Pedro Trancoso; we cooperated for the Uniserver project and I was truly lucky to have him as my professor in various university courses as well. Of course, I would like to thank all the fellow students and researchers that passed from the group: Marios, Panagiota, Panayiotis, Lorena, Giorgos, Kypros, Georgia and many others. With these people I shared the same lab for many years and their presence made life at work easier and more enjoyable.

Also, I would like to thank my colleagues and friends at Arm Cambridge offices. I would like to thank Emre Özer who contributed in establishing close working relationship between Arm and University of Cyprus. I would like to thank Paul Whatmough, my line manager during my first and second Arm internships who has contributed to the development of the GeST framework. I would like to thank David Bull for being always willing to share his high technical expertise. A big thank you to the people I hanged together with; my fellow Arm internship students and friends Vaibhav, Rohan and Jeremy. Their presence made life and work in Cambridge much more amusing.

Many thanks to the members of the examination committee for their time and their comments that helped improving this thesis. Likewise, special thanks go to all conference and journal reviewers which contributed to polishing this thesis through their feedback.

Many thanks to the institutions that contributed to this thesis: University of Cyprus and Arm. I would like to thank University of Cyprus for providing me the appropriate environment to carry this thesis, and for being my second home for the last eleven years. Also, a big thanks to Arm for providing me the opportunity to work there during three different internships.

Finally, I genuinely express my thankfulness towards my family and Avraamia for encouraging me and standing by my side during this journey. I dedicate this PhD thesis to my grandfather, Zacharias Hadjilambrou, who although passing away he has always been a role model and an inspiration, guiding my way through science. I remember him from a very young age sitting with me and teaching me how to read and write. He was also a holder of a doctoral degree and I am very proud and grateful for achieving to follow his footsteps.

# **Thesis Contributions**

This thesis has contributed to the following achievements.

- <u>Hadjilambrou, Zacharias</u>, Shidhartha Das, Marco A. Antoniades, and Yiannakis Sazeides. "Leveraging CPU Electromagnetic Emanations for Voltage Noise Characterization." In 2018 51st Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), pp. 573-585. IEEE, 2018.

- <u>Hadjilambrou, Zacharias</u>, Shidhartha Das, Paul N. Whatmough, David Bull, and Yiannakis Sazeides. "GeST: An Automatic Framework For Generating CPU Stress-Tests." In 2019 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), pp. 1-10. IEEE, 2019. [Best Paper Nominee]

- <u>Hadjilambrou, Zacharias</u>, Shidhartha Das, Marco A. Antoniades, and Yiannakis Sazeides. "Sensing CPU voltage noise through Electromagnetic Emanations." *IEEE Computer Architecture Letters* 17, no. 1 (2018): 68-71. [Best paper award]

- 4. US patent application: Power Analysis, application ID 20190064896, http://appft.uspto.gov/netacgi/nph-Parser?Sect1=PTO2&Sect2=HITOFF&p=1&u=%2Fnetahtml%2FPTO%2Fsearchbool.html&r=1&f=G&l=50&co1=AND&d=PG01&s1=Sazeides.IN.&OS=IN/Sazeides&RS=I N/Sazeides

- 5. Software Framework: GeST https://github.com/toolsForUarch/GeST

- <u>Hadjilambrou, Zacharias</u>, Shidhartha Das, Marco A. Antoniades, and Yiannakis Sazeides, Harnessing CPU Electromagnetic Emanations for Resonance-Induced Voltage-Noise Characterization, IEEE Transactions on Computers (Under Submission)

- Whatmough, Paul N., Shidhartha Das, <u>Zacharias Hadjilambrou</u>, and David M. Bull.

"Power integrity analysis of a 28 nm dual-core ARM cortex-A57 cluster using an all-digital power delivery monitor." IEEE Journal of Solid-State Circuits 52, no. 6 (2017): 1643-1654.

- Whatmough, Paul N., Shidhartha Das, <u>Zacharias Hadjilambrou</u>, and David M. Bull. "14.6 an all-digital power-delivery monitor for analysis of a 28nm dual-core arm cortex-a57 cluster." In 2015 IEEE International Solid-State Circuits Conference-(ISSCC) Digest of Technical Papers, pp. 1-3. IEEE, 2015.

- Konstantinos Tovletoglou, Lev Mukhanov, Georgios Karakonstantis, Athanasios Chatzidimitriou, George Papadimitriou, Manolis Kaliorakis, Dimitris Gizopoulos, <u>Zacharias</u> <u>Hadjilambrou</u>, Yiannakis Sazeides, Alejandro Lampropulos, Shidhartha Das, Phong Vo: Measuring and Exploiting Guardbands of Server-Grade ARMv8 CPU Cores and DRAMs. DSN Workshops 2018: 6-9

- Georgios Karakonstantis, Konstantinos Tovletoglou, Lev Mukhanov, Hans Vandierendonck, Dimitrios S. Nikolopoulos, Peter Lawthers, Panos K. Koutsovasilis, Manolis Maroudas, Christos D. Antonopoulos, Christos Kalogirou, Nikolaos Bellas, Spyros

Lalis, Srikumar Venugopal, Arnau Prat-Pérez, Alejandro Lampropulos, Marios Kleanthous, Andreas Diavastos, **Zacharias Hadjilambrou**, Panagiota Nikolaou, Yiannakis Sazeides, Pedro Trancoso, George Papadimitriou, Manolis Kaliorakis, Athanasios Chatzidimitriou, Dimitris Gizopoulos, Shidhartha Das: An energy-efficient and error-resilient server ecosystem exceeding conservative scaling limits. DATE 2018

- Poster: Harnessing CPU Electromagnetic Emanations for Voltage Noise Characterization, <u>Zacharias Hadjilambrou</u> and Yiannakis Sazeides ACM Student Research Competition held in conjunction with Parallel Architectures and Compilation Techniques Conference (PACT18), November 2018

- Poster: Shaving the Safety Margins by Exposing Intrinsic Hardware Heterogeneity <u>Zacharias Hadjilambrou</u>, Konstantinos Tovletoglou, Panagiota Nikolaou, Charalambos Chalios, Dimitrios Nikolopoulos, Pedro Trancoso, Yanos Sazeides and Georgios Karakonstantis, ACACES 2016, July 2016

# Contents

| Chapter<br>1.1 | 1. Introduction<br>Motivation                                                |    |

|----------------|------------------------------------------------------------------------------|----|

| 1.2            | Contributions                                                                | 3  |

| 1.3            | Document Structure                                                           | 5  |

| Chapter<br>2.1 | 2. Background and Related Work<br>CPU Power and Energy-Efficiency Techniques |    |

| 2.1.           | .1 Eliminating Static-Power                                                  | 7  |

| 2.1.           | .2 Eliminating Dynamic Power Consumption (Switching Activity)                | 8  |

| 2.1.           | .3 Eliminating Dynamic Power Consumption (Voltage-Frequency Reduction)       | 9  |

| 2.2            | Power-Delivery-Networks                                                      |    |

| 2.2.           | .1 PDN Resonance-Frequencies                                                 | 11 |

| 2.2.           | .2 IR drop versus dl/dt noise                                                | 12 |

| 2.3            | Voltage Margins                                                              | 15 |

| 2.3.           | .1 V <sub>MIN</sub> Characterization                                         | 16 |

| 2.4            | Voltage Margin Elimination Techniques                                        | 17 |

| 2.5            | LdI/dt Noise Mitigation Techniques                                           | 18 |

| 2.6            | Ldl/dt noise on GPUs                                                         | 20 |

| 2.7            | EM emanations exploitation                                                   | 21 |

| 2.8            | Stress-Tests                                                                 | 21 |

| 2.8.           | .1 Performance Stress-Tests                                                  | 22 |

| 2.8.           | .2 Power-Viruses                                                             | 22 |

| 2.8.           | .3 Ldl/dt stress-tests                                                       | 23 |

| 2.9            | GA for Stress-Test Generation                                                | 24 |

| Chapter<br>3.1 | 3. GeST Framework<br>GeST Framework Description                              |    |

| 3.1.           | .1 GA Engine                                                                 | 29 |

| 3.1.           | .2 Inputs                                                                    | 34 |

| 3.1.           | .3 Measurement and Fitness Evaluation                                        | 38 |

| 3.1.           | .4 Output                                                                    | 39 |

| 3.2            | GeST Evaluation Platforms                                                    | 40 |

| 3.3                     | Power-Virus Generation                                           | 43 |

|-------------------------|------------------------------------------------------------------|----|

| 3.4                     | Voltage-Noise Virus Generation                                   |    |

| Chapte<br>4.1           | r 4. EM methodology<br>Required Experimental Apparatus           |    |

| 4.2                     | Relationship Between CPU EM Emanations and On-Chip Voltage Noise | 54 |

| 4.3                     | EM Resonance Frequency Detection (Loop Method)                   | 57 |

| 4.4                     | EM Resonance Frequency Detection (Clock Method)                  | 59 |

| 4.5                     | EM dl/dt virus Generation                                        | 61 |

| Chapte<br>Chapte<br>6.1 | 1                                                                | 70 |

| 6.2                     | ARM Cortex-A53                                                   | 72 |

| 6.2                     |                                                                  |    |

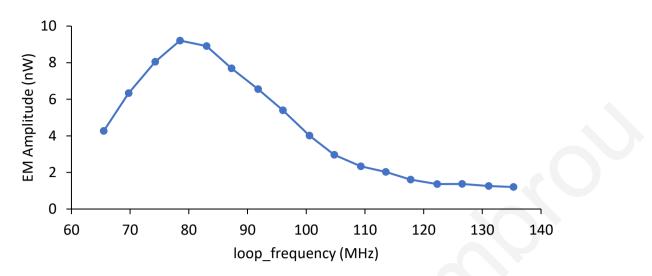

| 6.3                     | AMD Athlon II X4 645                                             | 76 |

| 6.4                     | Ampere Computing X-Gene2                                         | 78 |

| 6.5                     | Ampere Computing X-Gene3                                         | 79 |

| Chapte<br>7.1           | er 7. EM based DVS Governors<br>EM Detection Governor            |    |

| 7.2                     | Core Allocation Governor                                         |    |

| Chapte<br>8.1           | r 8. Conclusions                                                 |    |

| 8.2                     | Future Work Directions                                           |    |

| Biblio                  | graphy                                                           |    |

|                         |                                                                  |    |

|                         |                                                                  |    |

|                         |                                                                  |    |

|                         |                                                                  |    |

# List of Figures

| Figure 1. Power equations7                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

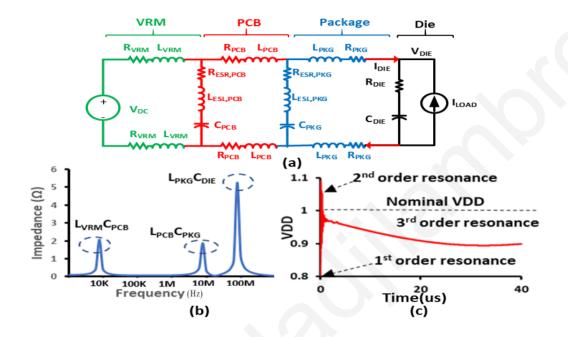

| Figure 2. (a) A simplified model of the PDN [55]. The impedance as seen by the die has multiple resonance frequencies, shown in the frequency-domain response in (b) and time-domain response to a step-current excitation in (c)      |

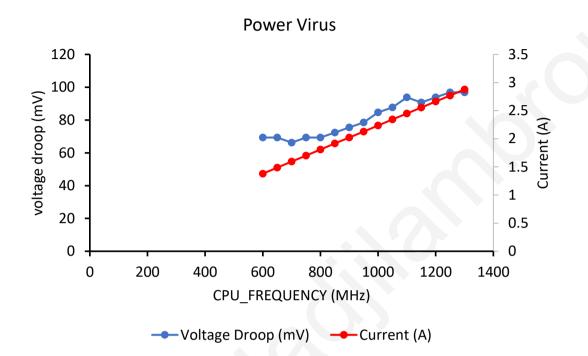

| Figure 3. Voltage droop and current consumption for a power virus at various CPU frequencies                                                                                                                                           |

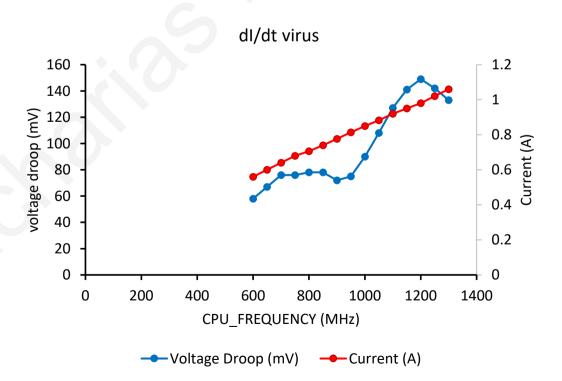

| Figure 4. Voltage droop and current consumption for a dI/dt virus at various CPU frequencies                                                                                                                                           |

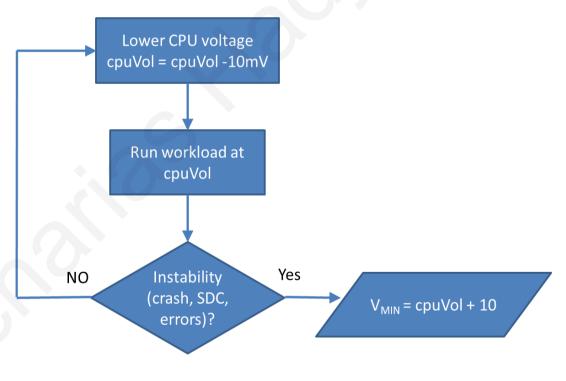

| Figure 5. V <sub>MIN</sub> characterization flow16                                                                                                                                                                                     |

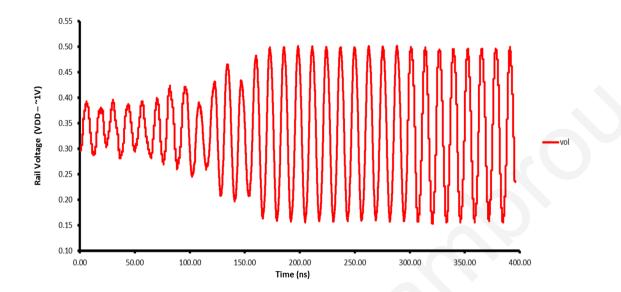

| Figure 6. Resonant buildup that leads to very high voltage droops and overshoots during dI/dt virus execution on a x86 CPU. Measured with external Oscilloscope and active differential probe connected to on-package measurement pads |

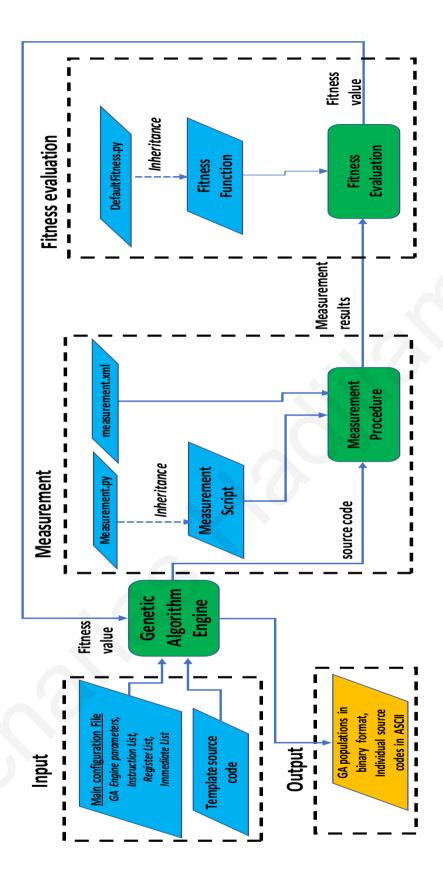

| Figure 7. GeST overview                                                                                                                                                                                                                |

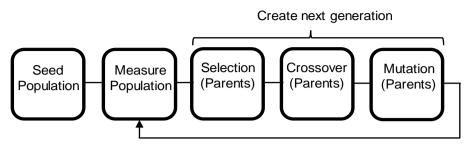

| Figure 8. A Typical GA flow                                                                                                                                                                                                            |

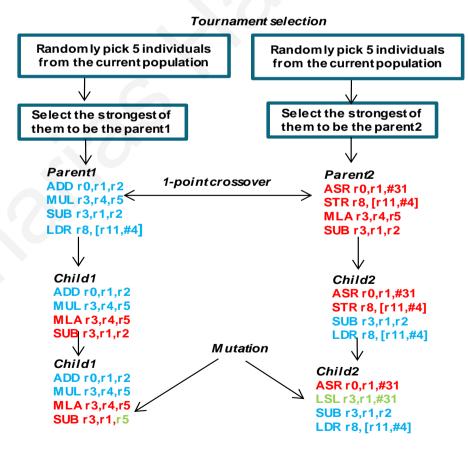

| Figure 9. Demonstration of GA operators                                                                                                                                                                                                |

| Figure 10. Example of an instruction definition and its necessary operands                                                                                                                                                             |

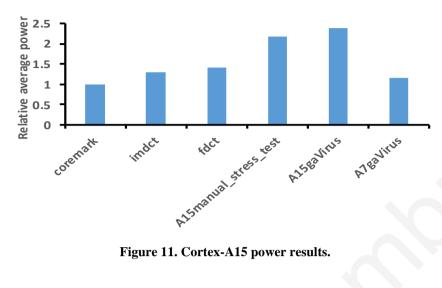

| Figure 11. Cortex-A15 power results                                                                                                                                                                                                    |

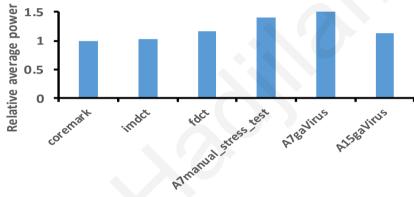

| Figure 12. Cortex-A7 power results                                                                                                                                                                                                     |

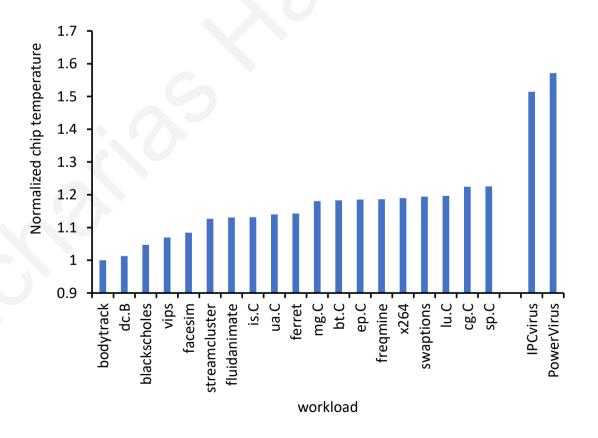

| Figure 13. X-Gene2 temperature results                                                                                                                                                                                                 |

| Figure 14. Complex fitness function rewarding high temperature and instruction simplicity.                                                                                                                                             |

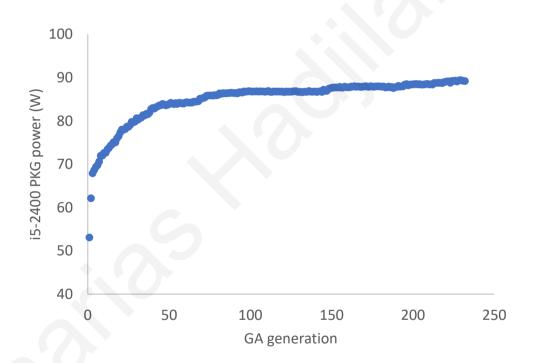

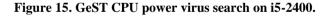

| Figure 15. GeST CPU power virus search on i5-2400                                                                                                                                                                                      |

| Figure 16. Power consumption results for Intel i5-2400                                                                                                                                                                                 |

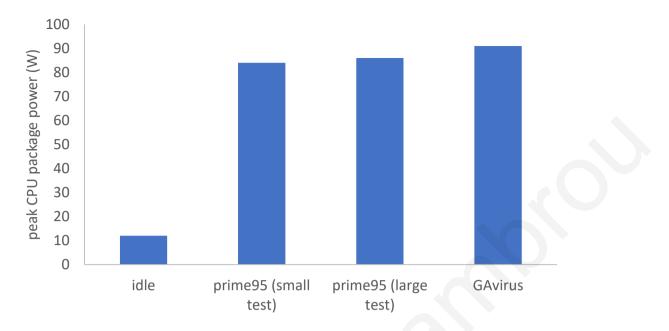

| Figure 17. Voltage-noise results on AMD Athlon CPU                                                                                                                                                                                     |

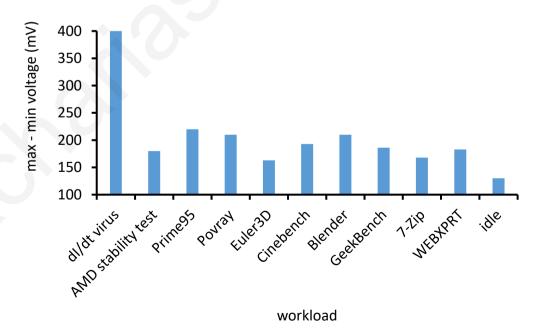

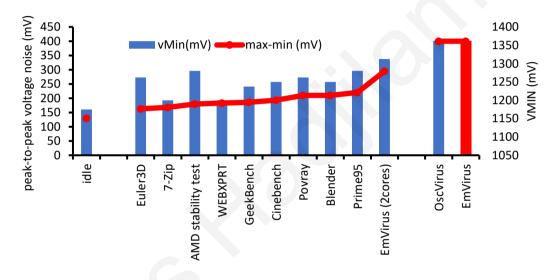

| Figure 18. V <sub>MIN</sub> results on AMD Athlon CPU51                                                                                                                                                                                |

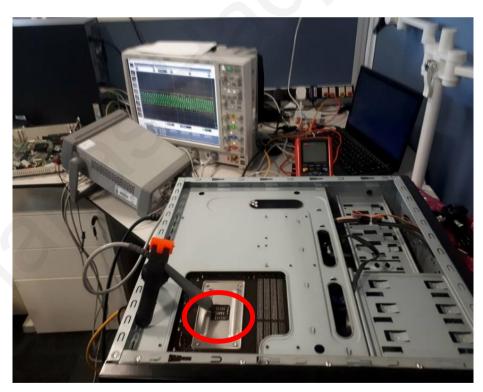

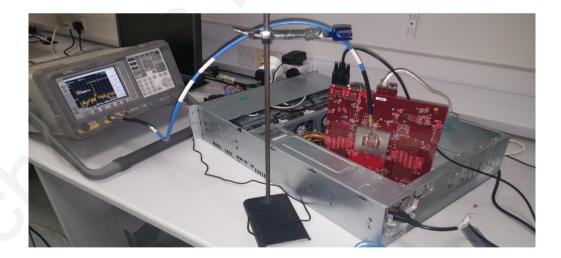

| Figure 19. Experimental setup for the ARM Juno board (left) and AMD desktop CPU (right)                                                                                                                                                |

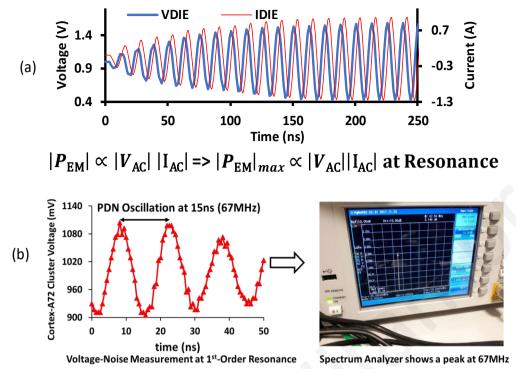

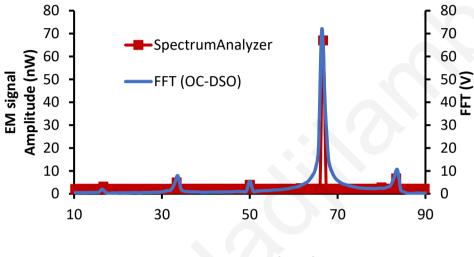

| Figure 21. a) Simulated waveforms showing the die voltage (VDIE) and die current (IDIE) in the simplified PDN model in Fig. 2. A pulsing ILOAD triggers the first-order resonance where the AC-component of both VDIE (Vac) and IDIE (Iac) maximize, thus maximizing the radiated EM power. b) Resonant oscillations (close to the resonance-frequency at 67MHz) triggered on an ARM Cortex-A72 cluster (on ARM Juno Platform) causes a corresponding peak in the measured EM power captured on a Spectrum Analyzer56 Figure 22. Comparison of spectrum analyzer readings (left axis) with FFT of OC-DSO voltage readings (right axis) during execution of a dI/dt virus. The two measurements agree as they reveal spikes at the same frequencies |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 23. EM resonance frequency exploration for Cortex-A72 PDN with loop method.58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

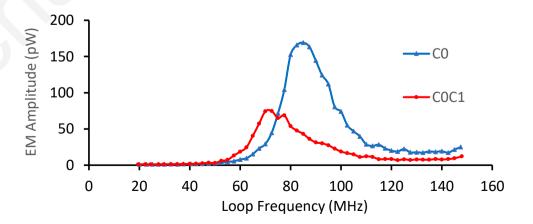

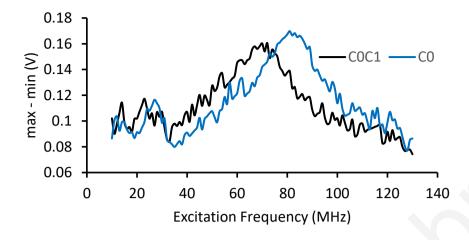

| Figure 24. SCL stimulus reveals a resonance frequency in the range of 66-72MHz with two powered cores (C0C1) and 80-86MHz with one powered core (C0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 25. Resonance-Frequency exploration on Cortex-A72 with clock method60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

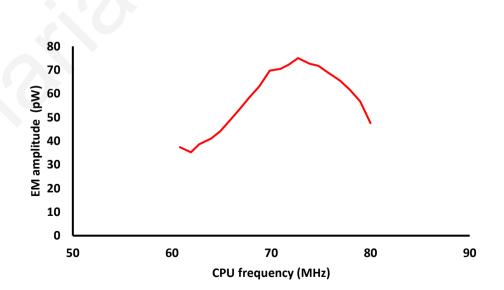

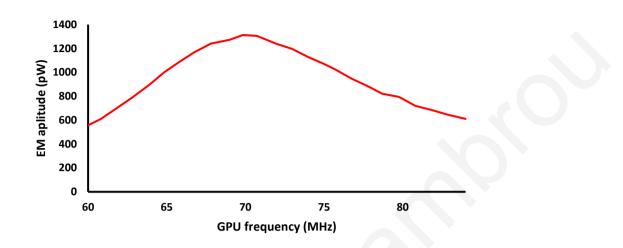

| Figure 26. Resonance frequency exploration on Mali-T622 with the clock method61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

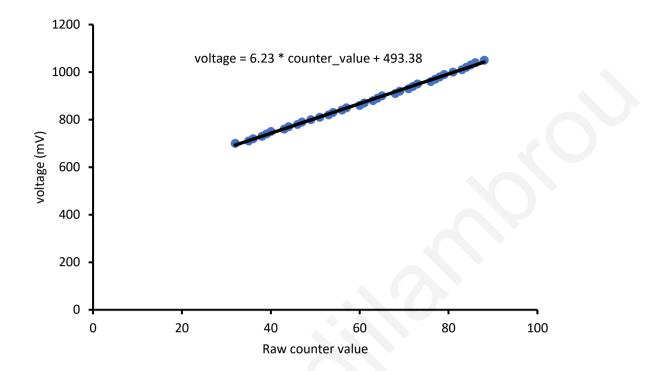

| Figure 27. OC-DSO calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

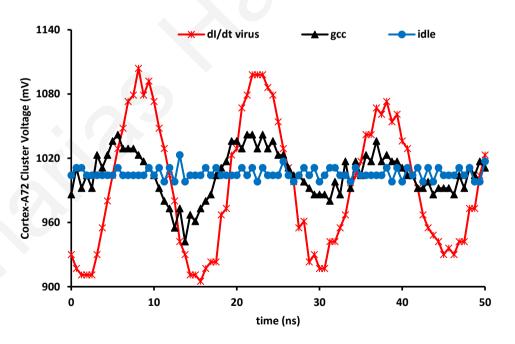

| Figure 28. Voltage waveforms obtained from OC-DSO for 3 different workloads. dI/dt virus causes the largest voltage noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

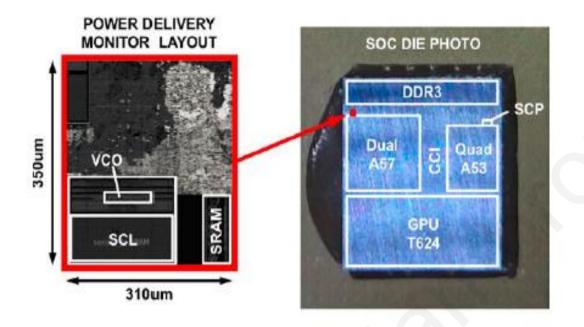

| Figure 29. The Power-Delivery-Monitor layout on the left and on the right a die photo of a JUNO R1 SoC [73] (Juno R1 uses the Cortex-A57 CPU whereas the Juno R2 uses the Cortex-A72, apart from some differences in CPU micro-architecture the two SoCs are identical)                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 30. AMD time-domain supply-voltage measurement setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

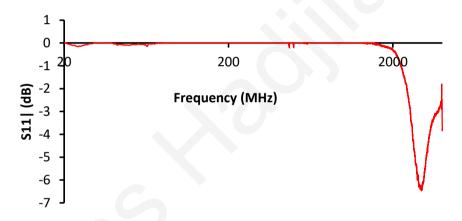

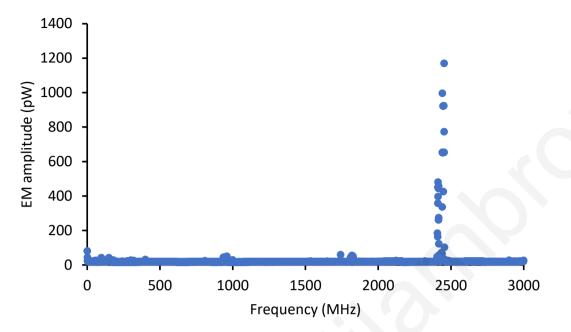

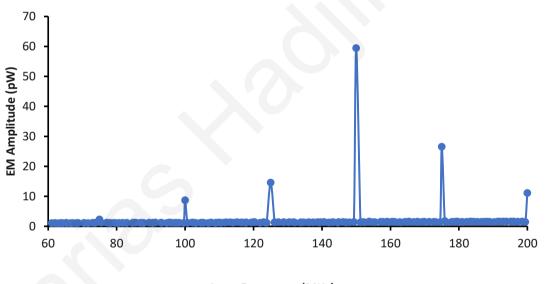

| Figure 31. Measurement of random signals in the frequency-spectrum of 1 to 3000MHz.69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

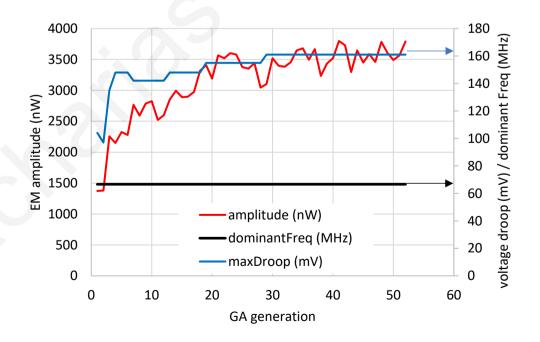

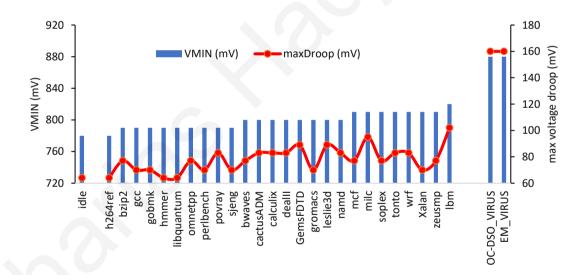

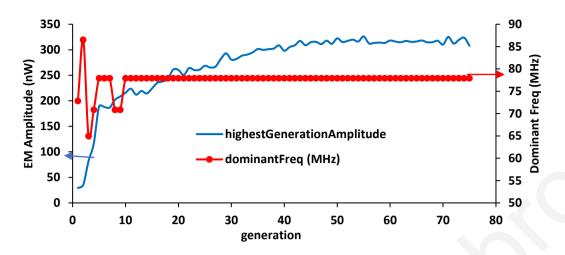

| Figure 32. EM driven GA run on Cortex-A72. Peak amplitude (left y-axis) and maximum droop / dominant frequency (right y-axis) for the best individual of each GA generation. 70 Figure 33. Voltage droop and V <sub>MIN</sub> measurements on Cortex-A72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

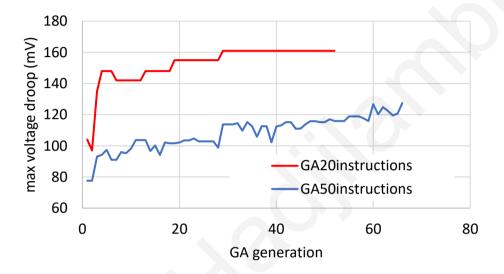

| Figure 34. GA search for Cortex-A72 dI/dt virus with 20 loop instructions vs 50 loop instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 35. GA EM amplitude driven optimization for Cortex-A5373                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------|

| Figure 36. V <sub>MIN</sub> measurements on Cortex-A53                                                                           |

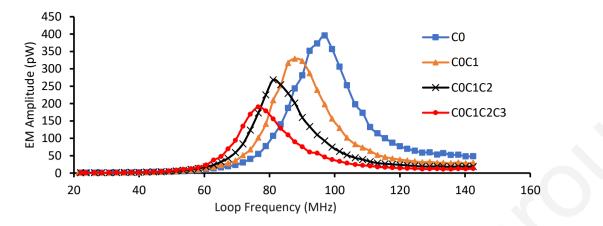

| Figure 37. Resonance frequency exploration on Cortex-A53. For four powered cores (C0C1C2C3) the resonance frequency is 76.5MHz74 |

| Figure 38. Simultaneous monitoring of voltage emergencies across multiple voltage domains through EM emanations                  |

| Figure 39. Loop frequency sweep on Athlon II X4 645 reveals a resonance frequency at 78MHz                                       |

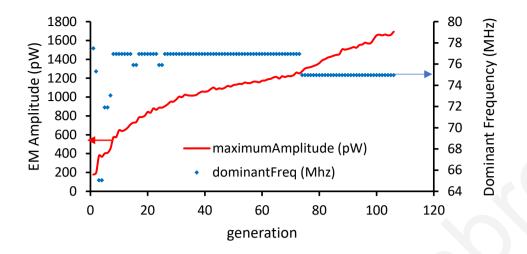

| Figure 40. GA EM amplitude driven run on AMD CPU77                                                                               |

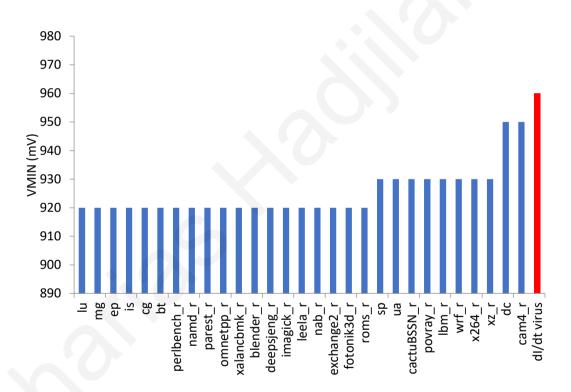

| Figure 41. V <sub>MIN</sub> and voltage noise measurements on the AMD CPU                                                        |

| Figure 42. X-Gene2 resonance frequency exploration                                                                               |

| Figure 43. GA search on X-Gene280                                                                                                |

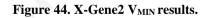

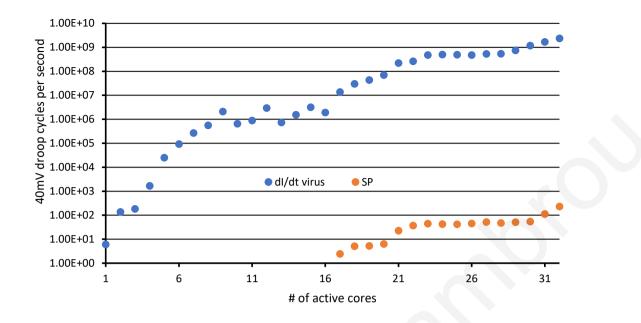

| Figure 44. X-Gene2 V <sub>MIN</sub> results                                                                                      |

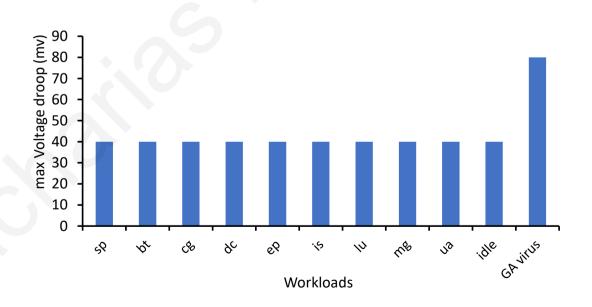

| Figure 45. Voltage droop of virus vs NAS workloads                                                                               |

| Figure 46. Cycles suffered droop per second versus number of active cores                                                        |

| Figure 47. V <sub>MIN</sub> measurements on X-Gene 3                                                                             |

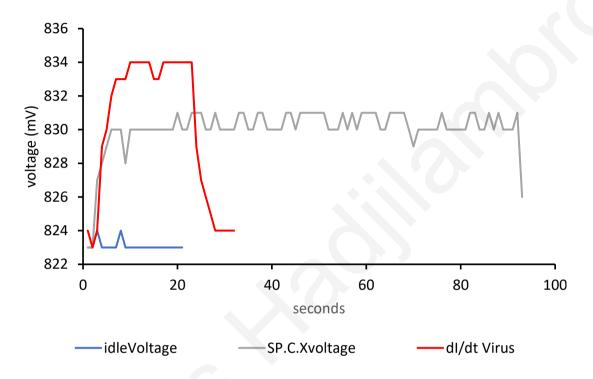

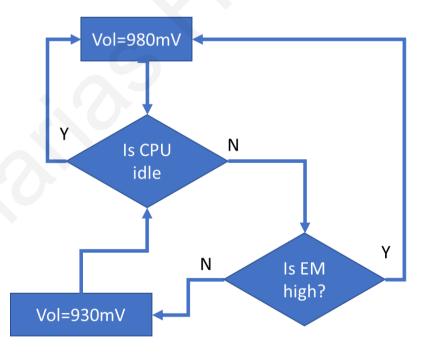

| Figure 48. Voltage over time for 3 different workloads (idle, SP and dI/dt virus)                                                |

| Figure 49. DVS governor EM detection setup on X-Gene2                                                                            |

| Figure 50. EM predictor flow-chart                                                                                               |

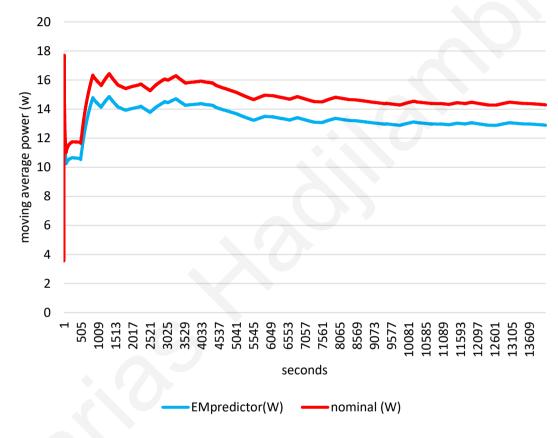

| Figure 51. EM predictor vs nominal                                                                                               |

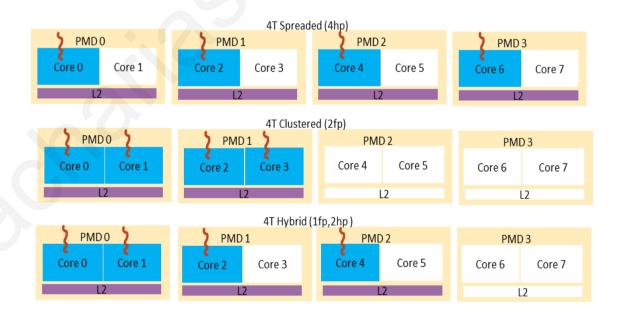

| Figure 52. Different core-allocation classes for 4 active threads. Idle cores and L2 are                                         |

| illustrated with white colour                                                                                                    |

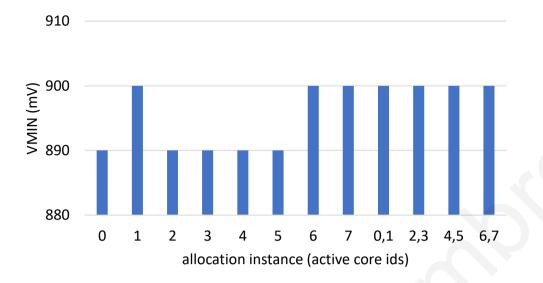

| Figure 53. Single core and PMD V <sub>MIN</sub> characterization                                                                 |

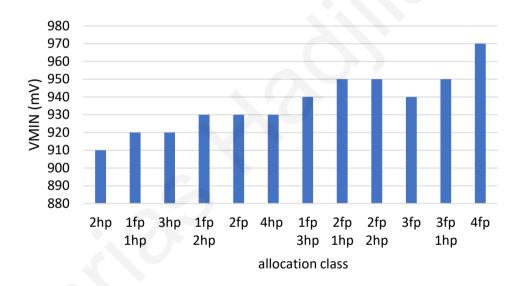

| Figure 54. Allocation class V <sub>MIN</sub> characterization                                                                    |

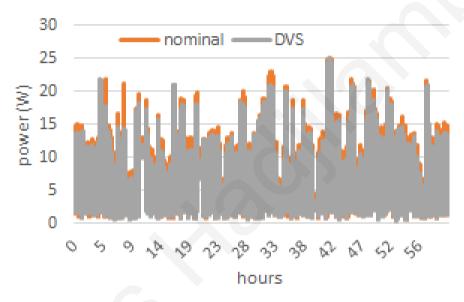

| Figure 55. CPU power consumption over 60 hours workload                                                                          |

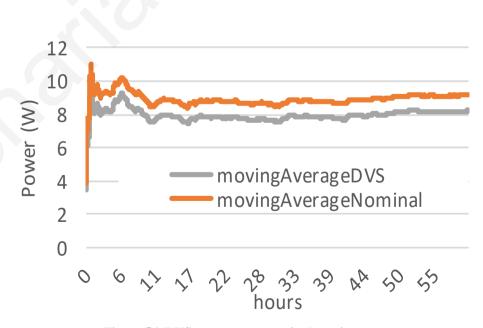

| Figure 56. DVS governor vs nominal moving average                                                                                |

# List of Tables

| Table I. Comparison of related work on GA frameworks                                  | 25    |

|---------------------------------------------------------------------------------------|-------|

| Table II. GA parameters                                                               | 34    |

| Table III. GeST evaluation platforms                                                  | 41    |

| Table IV. Instruction breakdown of Cortex-A15 and Cortex-A7 power viruses             | 43    |

| Table V. Power virus, simple power virus and IPC virus comparison.                    | 46    |

| Table VI. Experimental platforms.                                                     | 64    |

| Table VII. All X-Gene2 core allocation classes.                                       | 90    |

| Table VIII. dI/dt virus comparison. SL denotes short latency and LL denotes long late | ency. |

| Voltage margin = Nominal voltage – VirusVmin                                          | 97    |

## **Chapter 1. Introduction**

### **1.1 Motivation**

The combination of higher current demand at scaled supply-voltages [66], high operating frequencies, aggressive low-power techniques [39] and increasing core-counts exacerbate supply-voltage noise for CPUs both in mobile [20][46][47] and server/desktop [10][42][49] market segments. Large voltage noise is a threat to robust execution because when the supply voltage drops below a certain threshold, timing violations or bit-flips may occur [10][39][66]. This may lead to silent data corruption (SDC), application or system crashes and general system instability [42][73].

Manufacturers budget voltage margins (or guardbands) to ensure robustness even in the presence of worst-case voltage noise conditions<sup>1</sup>. Consequently, production systems are typically operated at a higher supply voltage (and/or lower clock-frequency) than necessary under nominal operating conditions. Accurate determination of voltage margins is critical since optimistic margining (where the added margins are not adequately provisioned for the rare worst-case noise event) can cause abrupt system-failures in the field. Conversely, excessive margining adversely impacts CPU energy-efficiency [9][10][42][44][56][66].

A key aspect of margining production systems is the determination of the worst-case inductive component (referred to as "LdI/dt" or "dI/dt") of the voltage noise [10]. LdI/dt events are abrupt changes in CPU current demand that cause voltage noise oscillations excited at the Power-Delivery-Network (PDN) 1<sup>st</sup> order resonance-frequency. The dI/dt voltage-noise component typically dominates over the resistive component (referred to as "IR") in the PDN of modern computing systems [20][44][55]. In comparison with aperiodic

<sup>&</sup>lt;sup>1</sup>Voltage margins are also necessary for variation effects such as temperature hot-spots, circuit-aging and process-variation [63]. However, system-margins are typically stressed most due to LdI/dt or inductive transients. Their fast-moving nature [21][44] renders them difficult to compensate for using traditional adaptive techniques.

or isolated dI/dt events, periodic current modulations at the 1<sup>st</sup> order resonance-frequency reinforce the resonant noise even further [63], thereby maximally stressing system-margins.

Commercial Electronic Design Automation (EDA) tools [5][6][15] cannot accurately model the time-varying CPU current due to the complex hardware/software interactions, particularly in multi-core configurations [10]. Consequently, design-time PDN optimization is inadequate and post-silicon characterization is essential for margining production systems [10][47]. Post-silicon characterization typically relies upon synthetic virus workloads, referred to as dI/dt stress tests (dI/dt viruses) [10]. Due to the inherent complexity of manually crafting these tests, previous work [10][41][42] introduced frameworks for automated generation of stress tests based on optimization techniques such as Genetic Algorithms (GA). These approaches rely upon the capability of the platform-under-test to support high-bandwidth monitoring of on-chip voltage rails or direct voltage measurements.

There are two main approaches for direct voltage measurement: 1) specialized on-chip circuitry integrated into the system at design-time [2][31][46][48][53][72] and 2) voltage sense pins located on the package [3][36][42][66] (also known as Kelvin measurement points). Unfortunately, these capabilities are not yet mainstream features, particularly in cost- and resource-constrained mobile platforms. Moreover, on-chip approaches incur the Non-Recurring Engineering (NRE) design-time costs for hardware development and system integration. In cases where the voltage monitor is integrated into the system as a peripheral device, it requires additional software support (in terms of a device driver) to configure, calibrate and query. Alternatively, on-package measurement points directly connected to on-chip voltage rails do not incur design-time NRE overheads. Nonetheless, they require a dedicated pair of Controlled Collapsible Chip Connection (C4) [22] bumps for each voltage domain. This consumes valuable C4 resources that could otherwise be used for direct powerdelivery. Consequently, such support is not usually provided in resource-constrained platforms such as mobile CPUs (e.g. the Cortex-A53 CPU used in this thesis).

2

In this thesis, we propose an alternative approach for post-silicon PDN characterization. The proposed approach relies upon sensing CPU electromagnetic (EM) emanations using an antenna and a spectrum analyzer connected to the antenna. Compared to direct-measurement, our approach offers the following unique advantages for resonant voltage noise analysis: a) is non-intrusive, as no physical connection to the CPU is required, b) has zero-overhead, as it does not require design time, development effort, on-package and on-chip resources, and c) is cross-platform, as it can be applied to virtually any platform.

Due to its general applicability, we believe that our approach provides a fundamentally new way for benchmarking commercial systems and at the same time democratizes PDN characterization and voltage noise research. Voltage noise visibility is not typically available in motherboards and researchers do not usually have access, when available, to proprietary on-chip voltage noise circuits. Consequently, voltage noise visibility is limited to chips and motherboards that expose high bandwidth voltage measurements points. The proposed EM methodology removes these constraints by allowing basic PDN characterization to be performed on any CPU and motherboard without the need for direct fine-grained voltage measurements.

### **1.2 Contributions**

This thesis explains the theoretical basis and provide conclusive evidence for the correlation between on-chip voltage noise and emanated EM power. Our measurements demonstrate that both on-chip voltage noise and EM signal power are maximized at the 1st-order resonance frequency. We leverage this observation to propose a convenient, zero-overhead, cross-platform and non-intrusive way for PDN characterization. We demonstrate that with the proposed EM approach, it is possible to: a) monitor periodic voltage-noise of large amplitude b) generate dI/dt stress tests within a GA framework that optimizes towards a maximum EM signal amplitude, c) rapidly measure the 1st-order resonance frequency, d)

detect resonance frequency shifts due to capacitance changes in multi-core configurations, e.g. due to dynamically switching on or off cores in a CPU cluster, e) construct Dynamic-Voltage-Scaling (DVS) governors that are based on real-time EM monitoring and the minimum-operational-voltage ( $V_{MIN}$ ) of the EM dI/dt viruses; these DVS governors provide at least 10% power-savings over nominal voltage settings.

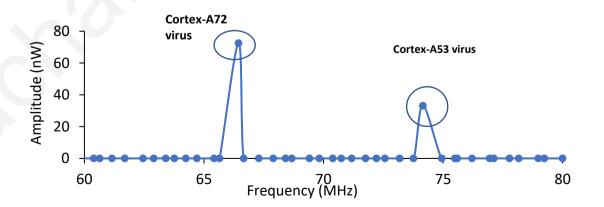

Furthermore, this thesis establishes the cross-platform applicability of the EM approach by successfully applying it to different CPUs and Instruction Set Architectures (ISA). We characterize the PDN for individual CPUs across separate platforms and distinct processorclusters integrated on the same die. In particular, the EM methodology is applied on five different CPUs: two ARM multi-core CPU clusters (dual-core Cortex-A72 and quad-core Cortex-A53) hosted on a Juno Board [7], one x86-64 AMD desktop CPU (Athlon II X4 645) and two Ampere Computing X-Gene ARM server CPUs (X-Gene2 8-core and X-Gene3 32-core). Thus, the proposed approach is shown to work across CPUs of different market segments (mobile, desktop and server), different ISAs (ARM and x86), different CPU micro-architectures, different technology nodes and on CPUs that do not offer direct voltage measurements such as the Cortex-A53 and the X-Gene2 CPU. The efficacy of the EM approach is validated through direct voltage measurements (where it is feasible) and V<sub>MIN</sub> determination (minimum stable operational voltage for a given frequency).

Finally, for the experimental needs of this thesis, the GeST (Generating Stress-tests) framework has been developed. GeST is a GA based framework for generating stress-tests. The EM methodology utilizes GeST for generating dI/dt viruses. GeST framework's source code has been released to public. While GA based automatic frameworks for generating stress-tests is not a novel concept, GeST is to the best of our knowledge the first publicly available framework that researchers and practitioners can use for generating stress-tests. The main strengths of GeST are its flexibility and extensibility as GeST can be extended to support virtually any optimization metric, any measurement instrument and any target

platform. This renders GeST an ideal platform for researchers to experiment with and build upon.

## **1.3 Document Structure**

The remainder of this thesis is the following. Chapter 2 discusses the theoretical background of this thesis, this includes among other subjects: a) CPU energy-efficiency, b) PDN and voltage-noise, c) dI/dt and power-viruses, d)  $V_{MIN}$  characterization, e) prior work related to exploitation of EM emanations, and f) related work on GA stress-test generation frameworks.

Chapter 3 presents and evaluates the GeST framework. We delve into the architecture, implementation and usage details of the GeST framework. We also demonstrate the framework's effectiveness by generating power, IPC and dI/dt viruses on several CPUs.

Chapter 4 proposes the EM methodology. Specifically, Section 4.1 provides the experimental apparatus required for the proposed approach, Section 4.2 provides both the theoretical explanation and the experimental findings that prove the correlation between inductive PDN voltage-noise and EM radiation. Sections 4.3, 4.4 provide the methodologies for resonance-frequency detection, and, Section 4.5 provides the methodology for dI/dt virus generation where we utilize GeST to conduct a GA search that optimizes towards high EM amplitude.

Chapter 5 presents the experimental platforms where we evaluate the EM methodology. Chapter 6 evaluates the EM methodology by detecting the resonance-frequency and generating dI/dt viruses for the Cortex-A72, Cortex-A53, AMD Athlon II X4 645 CPU, X-Gene2 and X-Gene3 CPUs. Chapter 7 proposes and evaluates on the X-Gene2 CPU two DVS governors based on the EM methodology. Finally, Chapter 8 concludes this thesis.

# Chapter 2. Background and Related Work

This Chapter provides this thesis' theoretical background and related work. The Chapter starts by discussing the factors that contribute to the CPU power-consumption and common techniques for improving the CPU energy-efficiency such as power-gating, clock-gating, DVFS, DVS etc. Then it discusses the fundamentals of PDNs and the voltage-noise phenomenon. Voltage-noise is one of the main subjects of this thesis. Therefore, we will delve deeply into related work on mitigating voltage-noise. We also provide background information on stress-tests (dI/dt viruses, power-virus, IPC viruses), V<sub>MIN</sub> characterization and all the prior work related to GA frameworks for stress-test development.

This thesis harnesses EM emanations for PDN characterization. This approach has been inspired from prior work that exploits EM emanations for other purposes (e.g. performanceprofiling, security exploits etc.). Therefore, in this Chapter we also discuss related work in exploiting CPU EM emanations.

### 2.1 CPU Power and Energy-Efficiency Techniques

Figure 1 illustrates the components of the CPU power-consumption. The CPU powerconsumption is attributed to two major factors: a) the static power-consumption, and b) the dynamic power-consumption. The static power contribution comes from the leakage current. Leakage current is always consumed regardless of the CPU activity. In contrast, dynamic power-consumption depends on CPU activity. The dynamic power is composed of: a) the voltage-frequency (these are mentioned together because their values are intertwined) and b) the switching activity. The switching activity is equal to the activity factor multiplied by the capacitance. A lot of work has been performed for improving the energy-efficiency and reducing the power-consumption of multi-core general-purpose CPUs. The techniques for reducing the power-consumption can be broken down into three categories: a) techniques that deal with static power, b) techniques that deal with dynamic power consumption through switching-activity reduction, and c) techniques that deal with dynamic power consumption through voltage and frequency reduction.

$P_{\text{static}} = V * I_{\text{leak}}$

$\mathbf{P}_{\text{dynamic}} = \mathbf{V}^2 * \mathbf{F} * \mathbf{C} * \mathbf{A}$

$P_{total} = P_{dynamic} + P_{static}$

V (voltage) F (frequency) C (capacitance) A (activity-factor)

Figure 1. Power equations.

#### 2.1.1 Eliminating Static-Power

First, we discuss static power-consumption reduction techniques. Power-gating is probably the most well-known static power elimination technique. Power-gating is performed by detecting idle transistors and turning them off (essentially disconnecting them from the PDN). Power-gating can be applied at the level of a cache line, a functional unit, a whole core or even a whole CPU cluster (e.g. in the case of big. Little chips). Power gating can be detrimental to energy-efficiency if it is not performed at the right time. The gating must be applied long enough to justify the delay and the dynamic-power spent to powerback the transistors. In a typical power-gating implementation a mechanism counts the idle time of a functional unit; if a threshold idle time is reached, then, the functional unit enters a power-gated state. Power-gating has more power saving potential on floating points units compared to integer units. The reason is that integer units are more utilized, hence, they offer less power gating opportunity. Power gating a whole core or CPU cluster can be instructed from OS using the ACPI interface, whereas power-gating of functional units is performed within the hardware. The power gated states as defined by ACPI interface start from C6 [83] state and above.

Caches are perhaps the most promising component for applying power-gating. Previous work [84] shows that most of the time (80% of workload execution) cache lines are dead. Dead means that they will not be used again. This motivates the concept of cache decay which basically is a mechanism that tries to guess whether a cache line is dead or alive. Dead caches can be power gated to save power. Of-course cache decay again incurs the risk of wrong prediction. A wrong prediction might cause an otherwise unnecessary cache miss that will have detrimental impact on both performance and energy.

The drowsy caches is an alternative approach for reducing static power consumption. This approach may not have the same power saving potential as cache decay but is less prone to detrimental effects. Drowsy caches exploit the fact that to preserve a cache line's state a lower voltage can be applied. Of course, when the cache line must be accessed the normal voltage has to be applied back. But during times when a cache line is not accessed, to save static power the voltage is lowered just enough to preserve the cache line values. The performance penalty of the drowsy cache mechanism is due to the latency to scale back to normal voltage. The performance penalty is very small (1%), therefore, related work proposed to put all the cache periodically regardless of usefulness into the drowsy mode for substantial energy savings [84].

#### 2.1.2 Eliminating Dynamic Power Consumption (Switching Activity)

The next power saving techniques category to be discussed is related to switching activity reduction. Clock-gating is the most common switching activity reduction technique. The motivation behind clock-gating is the following. During a CPU cycle a functional unit might be idle i.e. no instruction is scheduled to execute on that functional unit. Still, switching activity is wasted even when functional units are idle because of the clock signal causing unwanted bit toggling. Clock-gating prevents unnecessary switching due to clock signal. This is achieved by placing an AND gate between the clock signal and the flip-flops. The AND operation is performed on the clock signal and a control signal. The control signal is equal to 1 to allow the clock to reach the flip flops, unless a functional unit is idle for 1 cycle or more. In that case the control signal is equal to 0 to not allow the clock to reach the flip flops. Clock gating can be performed at various granularities. Clock-gating is commonly used in functional units, the power savings are less compared to power-gating, but clock-gating is more performance friendly since the latency for returning to operational state is negligible. Clock gating can be performed for the whole core in various degrees as defined by ACPI C1-C3 states. Like for the power gating C6 state, OS can orchestrate the core C1-C3 states transitions. Researchers have proposed even more finer grain clock-gating by gating unused bit width of functional units [84]. The motivation stems from the fact that registers are very wide 32 and 64 bit, but most instructions can be satisfied with only 16bits.

# 2.1.3 Eliminating Dynamic Power Consumption (Voltage-Frequency Reduction)

Next, techniques for reducing voltage and frequency are discussed [84]. Nearly, all modern general-purpose CPUs and GPUs use Dynamic voltage and frequency scaling (DVFS) to save energy. The motivation behind DVFS is that many workloads have significant slack that can be exploited to run the workload at a slower speed and save energy at the same time. Input/output (I/O) and memory latency dominated workloads provide good opportunity for DVFS. Let us take as example a text processor application. This is a relatively easy computational application with a lot of I/O and relatively relaxed response-time requirements (a person types about a character every 200-300ms) that does not justify operating the CPU at the highest CPU frequency all the time. Instead, we can lower the CPU frequency and the voltage to save significant amount of power (recall from Section 2.1 that power depends quadratically on voltage) while keeping a satisfying performance level and

response-time for the user. Like any other power management technique DVFS poses a risk of detrimental impact in performance. To avoid undesired performance reduction DVFS must be used only when substantial compute slack is available. The most common proxy for estimating compute slack and guiding DVFS decisions is the CPU utilization. Low CPU utilization implies opportunity for voltage and frequency reduction. DVFS decisions are usually guided by OS. Hardware usually exposes various voltage-frequency points (also known as performance-points or P-States) to the OS. The OS communicates to the hardware the desired performance level through the ACPI interface. A commonly used OS level DVFS interface is the cpufreq Linux utility.

Lowering only the frequency (DFS) (without lowering the voltage as well) can be beneficial in circumstances where the system is thermally constrained or when workload is dominated by main memory latency. But, for non-thermal and non-memory-latency constrained scenarios, performing DFS most probably is not beneficial for energy-efficiency because the power-consumption decrease is proportional to the workload execution time increase (frequency affects both power and performance linearly). Therefore, for energysavings we usually use DVFS which scales down both voltage and frequency.

Finally, besides DVFS, lowering only the voltage i.e. DVS can be also applied for dynamic power reduction. Lowering the voltage without scaling the frequency reduces the available voltage noise margin. If voltage drops very low error can happen. Therefore, DVS is a less common practice than DVFS. DVS requires either detection, correction and roll-back mechanisms [34] to deal with potential instability due to low voltage [21], or ability to monitor critical path and adjust voltage accordingly [44].

### 2.2 Power-Delivery-Networks

#### 2.2.1 PDN Resonance-Frequencies

Figure 2 (a) shows a simplistic representation of the PDN of a die-package-PCB system [20][55]. The current demand due to on-chip switching transistors is modelled as a lumped current source, I<sub>LOAD</sub>. Explicit decoupling capacitors (henceforth, referred to as decaps) and non-switching, but powered-on, transistors act as localized charge reservoirs that provide the high-frequency component of the demand current, ILOAD. The on-chip power-grid resistance is modelled as a lumped resistor, R<sub>DIE</sub>, connected in series with C<sub>DIE</sub>. The total die current (I<sub>DIE</sub>) is sourced through the inductive power-line traces of the package and the PCB, represented by a series R-L (resistor, inductor) equivalent circuit. The discrete decaps on the PCB and package are represented by an ideal capacitance ( $C_{PKG}$ ,  $C_{PCB}$ ) in series with its effective series inductance (ESL) and effective series resistance (ESR). Figure 2(b) shows the input impedance of the distributed RLC network as seen from the die. The impedance spectrum shows multiple resonance peaks due to multiple LC-tank circuits. The highest impedance peak, referred to as the 1st-order resonance peak is attributed to the diecapacitance (CDIE) interaction with its counterpart inductance (LPKG). The 1<sup>st</sup>-order resonance also occurs at the highest frequency (50MHz-200MHz) compared to the 2<sup>nd</sup>- (~1-10MHz) and 3<sup>rd</sup>-order (~10KHz) resonances that are due to downstream capacitor networks.

The resonance frequencies also manifest in the time-domain when the PDN is excited by a step-current excitation (Figure 2 (c)). Micro-architectural events such as branch mispredictions [20] can trigger these oscillations in the PDN. Power-supply oscillations of larger magnitudes can be set off within the supply network due to sustained program activity with alternating periods of high-current and low-current consumption within a loop (e.g. due to dI/dt virus) [42][73]. When the frequency of the time-varying current aligns closely with the 1st-order resonance frequency, voltage oscillations are maximized in amplitude. High voltage oscillations can lead to bit-flips in arrays, timing errors in logic paths [42][65][66][73] and reliability issues due to gate-oxide stress [1][65]. Such periodic events often result in system/application crashes and/or incorrect execution output [42][56].

Figure 2. (a) A simplified model of the PDN [55]. The impedance as seen by the die has multiple resonance frequencies, shown in the frequency-domain response in (b) and time-domain response to a step-current excitation in (c)

#### 2.2.2 IR drop versus dI/dt noise

This thesis focuses on the dI/dt voltage-droop (or AC droop) but the total voltage-droop magnitude does not solely depend on the dI/dt effect. The magnitude of a voltage-droop is the sum of the dI/dt and the IR droop (or DC droop) [10]. As illustrated in Figure 2 a PDN includes resistive and inductive PDN components. The resistive PDN components (R<sub>VRM</sub>, R<sub>PB</sub>, etc.) produce the IR drop, whereas the inductive components (L<sub>VRM</sub>, L<sub>PCB</sub>, etc.) produce the dI/dt droops. IR drops can be mitigated with techniques that compensate the voltage drop by dynamically adding a voltage-offset during runtime. A well-known technique for dynamic voltage-offsetting is the Load-Line calibration. Load-Line calibration is available on most high-performance PCBs. In contrast to IR droops, dI/dt droops due to their fast-

moving nature cannot be compensated with Load-Line calibration. Other more advances techniques must be employed (that are discussed in the next Sections of this Chapter).

IR and dI/dt voltage droops are stimulated by different factors and they are generated by different workloads. IR drop increases proportionally to the CPU power-consumption. Broadly speaking, higher CPU frequency and higher current draw lead to higher IR drop. Contrary, to raise the dI/dt droop, repetitive high current stimulus at a rate equal to the 1<sup>st</sup> order resonance-frequency is required. Therefore, increasing the CPU frequency while executing a resonant workload will not necessary increase the voltage-droop.

To illustrate these differences we run and measure the voltage droop caused by two different workloads: a) a power-virus that targets maximum power-consumption, and b) a dI/dt virus that targets the PDN resonance-frequency by causing sudden high current-draw at a rate equal to the resonance-frequency. We perform this experiment on a Cortex-A57 CPU hosted on an ARM Juno board. This CPU supports measuring dI/dt voltage-droops through a high-bandwidth On-Chip-Digital-Storage-Oscilloscope (OC-DSO). We run the two workloads for different CPU frequencies. At each frequency we measure the current draw and the voltage-droop. Figure 3 shows the power-virus' results and Figure 4 shows the dI/dt virus' results.

First and foremost, the figures confirm two fundamental expectations: a) that the powervirus draws significantly more current than the dI/dt virus and b) that the current consumption grows linearly to the CPU operating frequency for both workloads. Regarding voltage-droop, the measured voltage-droop for the power-virus shows linear dependence with the CPU frequency. This is the case because the power-virus exercises the IR drop. In contrast, the dI/dt virus measured droop does not show linear dependence to the CPU frequency. The dI/dt virus exercises the dI/dt droop. Hence, the measured voltage droop increases with CPU frequency until the resonance-frequency is achieved. This occurs at 1.2GHz, this is the operating CPU frequency at which the dI/dt virus stresses the resonancefrequency. Further increase in the CPU frequency moves the virus's stress-frequency beyond the 1st-order resonance. This causes a reduction in the measured voltage droop.

Figure 3. Voltage droop and current consumption for a power virus at various CPU frequencies.

Figure 4. Voltage droop and current consumption for a dI/dt virus at various CPU frequencies.

### 2.3 Voltage Margins

The classic approach for dealing with voltage-noise is adding a voltage margin i.e. running the chip at a higher voltage to provision for worst case voltage droops [63]. This is very practical for ensuring robust execution, but it leads to unnecessary waste of power. Usually the voltage margins are much more pessimistic than required. Manufacturers are forced to set pessimistic voltage margins because workload variations render the in the field voltage-droop magnitude very hard to predict. Moreover, due to hardware static variations, some parts may have higher tolerance to voltage-droops than others. Therefore, a voltagemargin that ensures robust execution for a slow part, limits the energy-efficiency of a faster part. Ideally, each chip should adopt different margins.

A partial solution to the issue of pessimistic margining is the speed-binning (or frequency-binning). Speed-binning refers to making different product models out of the same chips [63]. The chips are categorized to speed-bins (frequency-bins) after running various representative test workloads on all chips. Broadly speaking the product models will differ on their advertised nominal operating frequency (e.g. Model X runs at 3GHz, Model Y runs at 2.8GHz etc.) and on their price. With speed-binning the faster chips are not forced to work at slower frequencies and this partially solves the energy-inefficiency issue. But speed-binning does not tackle completely the issue of static variations as even in the same frequency-bin static variations still exist.

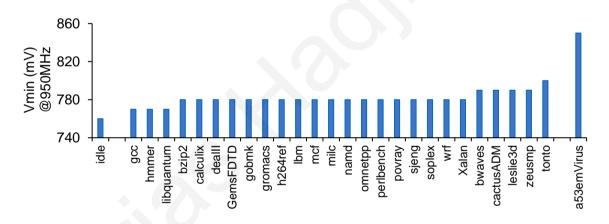

Constructing dI/dt viruses and characterizing their  $V_{MIN}$  is another approach for reducing the pessimistic margins [10]. As we show in this thesis and in prior work [42], the  $V_{MIN}$  of a proper dI/dt virus is higher than the  $V_{MIN}$  of conventional workloads, thereby, the dI/dt virus's  $V_{MIN}$  can be used as a guideline to determine the operating voltage for a given frequency.

#### 2.3.1 V<sub>MIN</sub> Characterization

$V_{MIN}$  is the minimum voltage at which a chip (CPU, GPU etc.) operates correctly for a given frequency. A chip can have different  $V_{MIN}$  per workload as the execution paths and the voltage droop magnitude differs from workload to workload. To determine a workload's  $V_{MIN}$  we perform  $V_{MIN}$  characterization. This procedure involves running the workload for various voltage values until instability is observed. Typically, the  $V_{MIN}$  characterization starts from high voltage and after each successful workload execution, the voltage is lowered in increments of 10mV. The  $V_{MIN}$  test stops at the first voltage where instability is observed (SDC, crash etc.). This voltage is tagged as the crash-point. The  $V_{MIN}$  is equal to the crash-point plus 10mV (or any other voltage increment that is selected). Figure 5 illustrates the  $V_{MIN}$  characterization flow.

Figure 5. V<sub>MIN</sub> characterization flow.

## 2.4 Voltage Margin Elimination Techniques

A voltage margin elimination approach is the critical path monitoring (CPM) [44]. CPMs are on-chip sensors that can measure at real-time the CPU's available timing margin. CPM can be combined with an actuator that can adjust the voltage or operating frequency. For instance, when the available timing margin is high, then the actuator can reduce the operating voltage to reduce the power or increase the CPU frequency to improve the energy efficiency. If the timing margin is low, then the CPU frequency should be decreased, or the voltage should be increased to ensure stability. Even in the presence of this technique, a fixed voltage margin for the worst-case voltage droops must be maintained to ensure stability in production setups [44]. Therefore, in practice this timing guard-band scheme adjusts the voltage (or frequency) depending on workload's voltage noise magnitude to maintain a fixed margin. This is a more energy-efficient approach compared to the conventional approach of maintaining fixed operating voltage, because with fixed operating voltage a lot of power is wasted for common workloads that do not cause high voltagenoise.

A more aggressive approach for voltage margin elimination is Razor [21]. Compared to CPM, Razor can provide higher energy savings, but it also incurs higher area and penalty overhead. Razor is based on running the chip at aggressive voltage/frequency conditions and relying on error-detection and roll-back mechanism to recover the pipeline from errors. Razor replicates critical path flip-flops. One flip-flop operates at aggressive margin conditions and provides the speculative value. The other flip-flop operates at safe conditions and provides the golden reference. If the flip-flop values do not match, then a recovery mechanism for bringing the pipeline to the correct state is started.

### 2.5 LdI/dt Noise Mitigation Techniques

The most common approach for mitigating dI/dt voltage-noise is to add on-chip capacitance [55]. Capacitance affect voltage-noise in two ways. First, higher capacitance helps in mitigating the voltage droop magnitude. Adding decoupling capacitors is a known design-time technique to reduce voltage droop magnitude [63]. This approach has its limitations though, as cost, area overheads and leakage limit the amount of capacitance that can be added. In general, well connected PDNs that connect many hardware components, and, thus, incorporate higher capacitance are considered beneficial for voltage noise reduction [37]. The second effect that capacitance has on voltage-noise is that higher capacitance has inverse relationship with resonance-frequency [55]. Therefore, the resonance-frequency decreases with more capacitance. In terms of voltage-droop magnitude, shifting the resonance-frequency can be either beneficial or detrimental depending on which frequencies a workload exercise.

The vast majority of voltage droops is caused by periodic activity of loops [33][85]. If these loops happen to match the PDN resonance-frequency, then the voltage noise is amplified even further. Therefore, authors in [58][59][60] examined ways to modulate loop frequency to avoid resonant voltage-noise. The proposed approaches require the capability to monitor current at high bandwidth. Monitoring current is more advantageous over monitoring voltage in this case, because resonant current behavior precedes voltage noise. The authors exploit a phenomenon called "maximum repetition tolerance" which is the maximum resonant current repetitions that can happen before a large voltage emergency is triggered. The maximum repetition tolerance helps preventing unnecessary reactions to voltage droops that are not dangerous and at the same it helps ensuring that a mitigation mechanism will be engaged before it is too late. For mitigating voltage droop when detected, stalling the pipeline by stalling instruction issue or instruction fetch has been proposed by the authors. These mitigation approaches incur a performance penalty each time an emergency is detected. Other authors [39] have proposed to clock-gate or turn-on functional units on purpose to reduce or increase current consumption. Turn-on can be used to compensate voltage droop and clock-gate to smooth-out voltage overshoot.

The adoption of multi-core CPUs compared to single core CPUs raises the dynamic power variability and hence increases the susceptibility to voltage transients. But at the same time, it gives opportunity for voltage noise mitigation with destructive scheduling [66]. Essentially, some workloads when co-scheduled on different cores of a multi-core CPU have a damping effect on voltage noise. Other workload combinations amplify voltage noise. The key is to find which workload combinations decrease the voltage noise and utilize this information in scheduling decisions. Workloads can have destructive voltage-noise interference because their current consumption does not align. Destructive interference can be also applied within multi-threaded application by misaligning the threads synchronization barriers [49]. Other work performed in a modern multi-core IBM server processor that supports droop mitigation mechanisms has shown that the server efficiency is limited by the IR drop [75]. Therefore, they suggest in multi-socket servers, to evenly balance the workload across the CPU sockets to minimize IR drop for better energy efficiency.

Using ECC feedback as a proxy of voltage noise and emergency conditions has been proposed in [9]. The idea is to lower the voltage until ECC errors start to occur. This approach applies only to chips that have error protected ECC pipelines. Other work shows that predicting safe V<sub>MIN</sub> through workload performance counters signature is possible [56]. Another prediction scheme [63] proposes voltage noise prediction based on sequences of micro-architectural events and instruction that are likely to cause voltage noise (e.g. branch instructions, pipeline flushes etc.). A micro-architectural structure inspired by branch predictors but for prediction of voltage noise emergency is proposed. This mechanism also relies on a voltage sensor for training the predictor as well as a roll-back mechanism in case of wrong emergency prediction that causes CPU malfunction. A voltage emergency misprediction in such configuration induces performance penalty.

Voltage droop mitigation circuits have been proposed and implemented on some processors [14][26][31][43][46][62][74]. A common mitigation circuit setup includes: a) an on-die voltage monitor sensor, b) an actuator that mitigates the voltage noise either by pipeline throttling (stall instruction issue or fetch) or reducing the CPU frequency (e.g. adaptive-clocking [14]) and c) a voltage threshold indicating when the actuator should be enabled (also in case of frequency modulation the amount of modulation is expressed). Setting the right threshold can be tricky. A conservative (pessimistic) threshold might lead to performance penalty whereas an optimistic threshold might translate to instability.

## 2.6 LdI/dt noise on GPUs

Besides CPU voltage noise, voltage on GPUs has been studied as well. In fact, GPUs may suffer more from voltage noise due to their higher current consumption. Contrast to CPU research, most GPU voltage noise research has been performed with the help of GPU voltage noise simulators e.g. the GPUVolt simulator [86]. This might be an indication that interfaces for direct voltage noise measurements on GPUs are seldomly found. Generating high inductive noise on GPUs should be easier compared to CPUs. The GPU cores are much simpler compared to complex general-purpose CPU out-of-order superscalar pipelines. Moreover, GPUs have much more support for synchronizing core execution which assists the generation of large dI/dt swings. Therefore, researchers have shown that dI/dt viruses can be achieved by relatively simple manual written code that activates and deactivates functional units with periodicity that matches the resonance-frequency or using instructions that are known to cause low and high-power consumption [70][87].

Similar techniques to CPU have been proposed for voltage noise mitigation on GPUs. GPUs due to high core counts are susceptible to static variations. Researchers have proposed the use of CPM combined with clock gating to throttle down cores that do not have enough timing margin [87]. Other work reaches to the interesting conclusion that on GPUs normal workloads have higher 2nd order droop compared to 1st order droop [45]. This is the case because the 1st order droop is more sensitive to miss-alignment of cores. In fact, alignment with so many cores (>100) at ~100MHz is hard to achieve. Whereas events as second order droop around 1MHz are aligned easier. They have identified that the main events that cause 1st order droops for GPUs are dispatch stalls and register file current variations. Events that cause 2nd order droops are instruction and data cache miss stalls. For droop mitigation they suggest blocking dispatch unit and delaying system wide activity. Last, related work has examined the GPU behaviour at low voltages. The researchers have shown that performance counters can be utilized for workload V<sub>MIN</sub> prediction [88].

# 2.7 EM emanations exploitation