# DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

# FABRICATION AND CHARACTERIZATION OF MEMRISTIVE DEVICES FOR BIOINSPIRED APPLICATIONS

#### **EVRIPIDES KYRIAKIDES**

A Dissertation Submitted to the University of Cyprus in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

### **VALIDATION PAGE**

Doctoral Candidate: Evripides Kyriakides

Doctoral Thesis Title: Fabrication and Characterization of Memristive Devices for Bioinspired Applications

The present Doctorate Dissertation was submitted in partial fulfillment of the requirements for the Degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering, and was approved on May  $18^{th}$ , 2016 by the members of the Examination Committee.

| Examination Committee: |                                  |

|------------------------|----------------------------------|

|                        |                                  |

| C                      |                                  |

| Committee Chair        |                                  |

|                        | Constantinos Pitris, Ph.D., M.D. |

|                        |                                  |

|                        |                                  |

| Research Supervisor    |                                  |

|                        | Georgios Ellinas, Ph.D.          |

|                        |                                  |

|                        |                                  |

| Committee Member       |                                  |

|                        | Stavros Iezekiel, Ph.D.          |

|                        |                                  |

|                        |                                  |

| Committee Member       |                                  |

|                        | Matthew Zervos, Ph.D.            |

|                        |                                  |

|                        |                                  |

| Committee Member       |                                  |

|                        | Shahar Kvatinsky, Ph.D.          |

| The present Doctoral Dissertation was submitted in partial fulfillment of the    |

|----------------------------------------------------------------------------------|

| requirements for the degree of Doctor of Philosophy of the University of Cyprus. |

| It is a product of original work of my own, unless otherwise mentioned through   |

| references, notes, or any other statements.                                      |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

| <br> | <br> |

|------|------|

| <br> | <br> |

# Περίληψη

Οι συσκευές μνημοαντίστασης προτάθηκαν αξιωματικά το 1971 και απαντήθηκαν για πρώτη φορά το 2008, παρόλο που έχουν υπάρξει για πολύ μεγαλύτερο χρονικό διάστημα. Κυκλώματα προσομοίωσης συσκευών μνημοαντίστασης είχαν χτιστεί και στο παρελθόν, αλλά υπέφεραν είτε από μεγάλες τοπολογίες ή από υπερβολικές απαιτήσεις σε χώρο και ισχύ. Οι χαρακτηριστικές ιδιότητες των μονολιθικών συσκευών μνημοαντίστασης, όμως, υπόσχονται σημαντικές βελτιώσεις σε διάφορους τομείς της μικροηλεκτρονικής. Στο πλαίσιο της αρχιτεκτονικής υπολογιστών von Neumann, προσφέρουν σημαντικά πλεονεκτήματα που θα μπορούσαν να αποδειχθούν ζωτικής σημασίας για τη συνέχιση των σημερινών τάσεων κλιμάκωσης. Με την προσθήκη τους στην εργαλειοθήκη των ηλεκτρονικών συσκευών, νέες εφαρμογές - ή βελτιώσεις υφισταμένων - προτείνονται. Αλλά κυρίως, μπορούν να χρησιμοποιηθούν για την υλοποίηση ηλεκτρονικών συνάψεων, που παρουσιάζουν πλαστικότητα και μάθηση.

Η μελέτη αυτή έχει ως στόχο την μοντελοποίηση, την κατασκευή και τον χαρακτηρισμό των εν λόγω συσκευών μνημοαντίστασης και την ενσωμάτωσή τους σε πρωτότυπες βιομιμητικές εφαρμογές. Για το σκοπό αυτό, περιγράφεται ο σχεδιασμός και η κατασκευή νέων συσκευών μνημοαντίστασης: μία συσκευή μνημοαντίστασης έξυπνου κράματος νικελίου-τιτανίου (NiTi) και μία μνημοαντίσταση χαλκού/πεντοξειδίου τανταλίου (Cu/Ta<sub>2</sub>O<sub>5</sub>). Είναι εντός του πεδίου εφαρμογής της παρούσας εργασίας η αξιολόγηση των χαρακτηριστικών αυτών των συσκευών και η εξαγωγή μοντέλων συμπεριφοράς για να καταστεί δυνατή η ένταξή τους στο σχεδιασμό κυκλωμάτων. Ως εκ τούτου, ο εκτεταμένος γαρακτηρισμός και μοντελοποίηση που εκτελέστηκαν σε αυτές τις δομές παρουσιάζονται ενδελεχώς. Αυτό περιλαμβάνει θερμική προσομοίωση, εκτός από θερμικές και ηλεκτρικό γαρακτηρισμό, για τη συσκευή ΝίΤι. Ο ηλεκτρικός γαρακτηρισμός για τη συσκευή Cu/Ta<sub>2</sub>O<sub>5</sub> περιλαμβάνει καθεστώτα συνεχούς ρεύματος, εναλλασσόμενου ρεύματος, και παλμού. Μοντέλα προσομοίωσης κατασκευάστηκαν για κάθε συσκευή και υλοποιήθηκαν σε Hardware Description Language (HDL). Τα μοντέλα ταιριάζουν με επιτυχία με τις μετρήσεις μέσω προσομοιώσεων, επιτρέποντας την ένταξή τους σαν ενότητες σε κυκλώματα. Τέλος, η μελέτη αυτή εμπεριέχει την κατασκευή εφαρμογών κυκλωμάτων που εκμεταλλεύονται τις ιδιότητες μνημοαντίστασης. Αρχικά, παρουσιάζεται ένας ταλαντωτής χαμηλής συχνότητας που βασίζεται σε συσκευή μνημοαντίστασης και που απευθύνεται στον παράγοντα του χώρου. Στη συνέχεια, ένα νευρομορφικό σύστημα που ενσωματώνει τις κατασκευασμένες μνημοαντιστάσεις  $Cu/Ta_2O_5$  φτιάχνεται για να διερευνήσει τη δυνατότητα της πλαστικότητα και της μάθησης και χρησιμοποιώντας μνημοαντιστάσεις. Τα κυκλώματα που είναι σχεδιασμένα για αυτό το σκοπό αναλύονται και το δίκτυο αξιολογείται.

Κατά τη διαδικασία της παρούσας διατριβής, συσκευές μνημοαντίστασης, τα βασικά δομικά στοιχεία της βιοεμπνευσμένης αρχιτεκτονικής, κατασκευάζονται και μελετούνται. Οι μοναδικές τους ιδιότητες στοιχειοθετούνται και μοντελοποιούνται. Ακολούθως, ενσωματώνονται στο σχεδιασμό και την κατασκευή νέων βιοεμπνευσμένων εφαρμογών.

#### Επισκόπηση κεφαλαίων

Το Κεφάλαιο 1 καθορίζει το κίνητρο για την εργασία αυτή. Οι όροι «βιοεμπνευσμένο κύκλωμα» και «συσκευή μνημοαντίστασης» εισάγονται και διηγείται συνοπτικά η κατάσταση των εν λόγω τεχνολογιών. Ακολούθως, αναθεωρείται η τρέχουσα τεχνολογία υπολογιστών, ενώ τα πλεονεκτήματα της βιοεμπνευσμένης αρχιτεκτονικής αναλύονται και οι λόγοι για την επιλογή μνημοαντιστάσεων ως βασικό δομικό στοιχείο εξηγείται. Τέλος, ορίζονται οι στόχοι της έρευνας.

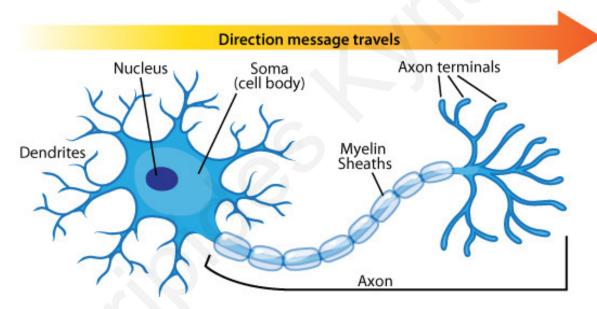

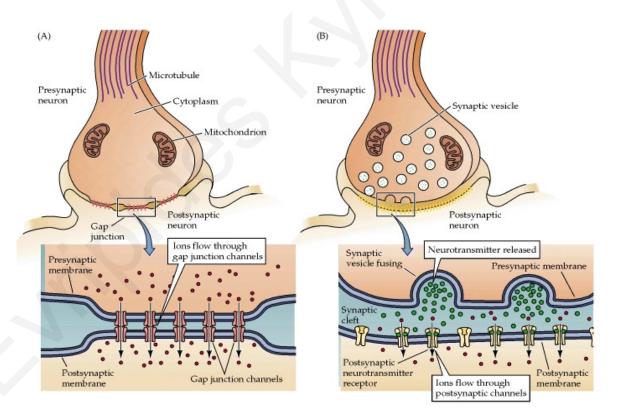

Το Κεφάλαιο 2 ξεκινά με μια ιστορική προοπτική για το βιοεμπνευσμένο σχεδιασμό, εντοπίζοντας τα βιολογικά θεμέλια της νευρομορφικής αρχιτεκτονικής. Στη συνέχεια, παρέχει μια λεπτομερή περιγραφή των συσκευών μνημοαντίστασης και αναλύει τις μοναδικές τους ιδιότητες. Προχωρά με την κατάσταση της τεχνολογίας στην συσκευές μνημοαντίστασης, κατηγοριοποιώντας και απαριθμώντας τα είδη των συσκευών που απαντώνται στη βιβλιογραφία, καθώς και αναλύοντας το μηχανισμό που προκαλεί τη συμπεριφορά μνημοαντίστασης. Κατά τη διαδικασία αυτή, οι δομές των διατάξεων αποκαλύπτονται σε συνδυασμό με τις αντίστοιχες διαδικασίες κατασκευής τους.

Το Κεφάλαιο 3 παρουσιάζει την πρώτη επιλογή δομής για αυτή την έρευνα. Η διάταξη, στη βάση NiTi, περιγράφεται λεπτομερώς. Μετά από εξέταση των μεθόδων παραγωγής που χρησιμοποιούνται, καλύπτονται οι μεθοδολογίες χαρακτηρισμού και προσομοίωσης. Ακολούθως, αναφέρονται οι μέθοδοι που χρησιμοποιούνται για την μοντελοποίηση των

κατασκευασμένων συσκευών NiTi. Τα προκύπτοντα μοντέλα αντιπροσωπεύονται σε Verilog-A και συγκρίνονται με τα αντίστοιχα αποτελέσματα χαρακτηρισμού.

Το Κεφάλαιο 4 παρουσιάζει τη δεύτερη επιλογή δομής για αυτή την έρευνα. Η συσκευή, που βασίζεται σε Cu/Ta<sub>2</sub>O<sub>5</sub>, περιγράφεται λεπτομερώς. Μετά από μία επανεξέταση των τεχνικών κατασκευής ημιαγωγών, παρουσιάζεται η κατασκευή της δομής σε cleanroom. Οι διαδικασίες ηλεκτρικού χαρακτηρισμού και τα συναφή αποτελέσματα για την κατασκευασμένη συσκευή καλύπτονται στη συνέχεια. Ακολούθως, αναφέρονται οι μέθοδοι που χρησιμοποιούνται για την μοντελοποίηση των κατασκευασμένων συσκευών Cu/Ta<sub>2</sub>O<sub>5</sub>. Τα προκύπτοντα μοντέλα αντιπροσωπεύονται σε Verilog-A και συγκρίνονται με τα αντίστοιχα αποτελέσματα χαρακτηρισμού.

Το Κεφάλαιο 5 παρουσιάζει τα κυκλώματα στη βάση συσκευών μνημοαντίστασης που σχεδιάζονται και κατασκευάζονται στα πλαίσια της παρούσας διατριβής. Καταρχάς, αναλύει ένα σχέδιο ταλαντωτή χαλάρωσης και παραθέτει τα συγκριτικά του πλεονεκτήματα. Ακολούθως, περιγράφει λεπτομερώς το σχεδιασμό και τη λειτουργικότητα ενός δικτύου εκμάθησης. Το σχέδιο υλοποιείται σε Cadence Virtuoso και οι ενότητές του παρουσιάζονται χωριστά. Μετέπειτα, η συμπεριφορά του κατασκευασμένου κυκλώματος επιβεβαιώνεται και συγκρίνεται με τη σχετική βιβλιογραφία.

Το Κεφάλαιο 6 συνοψίζει το έργο που επιτελέστηκε σε αυτή τη διατριβή. Οι συσκευές μνημοαντίστασης και οι εφαρμογές εξετάζονται, τονίζοντας τα βασικά τους αποτελέσματα. Στη συνέχεια, παρατίθενται οι συνεισφορές αυτής της μελέτης και προτείνονται μελλοντικές κατευθύνσεις έρευνας στους τομείς των συσκευών μνημοαντίστασης και των βιοεμπνευσμένων εφαρμογών.

#### **Abstract**

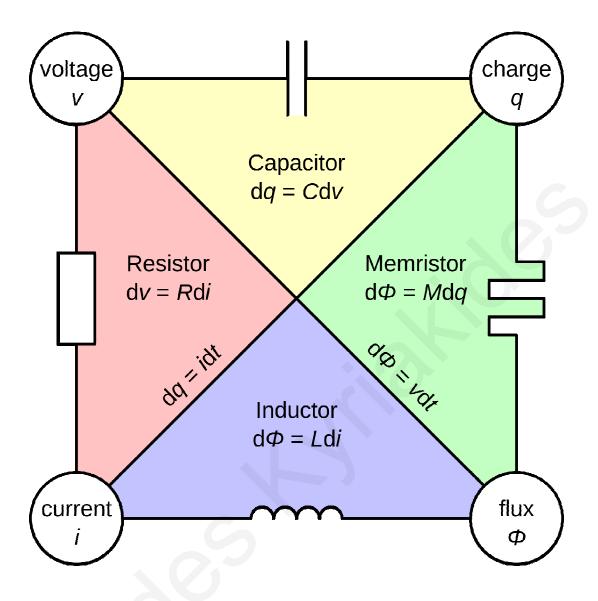

Memristive devices were postulated in 1971 and identified in 2008, even though they have existed for much longer. Memristive-device-emulating circuits had been built in the past, but suffered from either large topologies or excessive area and power requirements. The distinctive properties of monolithic memristive devices, however, hold promise for significant improvements in various areas of microelectronics. In the framework of von Neumann computer architecture, they offer significant advantages that could prove crucial in continuing current scaling trends. With their addition to the toolbox of electronic devices, novel applications - or improvements to existing ones - are being proposed. But most significantly, they can be used for implementing electronic synapses, exhibiting plasticity and learning.

This thesis is aimed at modeling, fabricating and characterizing such memristive devices and incorporating them in prototype bioinspired applications. To that end, the design and fabrication of novel memristive devices is reported: a nickel titanium (NiTi) smart alloy memristive device and copper/tantalum pentoxide (Cu/Ta<sub>2</sub>O<sub>5</sub>) memristor. It is within the scope of this work to evaluate the characteristics of these devices and extract behavioral models to enable their integration into circuit design. Therefore, the extensive characterization and modeling performed on these structures is comprehensively presented. This includes thermal simulation, in addition to thermal and electrical characterization, for the NiTi device. Electrical characterization for the Cu/Ta<sub>2</sub>O<sub>5</sub> device includes DC, AC, and pulse regimes. Behavioral models were constructed for each device and implemented in Hardware Description Language (HDL). The models were successfully matched to measurements through simulations, enabling their inclusion as modules in circuits. Finally, this study encompasses constructing circuit applications exploiting memristive properties. First, a low-frequency memristor-based oscillator addressing space considerations is presented. Next, a neuromorphic system incorporating the fabricated Cu/Ta<sub>2</sub>O<sub>5</sub> memristors is built to investigate the possibility of plasticity and learning using memristors. The circuits designed for this purpose are thus analyzed and the network evaluated.

In the process of this thesis, memristive devices, the basic building blocks of bioinspired architecture, are built and studied. Their unique properties are established and modeled. Subsequently, they are incorporated in the fabrication of novel bioinspired applications.

#### Overview of chapters

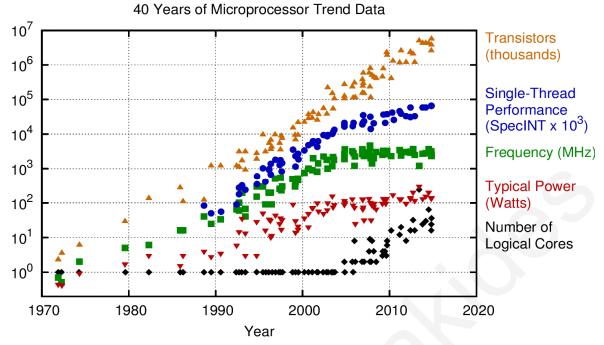

Chapter 1 establishes the motivation for this thesis. The terms "bioinspired circuit" and "memristive device" are introduced and a concise account of their state-of-the-art is narrated. Subsequently, current computing technology is reviewed, whereas the merits of bioinspired architecture are analyzed and the reasons for choosing memristive devices as the basic building block are explained. Finally, the research objectives are laid out.

Chapter 2 starts with a historical perspective on bioinspired design, tracing the biological foundations of neuromorphic architecture. It then provides a detailed description of memristive devices and analyzes their unique properties. It proceeds with the state-of-the-art in memristive devices, grouping and enumerating the types of devices encountered in the literature, as well as analyzing the specific mechanism that causes memristive behavior. In the process, memristive structures are revealed in tandem with their respective fabrication procedures.

Chapter 3 presents the first choice of structure for this research. The device, based on NiTi, is described in detail. Following an examination of the manufacturing methods utilized, the characterization and simulation methodologies are covered. Subsequently, the methods used for modeling the fabricated NiTi devices are reported. The resulting models are represented in Verilog-A and compared to the respective characterization results.

Chapter 4 presents the second choice of structure for this research. The device, based on Cu/Ta<sub>2</sub>O<sub>5</sub>, is described in detail. Following a review of semiconductor fabrication techniques, the cleanroom fabrication of the structure is presented. The electrical characterization procedures and associated results for the fabricated device are then covered. Subsequently, the methods used for modeling the fabricated Cu/Ta<sub>2</sub>O<sub>5</sub> devices are reported. The resulting models are represented in Verilog-A and compared to the respective characterization results.

Chapter 5 introduces the memristive-device-based circuits designed and fabricated as part of this thesis. At first, it analyzes a relaxation oscillator design and lists its comparative advantages. Then, it details the design and functionality of a learning network. The design is implemented in Cadence Virtuoso and the modules are separately presented. The behavior of the fabricated circuit is then established and compared to the pertinent literature.

Chapter 6 summarizes the work done in this thesis. The memristive devices and applications are reviewed, with their key results highlighted. It goes on to list the contributions of this study and propose future directions of research in the fields of memristive devices and bioinspired applications.

# **Acknowledgements**

I would like to thank everyone who has contributed towards the completion of this work, beginning with my research supervisor, Prof. Georgios Ellinas. To my fellow researchers at the University of Cyprus, Guillaume Garreau, Nicoletta Nicolaou, Horacio Rostro-Gonzalez, Adrian Romiński, Panayiota Demosthenous, Christopher Beck, and especially Charalambos Andreou, I appreciate the help and support. From the École Polytechnique Fédérale de Lausanne I am grateful for the help of Sandro Carrara, Francesca Puppo, and Davide Sacchetto, as well as, Philippe Flückiger, Cyrille Hibert, and Boris Lunardi, from the Center of MicroNanoTechnology. I would also like to thank Danilo De Marchi and Katarzyna Bejtka from the Istituto Italiano di Tecnologia. Finally, I would like to acknowledge the Cyprus Research Promotion Foundation for funding this work.

## **Publications**

#### **Published journal publications**

- 1. E. Kyriakides and J. Georgiou, "A compact, low-frequency, memristor-based oscillator," *International Journal of Circuit Theory and Applications*, vol. 43, no. 11, pp. 1801-1806, 2015.

- 2. E. Kyriakides, S. Carrara, G. De Micheli, and J. Georgiou, "Low-cost, CMOS compatible, Ta2O5-based hemi-memristor for neuromorphic circuits," *Electronics Letters*, vol. 48, no. 23, pp. 1451-1452, 2012.

- 3. J. Georgiou, E. Kyriakides, and C. Hadjistassou, "NiTi smart alloys for memristors with multi-time-scale volatility," *Electronics Letters*, vol. 48, no. 14, pp. 877-879, 2012.

#### **Published conference proceedings**

- 1. J. Georgiou and E. Kyriakides, "Memristors for energy-efficient, bioinspired processing," *IEEE 27th Convention of Electrical & Electronics Engineers in Israel (IEEEI)*, pp. 1-5, November 2012.

- 2. E. Kyriakides, C. Hadjistassou, and J. Georgiou, "A new memristor based on NiTi smart alloys," *IEEE International Symposium on Circuits and Systems (ISCAS)*, pp. 1403-1406, May 2012.

# **Contents**

| 1 | Intr | oductio | on                                        | 1  |

|---|------|---------|-------------------------------------------|----|

|   | 1.1  | Why b   | bioinspired systems?                      | 1  |

|   | 1.2  | Curre   | ent computing technology                  | 1  |

|   | 1.3  | Bioins  | spired design                             | 5  |

|   | 1.4  | Memr    | ristive Devices                           | 6  |

|   | 1.5  | Resea   | arch objectives                           | 8  |

|   | 1.6  | Synop   | psis                                      | 9  |

| 2 | Bac  | kgroun  | nd                                        | 11 |

|   | 2.1  | Introd  | duction                                   | 11 |

|   | 2.2  | Bioins  | spired design                             | 11 |

|   |      | 2.2.1   | Historical review                         | 12 |

|   |      | 2.2.2   | Bioinspired design framework              | 13 |

|   |      | 2.2.3   | Discussion                                | 22 |

|   | 2.3  | Memr    | ristive devices                           | 24 |

|   |      | 2.3.1   | Historical review                         | 25 |

|   |      | 2.3.2   | Memristor theory                          | 26 |

|   |      | 2.3.3   | State of the art in memristive structures | 37 |

|   |      |         | 2.3.3.1 Metal-insulator-metal             | 38 |

|   |      |         | 2.3.3.2 Single-element                    | 47 |

|   |      |         | 2.3.3.3 Organic                           | 49 |

|   |      |         | 2.3.3.4 Silicon-based                     | 55 |

|   |      |         | 2.3.3.5 Insulator-metal transition        | 62 |

|   |      |         | 2.3.3.6 Transition metal oxide            | 65 |

|   |      |         | 2.3.3.7 Valence change memory             | 66 |

|   |      |         | 2.3.3.8 Cation-migration-based            | 67 |

|   |      | 2.3.4   | Discussion                                | 70 |

|   | 2.4  | Concl   | lusion                                    | 75 |

| 3 | NiT  | i Devic | ce                                        | 77 |

|   | 3.1  | Introd  | duction                                   | 77 |

|   | 3.2  | Choice of NiTi structure                                                   |

|---|------|----------------------------------------------------------------------------|

|   | 3.3  | Fabrication of NiTi devices                                                |

|   |      | 3.3.1 Enclosure fabrication                                                |

|   |      | 3.3.2 Discussion                                                           |

|   | 3.4  | Characterization and modeling of NiTi devices                              |

|   |      | 3.4.1 Methods                                                              |

|   |      | 3.4.2 Thermal simulations                                                  |

|   |      | 3.4.3 Resistance measurements                                              |

|   |      | 3.4.4 Behavioral modeling                                                  |

|   |      | 3.4.5 Discussion                                                           |

|   | 3.5  | Conclusion                                                                 |

|   |      |                                                                            |

| 4 | Cu/  | Ta <sub>2</sub> O <sub>5</sub> Device                                      |

|   | 4.1  | Introduction                                                               |

|   | 4.2  | Choice of Cu/Ta <sub>2</sub> O <sub>5</sub> structure                      |

|   | 4.3  | Fabrication of Cu/Ta <sub>2</sub> O <sub>5</sub> devices                   |

|   |      | 4.3.1 Fabrication methods                                                  |

|   |      | 4.3.2 Process outline                                                      |

|   |      | 4.3.3 Fabrication results                                                  |

|   |      | 4.3.4 Discussion                                                           |

|   | 4.4  | Characterization and modeling of Cu/Ta <sub>2</sub> O <sub>5</sub> devices |

|   |      | 4.4.1 Methods                                                              |

|   |      | 4.4.2 Pre-forming region                                                   |

|   |      | 4.4.3 Forming process                                                      |

|   |      | 4.4.4 Post-forming region                                                  |

|   |      | 4.4.5 Threshold voltage designation                                        |

|   |      | 4.4.6 Pulse measurements                                                   |

|   |      | 4.4.7 AC measurements                                                      |

|   |      | 4.4.8 Behavioral modeling                                                  |

|   |      | 4.4.9 Discussion                                                           |

|   | 4.5  | Conclusion                                                                 |

|   |      |                                                                            |

| 5 | Bioi | inspired System Demonstration                                              |

|   | 5.1  | Introduction                                                               |

|   | 5.2  | Memristor oscillator                                                       |

|   |      | 5.2.1 Memristor model                                                      |

|          |        | 5.2.2    | Circuit design            | 172 |

|----------|--------|----------|---------------------------|-----|

|          |        | 5.2.3    | Discussion                | 175 |

|          | 5.3    | Learni   | ing network               | 177 |

|          |        | 5.3.1    | Design                    | 178 |

|          |        | 5.3.2    | LIF neuron                | 180 |

|          |        | 5.3.3    | Modules                   | 182 |

|          |        | 5.3.4    | Characterization          | 186 |

|          |        | 5.3.5    | Results                   | 201 |

|          |        | 5.3.6    | Discussion                | 208 |

|          | 5.4    | Concl    | usion                     | 209 |

|          |        |          |                           |     |

| 6        | Con    | clusion  |                           | 211 |

|          | 6.1    | Summ     | nary                      | 211 |

|          | 6.2    | Contri   | butions                   | 213 |

|          | 6.3    | Future   | e work                    | 215 |

|          |        |          |                           |     |

| Re       | feren  | ces      |                           | 217 |

|          |        |          |                           |     |

| A        | Clean  | room F   | Fabrication Equipment     | 227 |

|          |        |          |                           |     |

| B        | Electr | rical Ch | naracterization Equipment | 235 |

|          |        |          |                           |     |

| <b>C</b> | Verilo | og-A Sc  | ripts                     | 245 |

|          |        |          |                           |     |

| D        | Chin   | Fahrica  | ation and Testing         | 251 |

# **List of Acronyms and Abbreviations**

3D IC Three-Dimensional Integrated Circuit

a-Si Amorphous Silicon AC Alternating Current

ADC Analogue-to-Digital Converter

AHDL Analog Hardware Descriptive Language

ALD Atomic Layer Deposition

ASIC Application Specific Integrated Circuit

ASIP Application-Specific Instruction-Set Processor

BRAIN Brain Research through Advancing Innovative Neurotechnologies

CMOS Complementary Metal-Oxide Semiconductor

CL Current Limiter

CMP Chemical Mechanical Polishing

CNT Carbon Nanotube

CPU Central Processing Unit

DC Direct Current

DMM Digital Multimeter

DRAM Dynamic Random Access Memory

DRIE Deep Reactive Ion Etching

DUT Device Under Test

E-beam Electron beam

EBL Electron Beam Lithography

FESEM Field Emission Scanning Electron Microscope

FET Field-Effect Transistor

FIB Focused Ion Beam

FLOPS Floating-Point Operations per Second

FPGA Field-Programmable Gate Array

G-O Graphene Oxide

GPU Graphics Processing Unit

HDL Hardware Description Language

HRS High Resistance State

IC Integrated Circuit

ILP Instruction Level Parallelism

**IMT Insulator-Metal Transition**

**IPA:MIBK** Isopropanol:methyl-isobutyl-ketone

LB Langmuir-Blodgett

LF Low Frequency

LIF Leaky Integrate-and-Fire

Lift-Off Resist LOR

**LPCVD** Low-Pressure Chemical Vapor Deposition

Low Resistance State LRS LTD Long-Term Depression LTO Low Temperature Oxide Long-Term Potentiation LTP

Metal-Insulator-Metal MMA/MAA Methyl-methacrylate/methacrylic-acid

**MOSFET** Metal-Oxide-Semiconductor Field-Effect Transistor

**MRAM** Magnetoresistive Random-Access Memory

NA **Acceptor Concentration**

Nickel Titanium NiTi

MIM

**NMP** N-Methyl-2-Pyrrolidone

p-type Silicon p-Si Polyaniline **PANI**

PCB Printed Circuit Board Phase-Change Memory **PCM**

**PCMO** Pr1-xCaxMnO3

Post Exposure Bake **PEB PEO** Polyethylene Oxide

**PLD** Pulsed Laser Deposition

**PMMA** Poly(methyl-methacrylate)

poly-crystalline Silicon poly-Si

PR **Photoresist**

PTFE Polytetrafluoroethylene

RF Radio Frequency

**RIE** Reactive Ion Etchant

**RRAM** Resistive Random-Access Memory

**SEM** Scanning Electron Microscopy

**SMA** Shape Memory Alloy SMU Source Measurement Unit

SOG Spin-on Glass

SOI Silicon on Insulator

STDP Spike-Timing-Dependent Plasticity

TRIS Tris(hydroxymethyl)aminomethane

TSV Through-Silicon Via

UV Ultraviolet

XRD X-Ray Diffraction

# **List of Figures**

| 1.1  | Evolution of microprocessor data over 40 years. Adapted from [5]                                                                                                                                                                                                    | 3  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

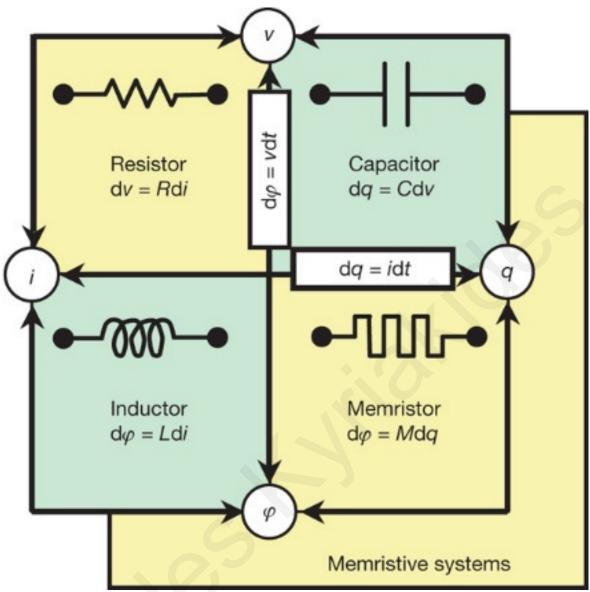

| 1.2  | The four fundamental circuit elements. Adapted from [19].                                                                                                                                                                                                           | 7  |

| 2.1  | The anatomy of the biological neuron showing the direction of signal transmission. Adapted from [39].                                                                                                                                                               | 14 |

| 2.2  | Comparison of electrical and chemical synapses. Adapted from [41]                                                                                                                                                                                                   | 15 |

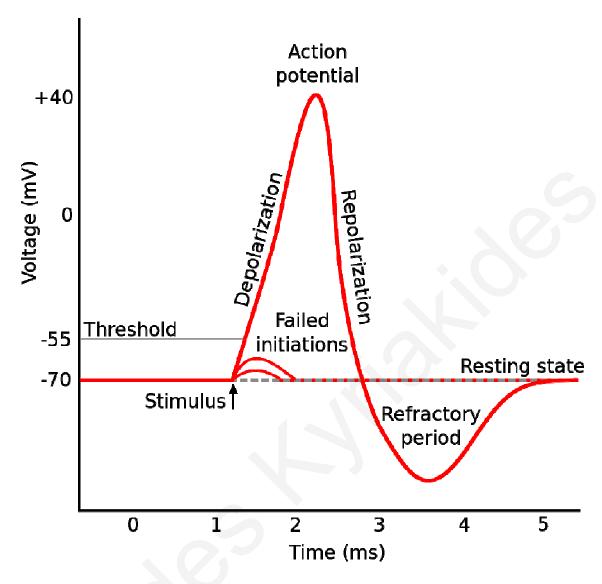

| 2.3  | Action potential generation. Adapted from [43].                                                                                                                                                                                                                     | 17 |

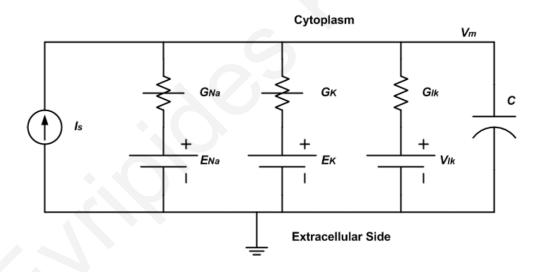

| 2.4  | General Hodgkin-Huxley model with external stimulus. Adapted from [44].                                                                                                                                                                                             | 18 |

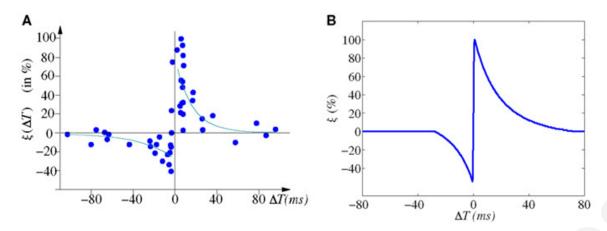

| 2.5  | Illustration of STDP. Change in plasticity is plotted with respect to time difference of spikes of post-synaptic and pre-synaptic neuron. (A) Experimentally measured results from the hippocampal neuron. (B) Idealized STDP function. Adapted from [49].          | 22 |

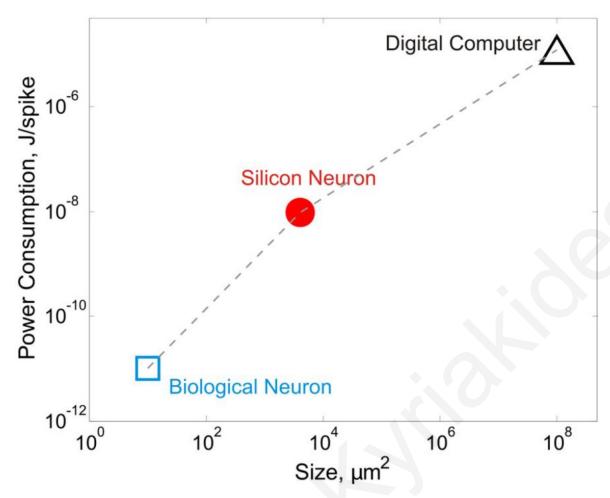

| 2.6  | Comparison between the power and space efficiencies of digital computers, silicon neurons, and biological neurons. Adapted from [53].                                                                                                                               | 24 |

| 2.7  | The four fundamental circuit elements. Adapted from [18].                                                                                                                                                                                                           | 27 |

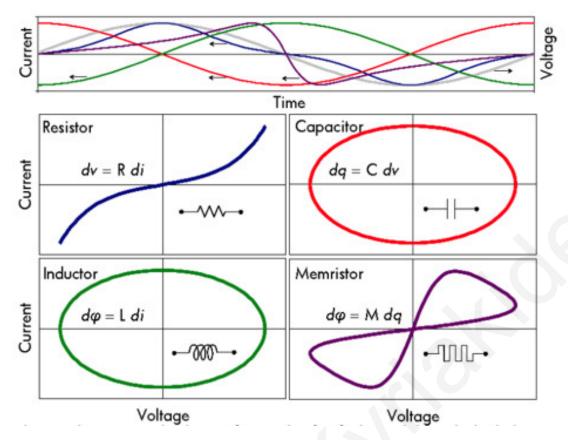

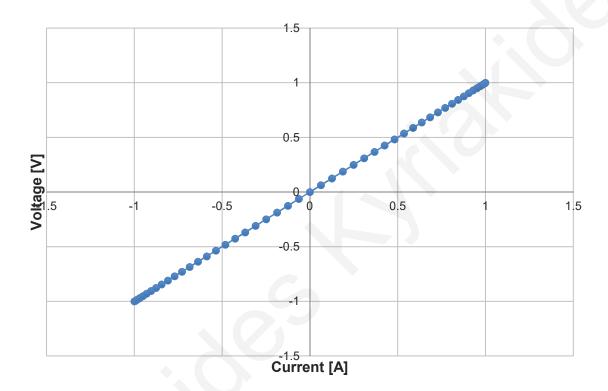

| 2.8  | Current-voltage characteristics for the resistor, capacitor, inductor and memristor. Adapted from [62].                                                                                                                                                             | 28 |

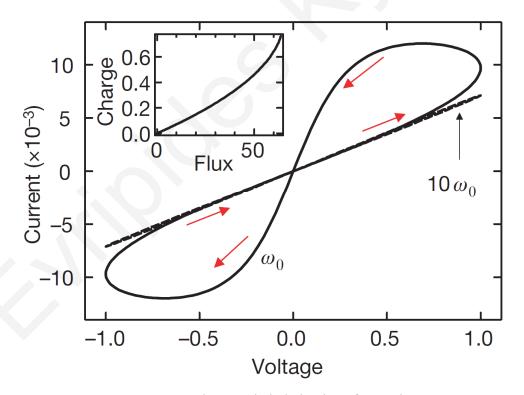

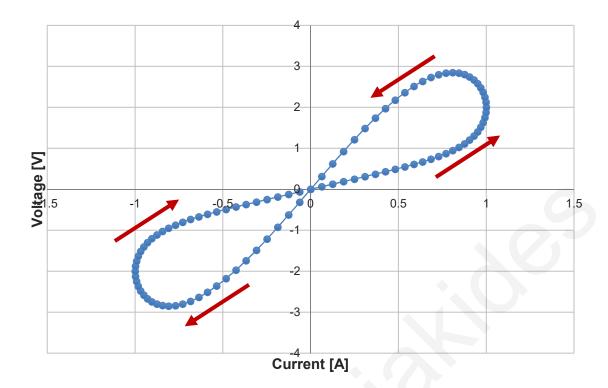

| 2.9  | Characteristic behavior of memristor. Adapted from [18]                                                                                                                                                                                                             | 30 |

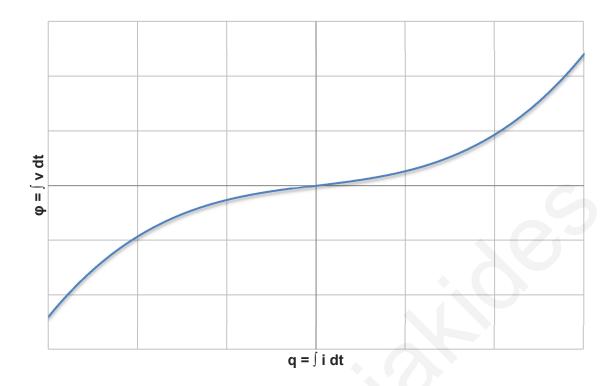

| 2.10 | Graphical representation of $\varphi(q) = q + q^3/3$                                                                                                                                                                                                                | 33 |

| 2.11 | Pinched hysteresis loop of $(v(t), i(t))$ with $A = 1$ and $\omega = 2\pi$                                                                                                                                                                                          | 35 |

| 2.12 | Degenerate case of hysteresis loop of $(v(t), i(t))$ with $A = 1$ and $\omega = 2\pi$                                                                                                                                                                               | 36 |

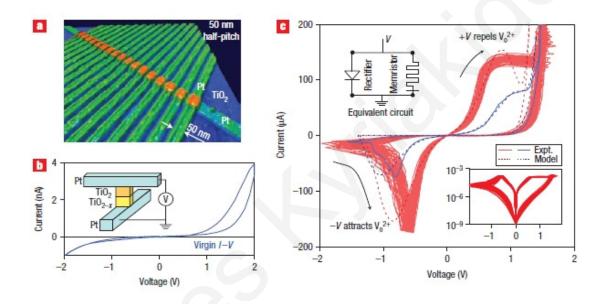

| 2.13 | The TiO <sub>2</sub> memristor, showing (a) the cross-point structure, (b) the initial I-V curve of the device, and (c) experimental vs. modeled I-V curves. Adapted from [69].                                                                                     | 39 |

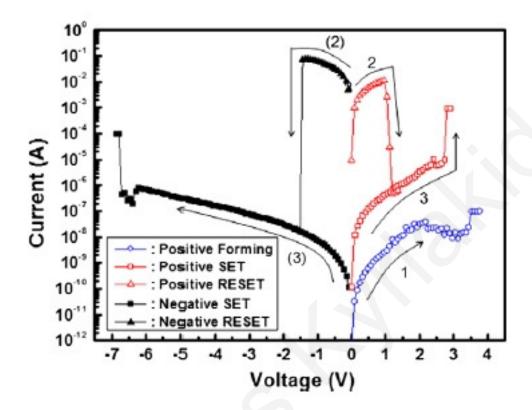

| 2.14 | Current versus voltage for one switching cycle of the Al/a-TiO <sub>2</sub> /Al device. The inset shows sweeps of the same bias polarity applied consecutively demonstrating a decrease in device resistance with each sweep. Adapted from [71].                    | 41 |

| 2.15 | Typical unipolar I–V characteristics Ti/Gd <sub>2</sub> O <sub>3</sub> /Pt structures. Blue line represents the forming process. Red and black lines represent I–V characteristics under the positive and negative bias operation, respectively. Adapted from [72]. | 42 |

| 2.16 | Conductive AFM measurements show three I-V curves of NiO devices (a) without forming, and with forming (b) once, (c) twice, and (d) four times. Adapted from [54].                                                                                                  | 43 |

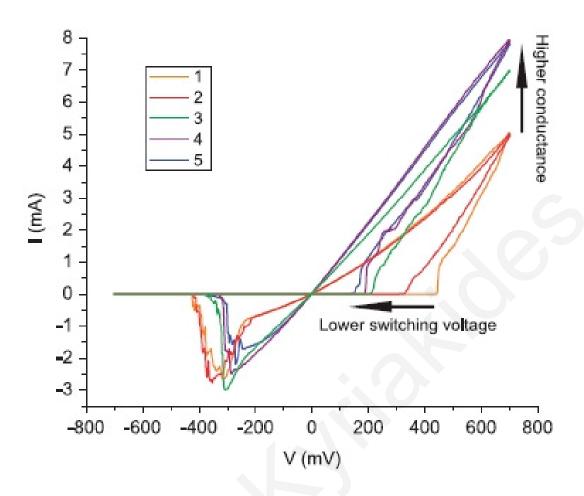

| 2.17 | Multiple voltage sweeps reveal change in device switching voltage and conductance. Adapted from [73].                                                                                                                                                               | 45 |

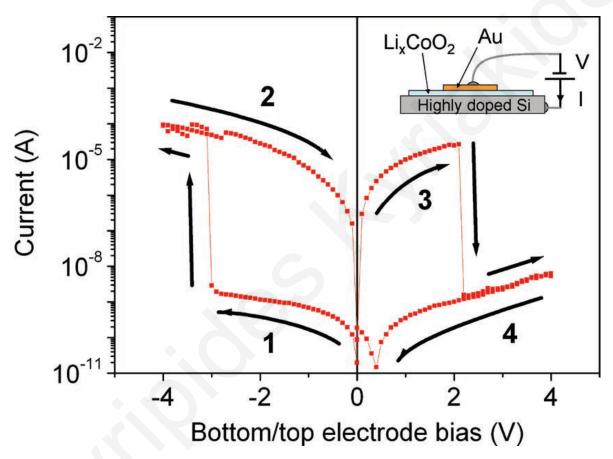

| 2.18 | I–V characteristics of the LixCoO <sub>2</sub> device (structure shown in the upper left insert). The sweeping rate of the potential, between $-4$ V and $+4$ V, is 100 mV·s-1. The rapid state transition occurs from the HRS to the LRS at about $-3$ V and from the LRS to the HRS at around $+2.5$ V. Adapted from [74]                                                                                                                                  | 46 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

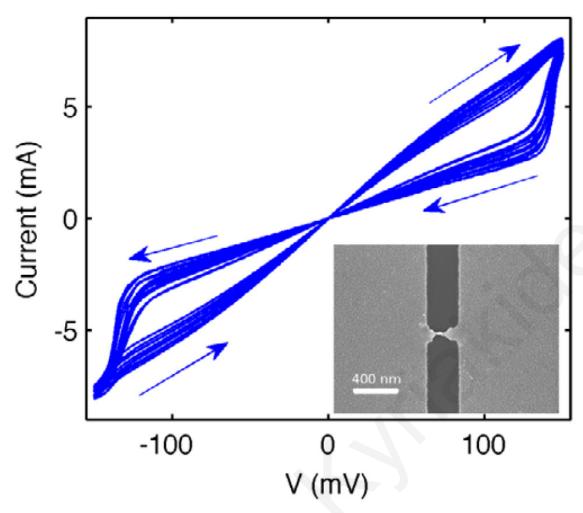

| 2.19 | I–V curves of gold nanowires generated over 14 cycles. Inset:<br>Corresponding nanowire. Adapted from [56].                                                                                                                                                                                                                                                                                                                                                  | 48 |

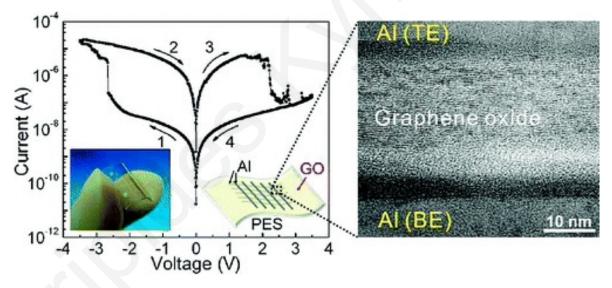

| 2.20 | Left: Typical I-V curve of a Al/G-O/Al/PES device plotted on a semilogarithmic scale with the arrows indicating the voltage sweep direction. Right: TEM image of the device. Adapted from [75]                                                                                                                                                                                                                                                               | 49 |

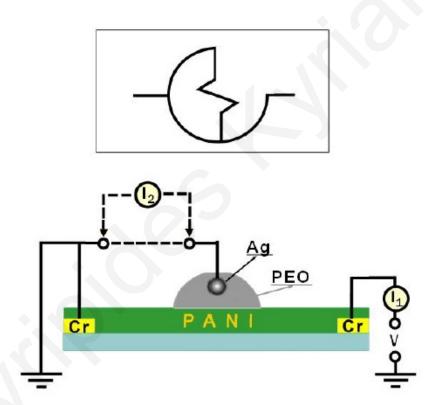

| 2.21 | PEO/PANI electrochemical element structure (below) and its symbol (above). Adapted from [87].                                                                                                                                                                                                                                                                                                                                                                | 50 |

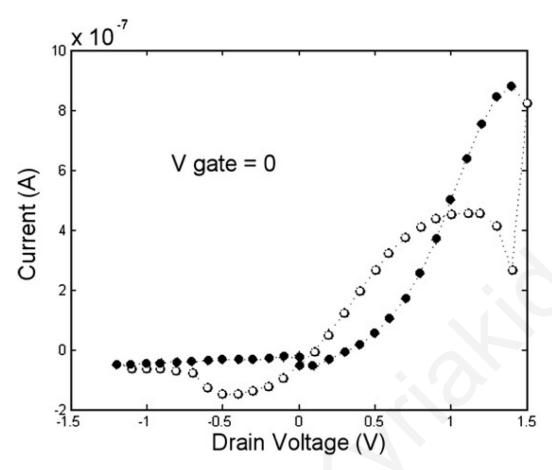

| 2.22 | Hysteresis curve in gate current with respect to the drain voltage of PEO/PANI device. Adapted from [20].                                                                                                                                                                                                                                                                                                                                                    | 52 |

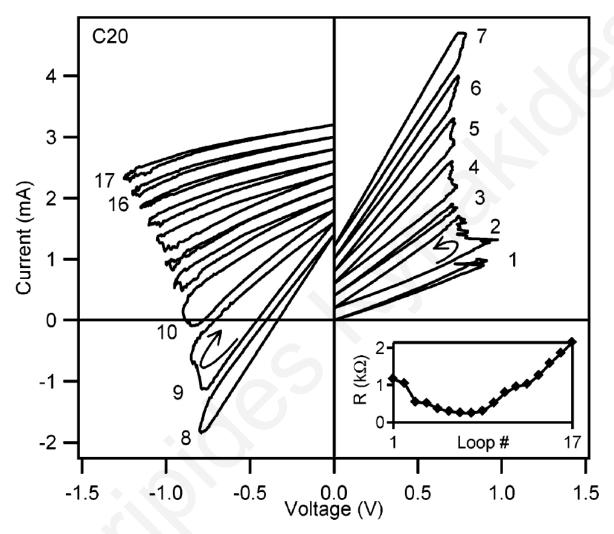

| 2.23 | Continuous resistance tuning from 1.1 k $\Omega$ to 250 $\Omega$ and back to 2.1 k $\Omega$ . Successive curves achieved by applying positive DC current-bias sweeps, numbered 1 - 7, followed by negative DC voltage-bias sweeps, numbered 8 - 17. Successive curves are offset by +0.2 mA. Adapted from [19]                                                                                                                                               | 54 |

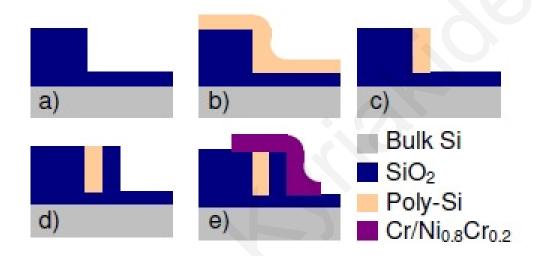

| 2.24 | Fabrication steps of poly-Si nanowire Field-Effect Transistor (FET): (a) sacrificial layer etch, (b) poly-Si deposition, (c) RIE etch, (d) LTO spacer definition, and (e) metallization. Adapted from [55].                                                                                                                                                                                                                                                  | 55 |

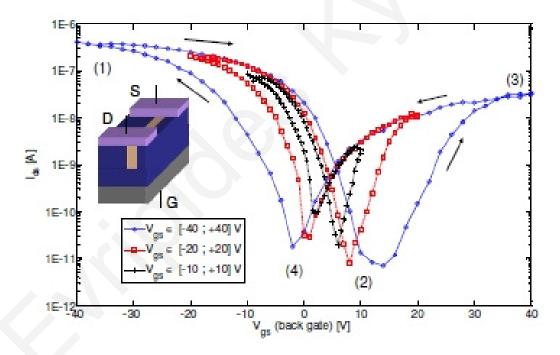

| 2.25 | Variation of hysteresis of $I_{ds}$ - $V_{gs}$ at $V_{ds} = 3.1$ V. Adapted from [55]                                                                                                                                                                                                                                                                                                                                                                        | 56 |

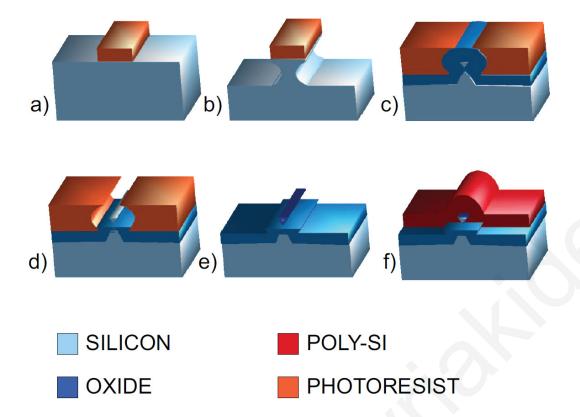

| 2.26 | Fabrication steps of gate-all-around silicon nanowire FET: (a) A photoresist line determines the nanowire position. (b) DRIE etching forms a scalloped trench. (c) After wet oxidation, the silicon trench reduces to a suspended nanowire. The caves are filled with photoresist and planarized with CMP. (d) Buffered HF oxide etch releases the SiNWs. (e) Gate oxidation. (f) Polysilicon is deposited and patterned to form the gate. Adapted from [76] | 58 |

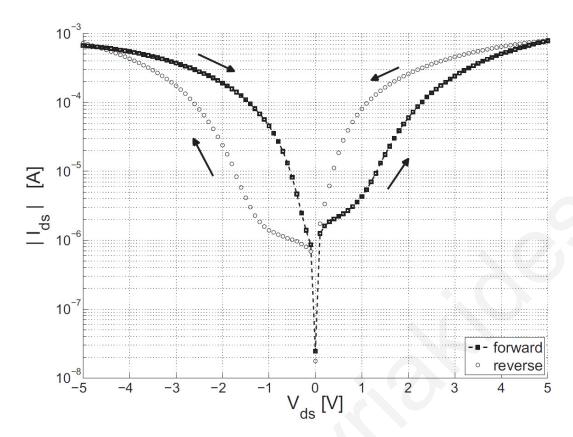

| 2.27 | Ids –Vds characteristic showing the trapping/detrapping of charges at the metal/semiconductor junction. The device channel consists of 10 SiNWs in parallel. Adapted from [76].                                                                                                                                                                                                                                                                              | 59 |

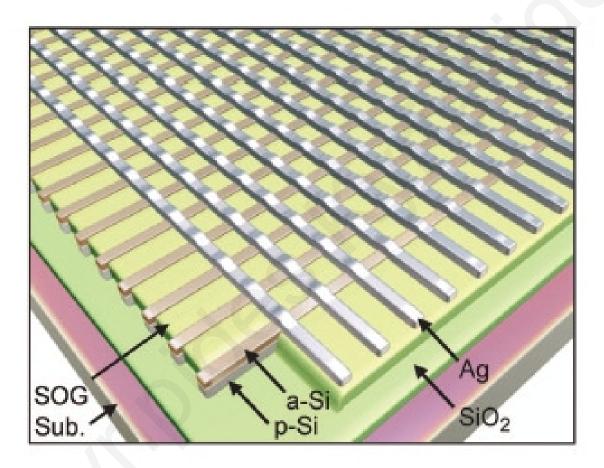

| 2.28 | Crossbar array formed with Ag and p-Si nanowire electrodes and a-Si as the active layer. Adapted from [21].                                                                                                                                                                                                                                                                                                                                                  | 60 |

| 2.29 | DC resistance switching characteristics for a typical Ag/a-Si/p-Si device with a 30 nm thick a-Si layer. Inset: The same I-V curve is plotted in semilogarithmic scale. Adapted from [21].                                                                                                                                                                                                                                                                   | 61 |

| 2.30 | Resistance switching characteristics of a typical Ag/a-Si/Ni device. Adapted from [21].                                                                                                                                                                                                                                                                                                                                                                      | 62 |

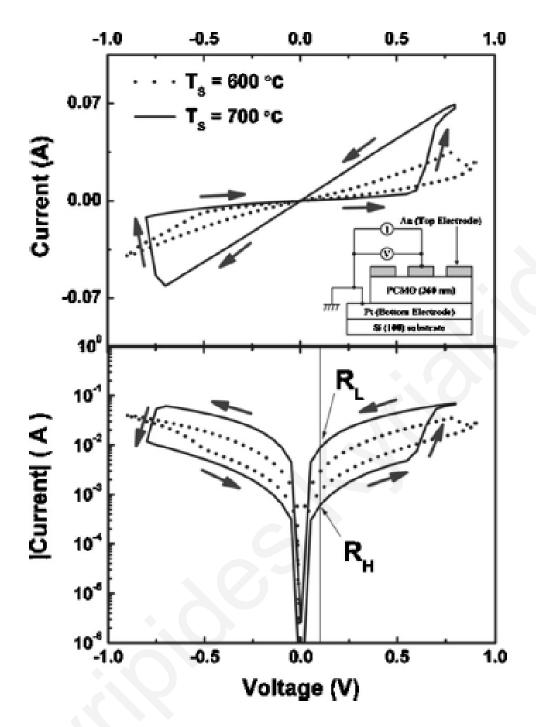

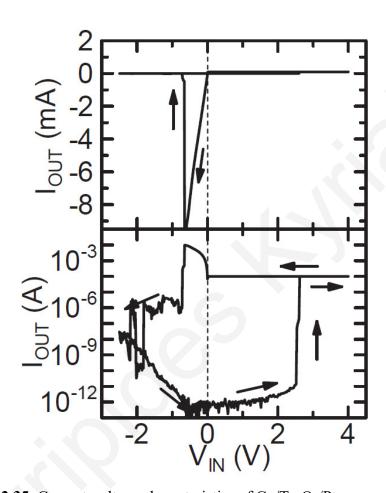

| 2.31 | I-V characterization of Au/PCMO/Pt structures for two different substrate deposition temperatures. Top panel is drawn in linear scale and bottom panel in semilogarithmic scale. Inset panel shows schematic view of I-V measurement system. Adapted from [77].                                                                                                                                                                                              | 64 |

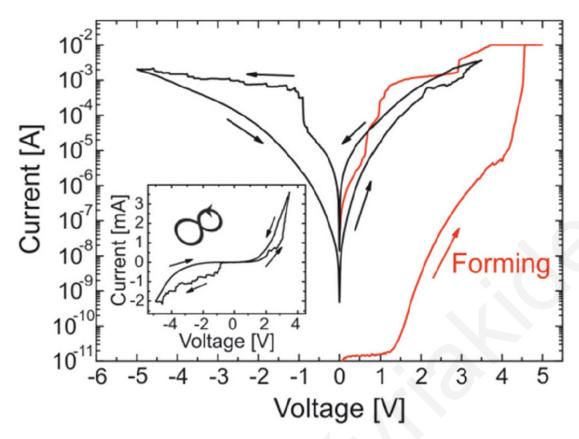

| 2.32 | Semilogarithmic hysteresis loop of SrTiO3 thin film device with initial forming indicated in red. Inset: Bow-tie loop apparent in linear scale.  Adapted from [81].                                                                                                                                                                                                                                                                                          | 66 |

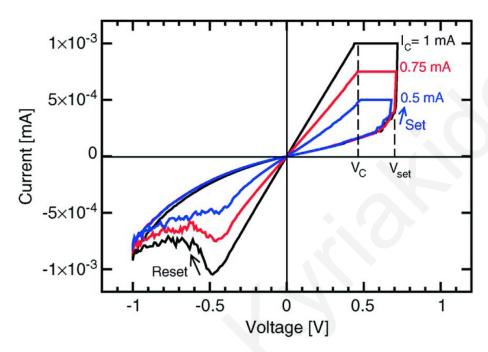

| 2.33 | RESET operations are reported for different compliance current values, denoted by IC. Adapted from [84].                                                                                                                                                               |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

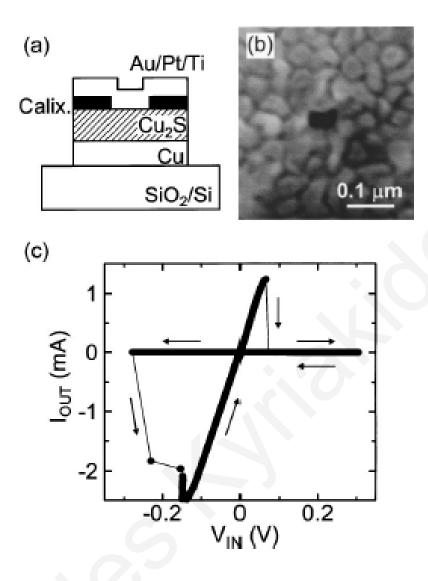

| 2.34 | (a) Schematic view of nanometer-scale Cu2S-based switch. (b) Plane view of top electrode with contact hole. (c) Current-voltage characteristics of the device with a 0.03 mm hole. Adapted from [85].                                                                  |

| 2.35 | Current-voltage characteristics of Cu/Ta <sub>2</sub> O <sub>5</sub> /Pt nanometer-scale switch in linear (top) and semilogarithmic (bottom) scales. Adapted from [86]                                                                                                 |

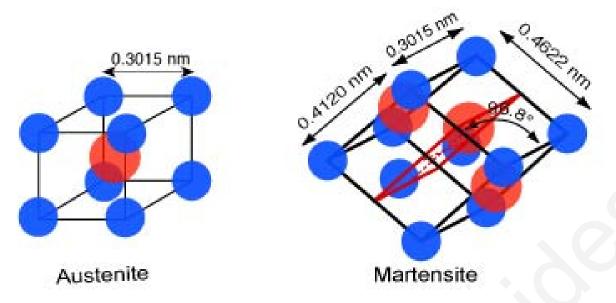

| 3.1  | The two lattice structures of the NiTi alloy; austenite and martensite.  Adapted from [93].                                                                                                                                                                            |

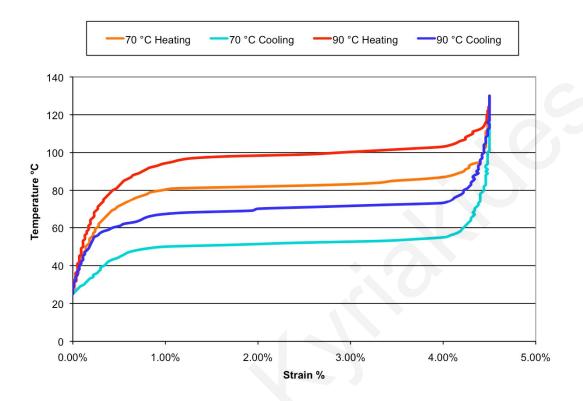

| 3.2  | Typical temperature vs. strain characteristics for NiTi. The two sets of heating-cooling curves represent different alloy compositions. Adapted from [96].                                                                                                             |

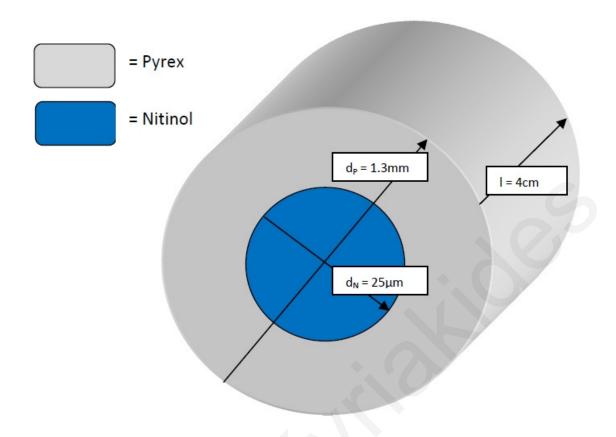

| 3.3  | Schematic of NiTi enclosure.                                                                                                                                                                                                                                           |

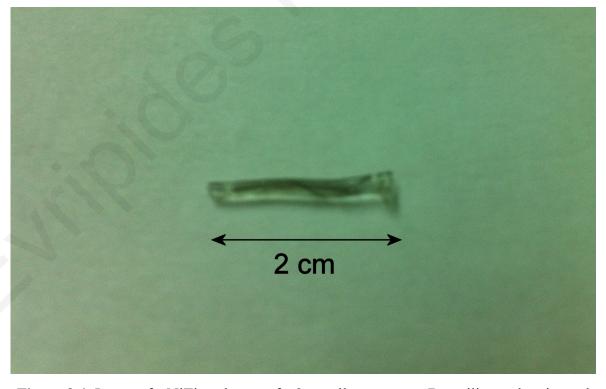

| 3.4  | Image of a NiTi enclosure of a 2 cm alloy segment. Borosilicate glass is used to encapsulate NiTi alloy in an effort to limit ambient heat loss                                                                                                                        |

| 3.5  | Four-wire resistivity measurements: The Keithley 2100 DMM, used to measure the NiTi device resistance during heating, connected to the ESPEC SU-261 temperature chamber, used for controlled heating of the NiTi devices.                                              |

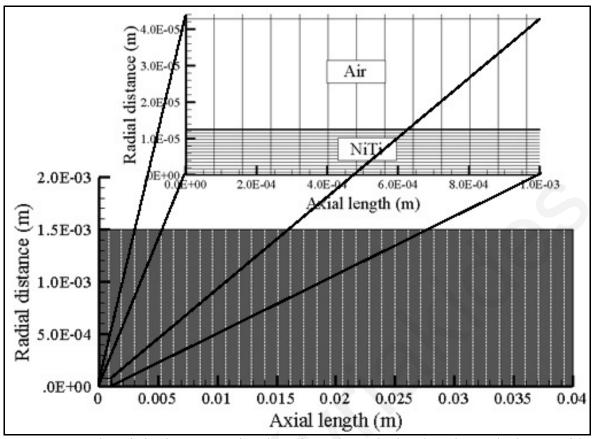

| 3.6  | The NiTi-Air computational mesh used to calculate heat loss. The lower grid shows the NiTi-Air (axisymmetric) model which consists of 28,443 cells. The top-grid detail highlights the NiTi finer model domain surrounded by the coarser air grid. Adapted from [100]. |

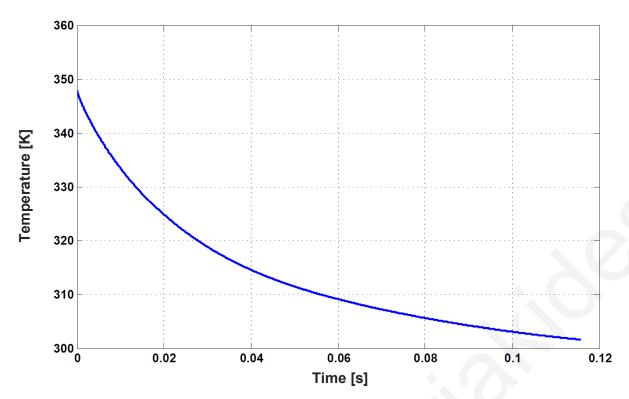

| 3.7  | Model results of NiTi cooling extracted from the CFD-ACE+ platform. The NiTi temperature is traced during convection cooling from 348 K to steady state. Adapted from [100].                                                                                           |

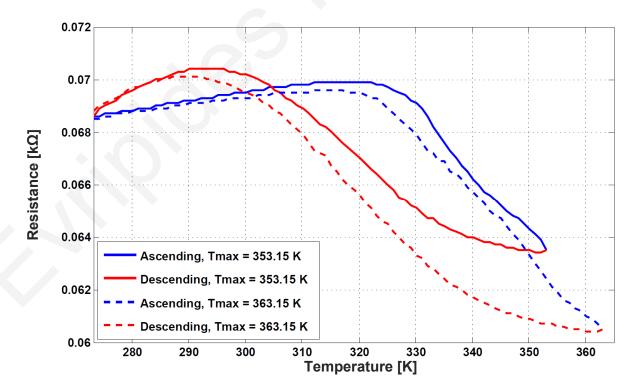

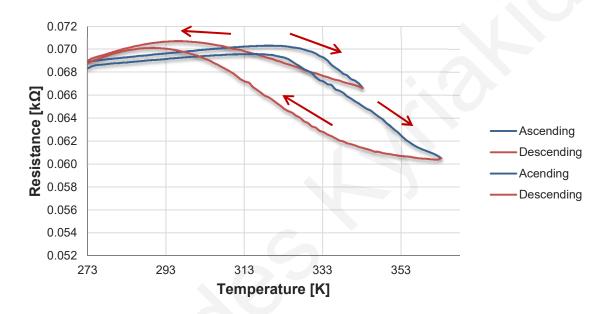

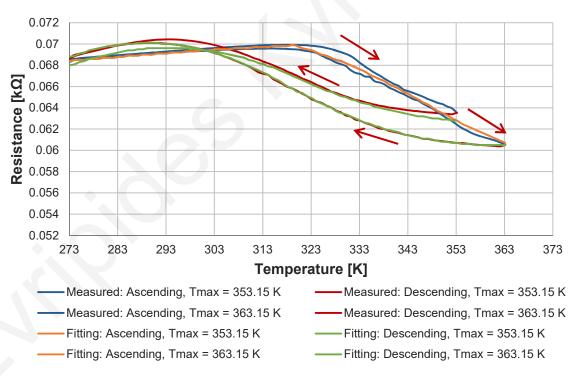

| 3.8  | NiTi resistance heating curves for $T_{max}$ of 353.15 K (80 °C) and 363.15 K (90 °C). Adapted from [100].                                                                                                                                                             |

| 3.9  | NiTi resistance measurements depicting two ascending-descending cycles with different peak temperatures.                                                                                                                                                               |

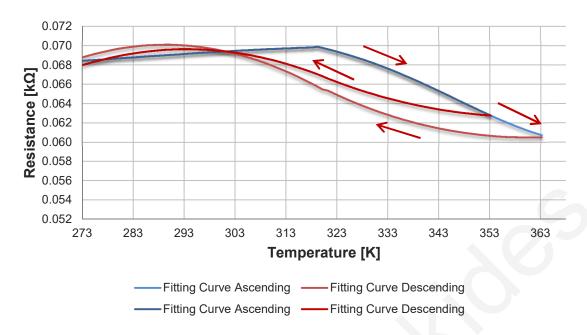

| 3.10 | NiTi resistance curve-fitting depicting the respective fitting curves of two ascending-descending cycles with different peak temperatures.                                                                                                                             |

| 3.11 | NiTi resistance measurements with respective fitting curves of two ascending-descending cycles with different peak temperatures.                                                                                                                                       |

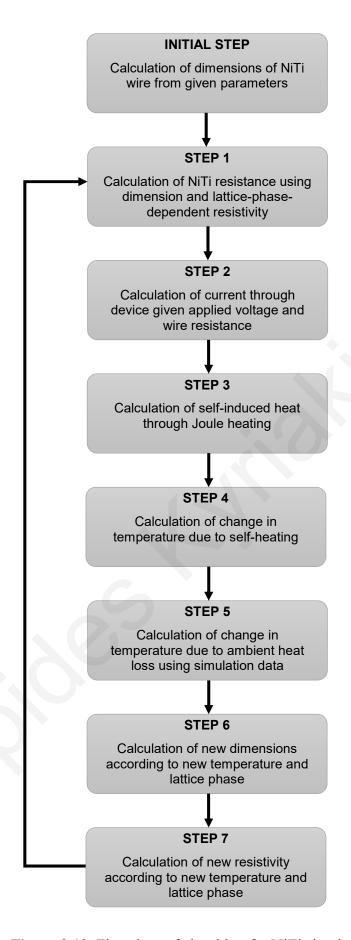

| 3.12 | Flowchart of algorithm for NiTi simulation.                                                                                                                                                                                                                            |

| 3.13 | Simulation of a 4 cm NiTi device using Verilog-A model.                                                                                                                                                                                                                |

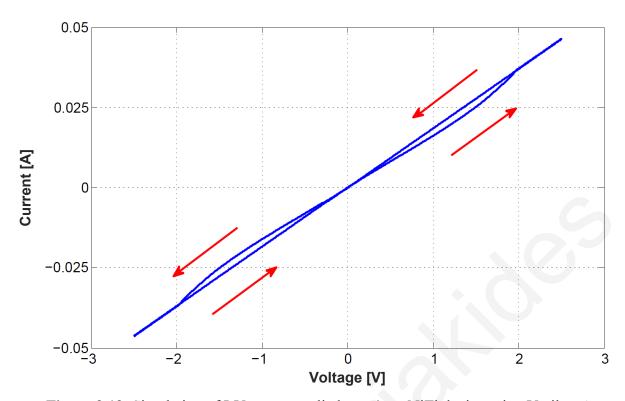

| 3.14 | I-V sweep measurement of a 4 cm NiTi device showing hysteresis                                                                                                                                                                                                         |

| 3.15 | Comparison of I-V sweep measurement with simulation obtained using the coded Verilog-A model for a 4 cm NiTi device. Both measurement and simulation show the anticipated hysteresis.                                                                                  |

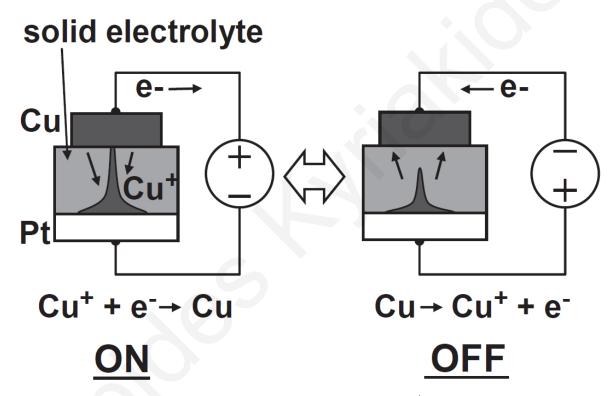

| 4.1  | Operating principle of Cu/Ta <sub>2</sub> O <sub>5</sub> device. A Cu <sup>+</sup> filament formation and dissolution is responsible for the ON and OFF states. Adapted from [86]                                                                                      |

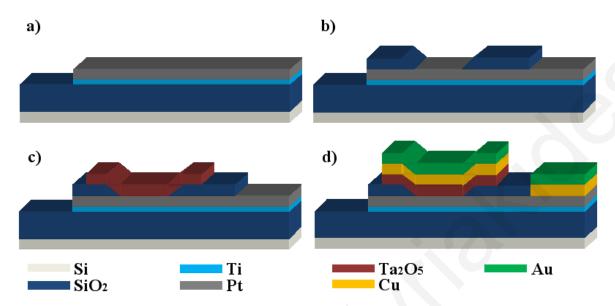

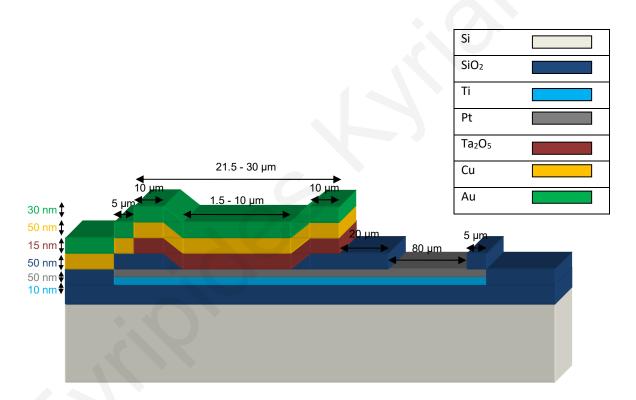

| 4.2  | Major fabrication steps of Cu/Ta <sub>2</sub> O <sub>5</sub> device: (a) Bottom electrode, (b) Interlayer dielectric, (c) Ta <sub>2</sub> O <sub>5</sub> layer, and (d) Top electrode. For clarity purposes, the illustrations are not drawn to scale. Adapted from [108] | 110 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

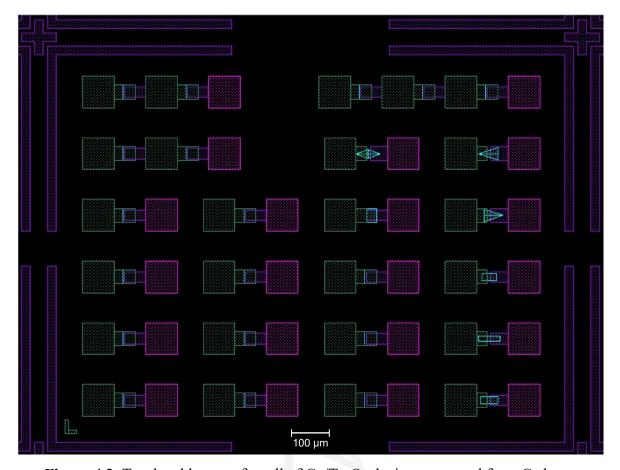

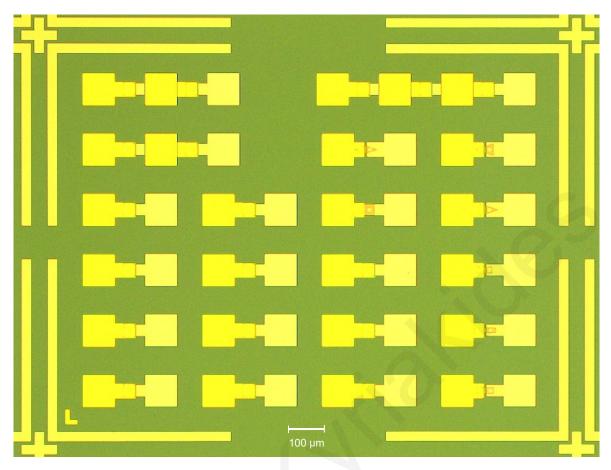

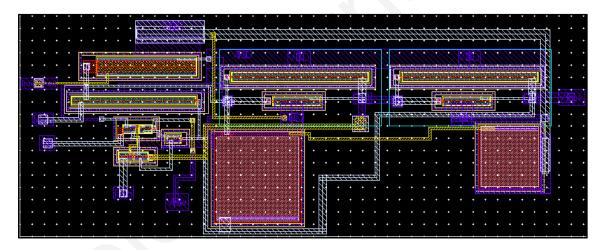

| 4.3  | Top-level layout of a cell of Cu/Ta <sub>2</sub> O <sub>5</sub> devices extracted from Cadence Virtuoso design environment. Devices included in each cell feature a variation in their active region geometry. The cell is repeated across the available wafer.           | 111 |

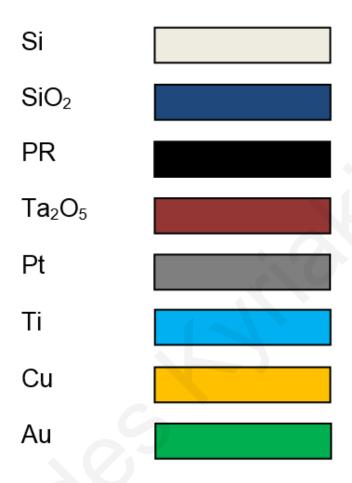

| 4.4  | Material color chart for Cu/Ta <sub>2</sub> O <sub>5</sub> fabrication.                                                                                                                                                                                                   | 117 |

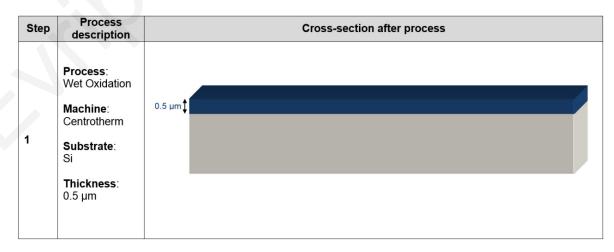

| 4.5  | Step 1 is the wet oxidation of a silicon wafer to create a SiO <sub>2</sub> layer upon which the fabrication will take place.                                                                                                                                             | 117 |

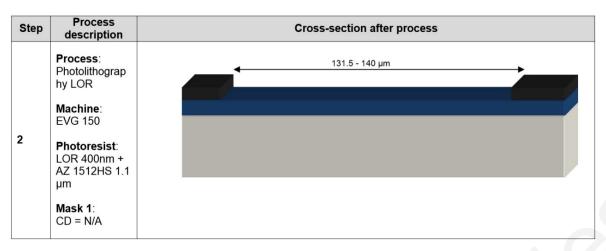

| 4.6  | Step 2 is the first step of the LOR process, namely, the LOR deposition                                                                                                                                                                                                   | 118 |

| 4.7  | Step 3.1 continues the LOR process, which involves the evaporation of two metals serving as the device's bottom electrode. In the first part, titanium is evaporated to serve as adhesive layer using LAB 600 H.                                                          | 118 |

| 4.8  | Step 3.2 is the second part of metal evaporation for the bottom electrode. Here, platinum is evaporated using LAB 600 H.                                                                                                                                                  | 118 |

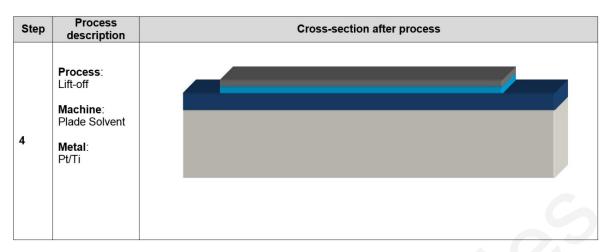

| 4.9  | Step 4 completes the LOR process. The LOR is chemically lifted in a wet bench, leaving behind the desired bilayer of Pt/Ti.                                                                                                                                               | 119 |

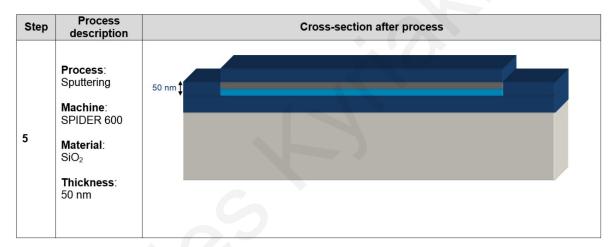

| 4.10 | Step 5 is the deposition through sputtering of the SiO <sub>2</sub> interlayer dielectric                                                                                                                                                                                 | 119 |

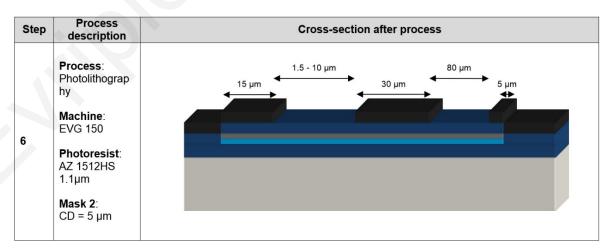

| 4.11 | Step 6 is the application of the second mask, with critical dimension 5 μm. This step defines the active device area and the access window to the bottom electrode.                                                                                                       | 119 |

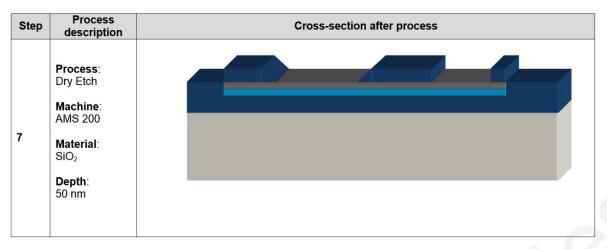

| 4.12 | Step 7 is the dry etching of the SiO <sub>2</sub> layer to reveal the bottom electrode, thus defining the device's active region.                                                                                                                                         | 120 |

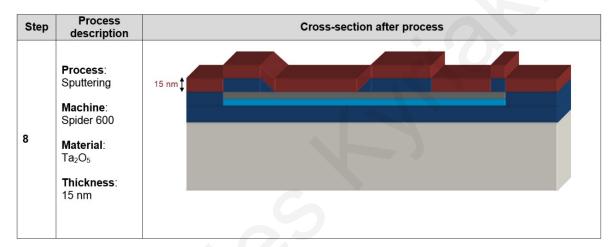

| 4.13 | Step 8 is the sputtering of the Ta <sub>2</sub> O <sub>5</sub> layer using Spider 600                                                                                                                                                                                     | 120 |

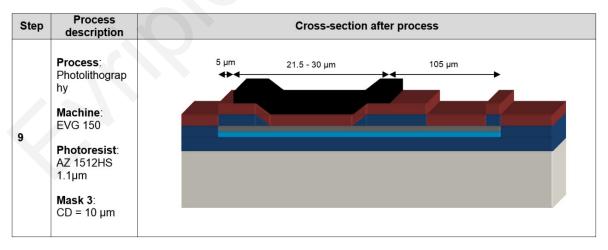

| 4.14 | Step 9 is the deposition of photoresist to define the areas where Ta <sub>2</sub> O <sub>5</sub> is to be etched.                                                                                                                                                         | 120 |

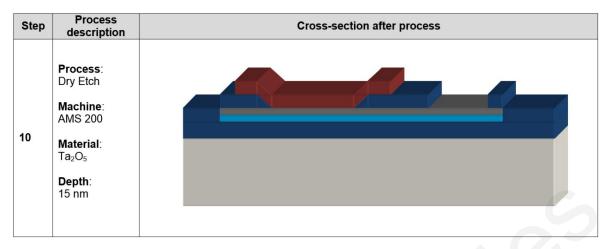

| 4.15 | Step 10 is the dry etching of the Ta <sub>2</sub> O <sub>5</sub> layer.                                                                                                                                                                                                   | 121 |

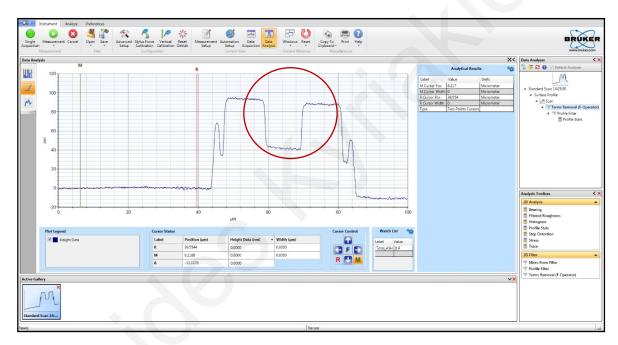

| 4.16 | Profilometer analysis of a fabricated device after Step 10. The trench (circled) represents the device's active area, verifying the expected structure profile shown in Fig. 4.15. This ensures no overetching or underetching took place.                                | 121 |

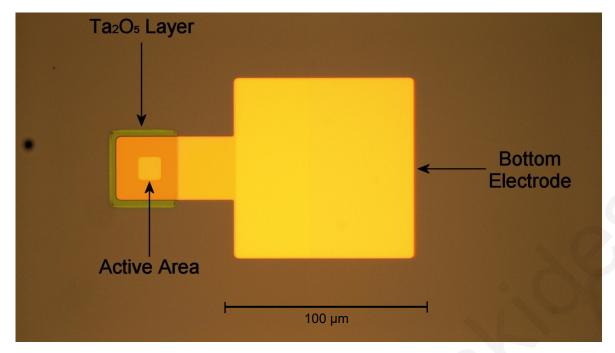

| 4.17 | Microscope image of the device as intermediate verification after Step 10. The Ta <sub>2</sub> O <sub>5</sub> layer is covering the device's active region on the left. The bottom electrode is visible on the right.                                                     | 122 |

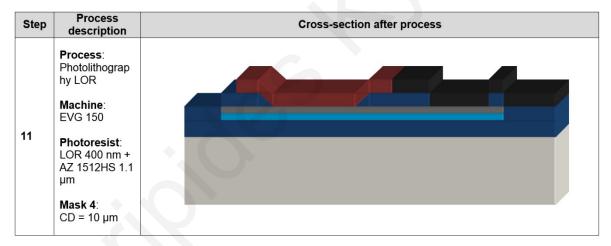

| 4.18 | Step 11 is the first part of the top electrode fabrication. LOR is deposited to define where the top electrode is to be lifted off.                                                                                                                                       | 122 |

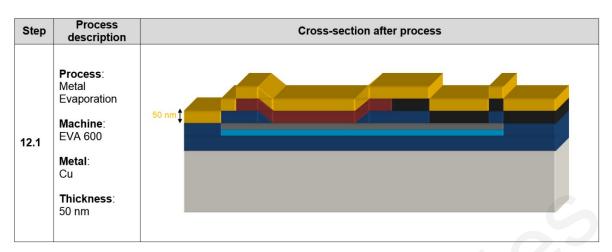

| 4.19 | Step 12.1 continues the LOR process, which involves the evaporation of two metals serving as the device's top electrode. In the first part, 50 nm-thick copper is evaporated using the EVA 600.                                                                           | 123 |

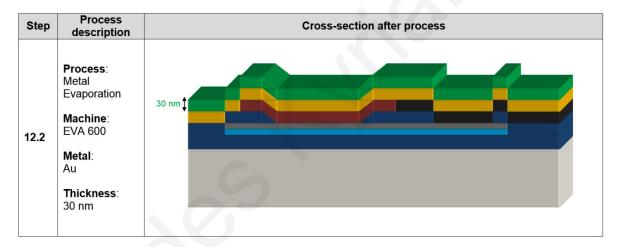

| 4.20 | Step 12.2 is the second part of metal evaporation for the top electrode. Here, gold is evaporated using the EVA 600.                                                                                                                                                      | 123 |

| 4.21 | Step 13 completes the LOR process. The LOR is chemically lifted in a wet bench, leaving behind the desired bilayer of Au/Cu.                                                                                                                                                                           |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.22 | Representation of final fabricated Cu/Ta <sub>2</sub> O <sub>5</sub> device. The layer thicknesses are colored in accordance with the respective materials for clarity                                                                                                                                 |

| 4.23 | Microscope image of fabricated "cell" of Cu/Ta <sub>2</sub> O <sub>5</sub> devices. Each "cell" contains a library of structures with geometrical variations.                                                                                                                                          |

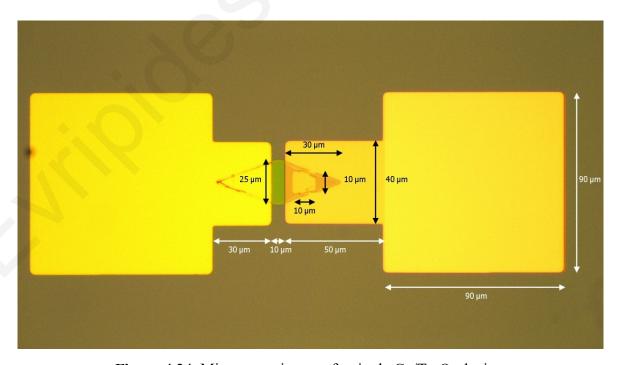

| 4.24 | Microscope image of a single Cu/Ta <sub>2</sub> O <sub>5</sub> device.                                                                                                                                                                                                                                 |

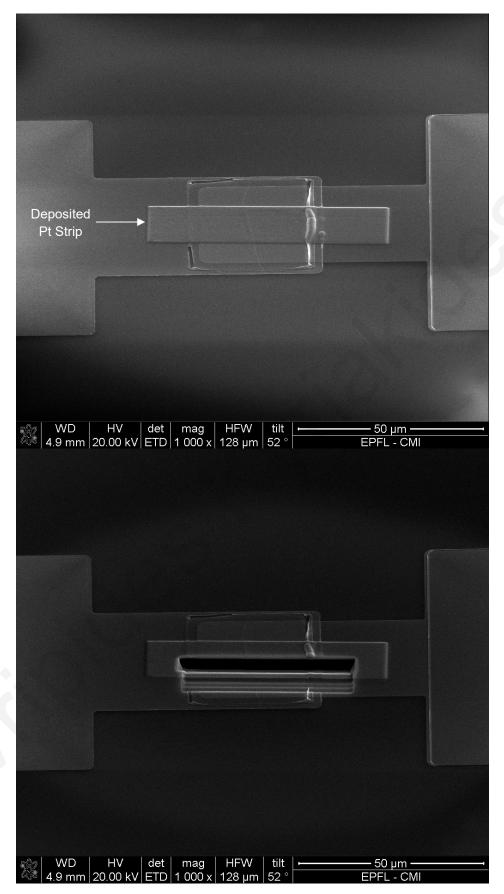

| 4.25 | Top: Platinum deposition during FIB procedure shown as a horizontal strip across active device region. Bottom: Successive etching steps of smaller areas results in tapered etching of the active device region during the FIB procedure.                                                              |

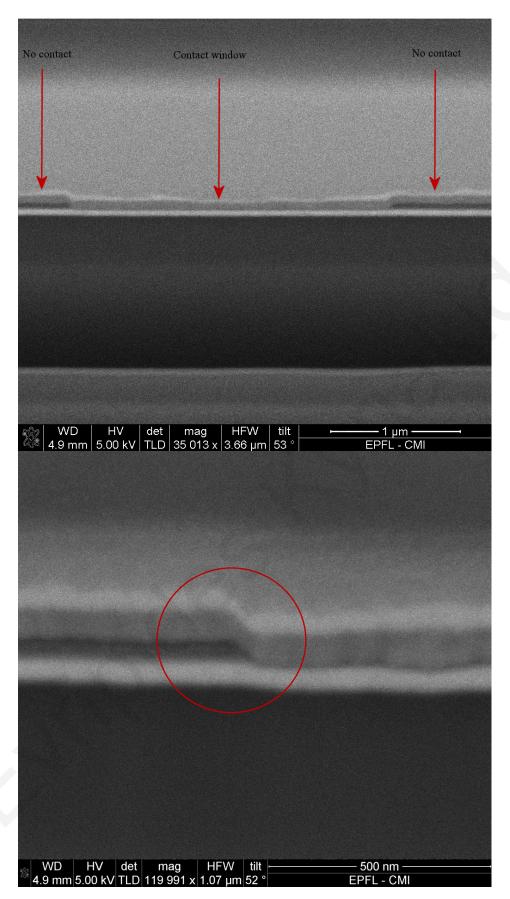

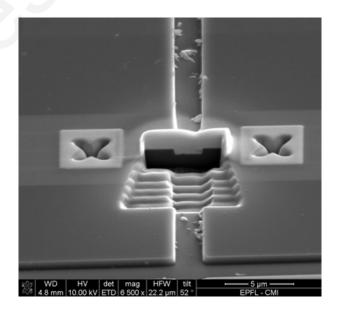

| 4.26 | SEM/FIB image of a device cross-section. Top: Definition of the active device area. Bottom: The SiO <sub>2</sub> layer to the left of the junction edge (circled) acts as an interlayer dielectric between the Ta <sub>2</sub> O <sub>5</sub> and platinum layers                                      |

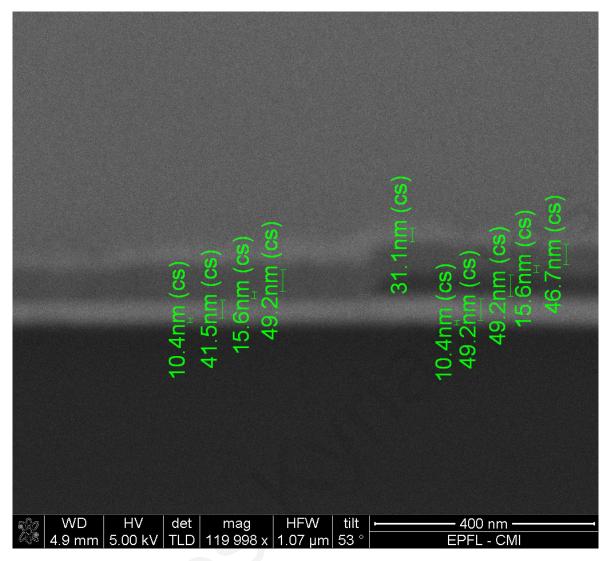

| 4.27 | Verification of layer thicknesses becomes possible using the SEM imaging capabilities.                                                                                                                                                                                                                 |

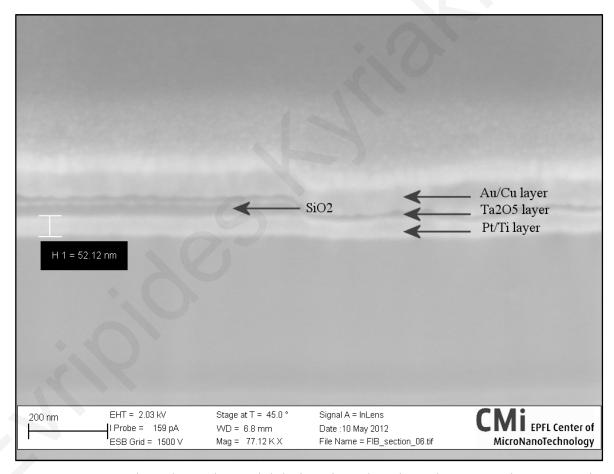

| 4.28 | Junction edge and material designation taken through a SEM. The structure is believed to owe its behavior to electrochemical processes taking place in the Ta <sub>2</sub> O <sub>5</sub> layer.                                                                                                       |

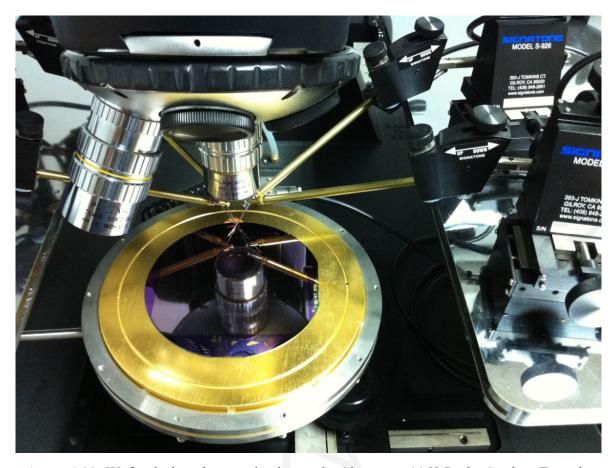

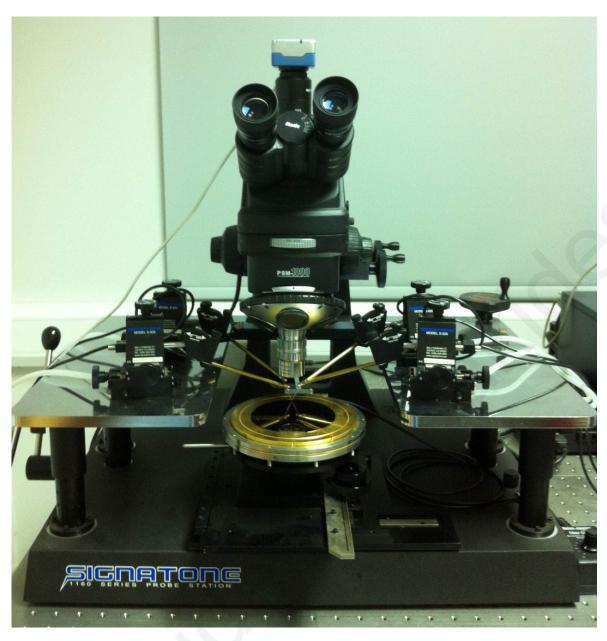

| 4.29 | Wafer during characterization at the Signatone 1160 Probe Station. Four tips in total allow contact to the 100 $\mu m \times 100 \mu m$ device pads                                                                                                                                                    |

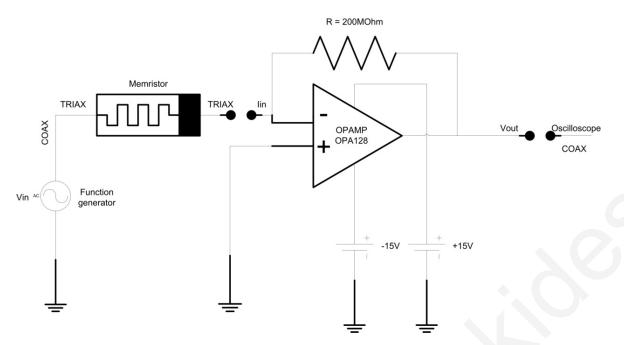

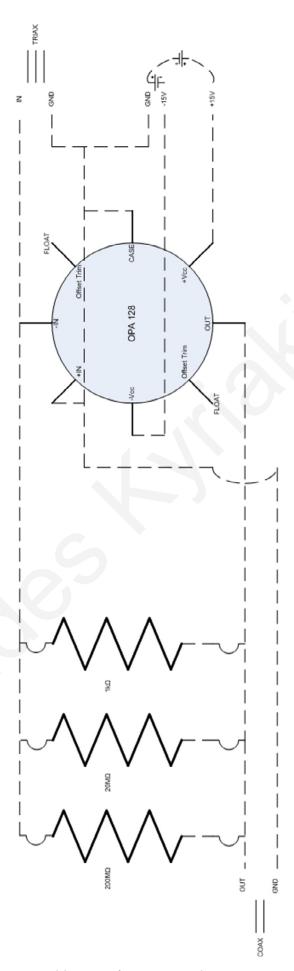

| 4.30 | Block diagram of custom-made measurement module.                                                                                                                                                                                                                                                       |

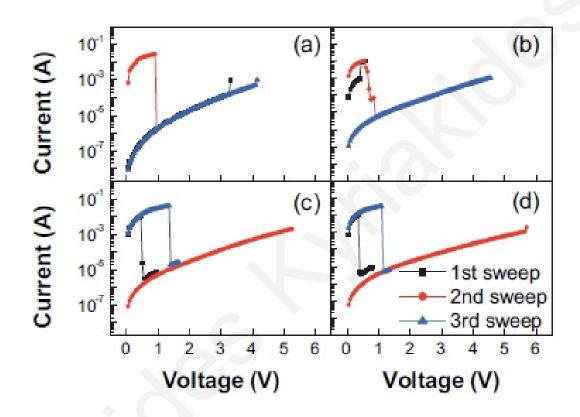

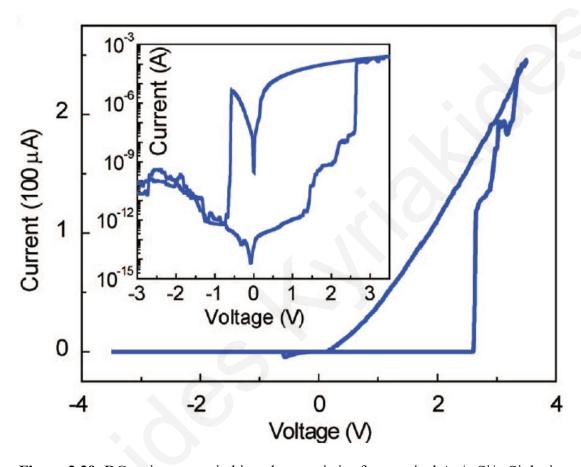

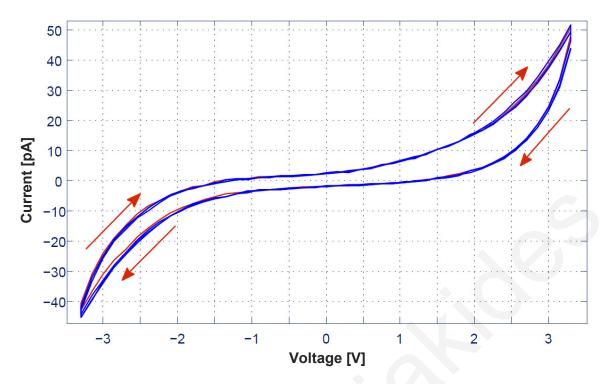

| 4.31 | Pre-forming I-V hysteresis loop comprising four sweeps. Adapted from [108].                                                                                                                                                                                                                            |

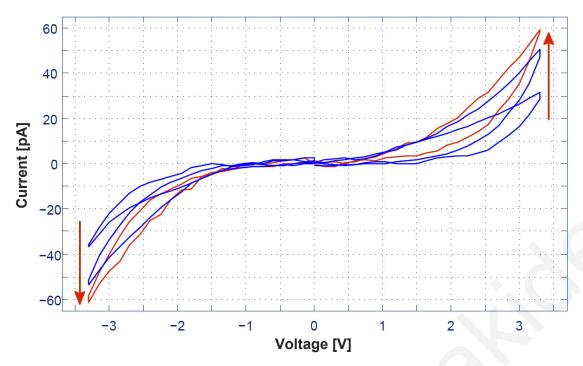

| 4.32 | Sweep frequency variation. Red arrows indicate increasing frequency. Adapted from [108].                                                                                                                                                                                                               |

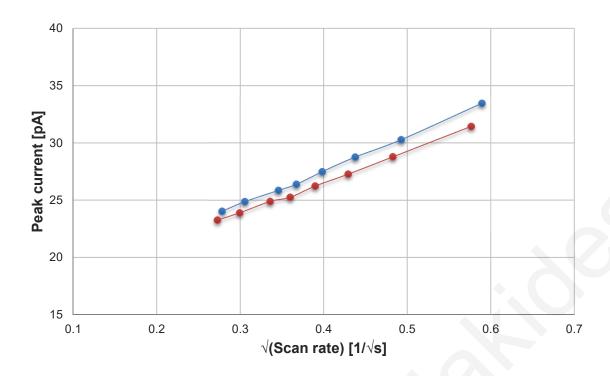

| 4.33 | Plot of peak current versus square root of scan rate from Tab. 4.2                                                                                                                                                                                                                                     |

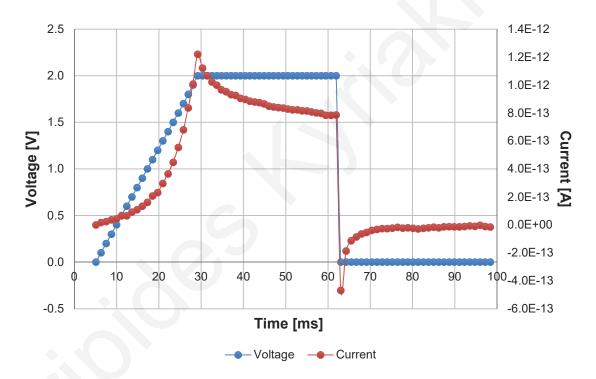

| 4.34 | Current and voltage across device as a function of time illustrating current discharge.                                                                                                                                                                                                                |

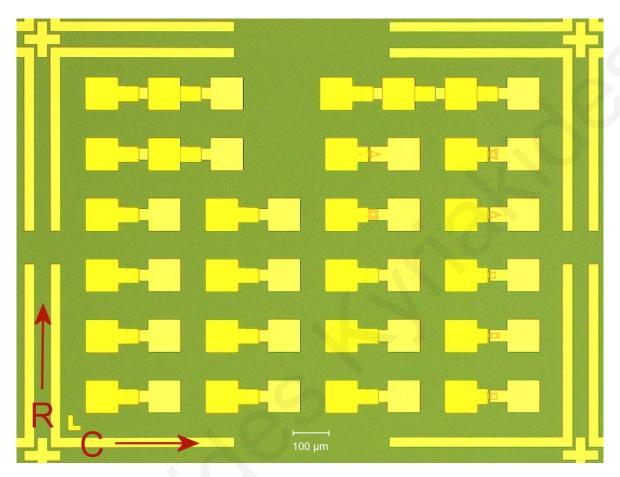

| 4.35 | Microscope image of fabricated "cell" of Cu/Ta <sub>2</sub> O <sub>5</sub> devices. Each "cell" contains a library of structures with geometrical variations. The naming convention follows C for column left to right and R for row bottom to top, e.g. the bottom left device is designated as C1R1. |

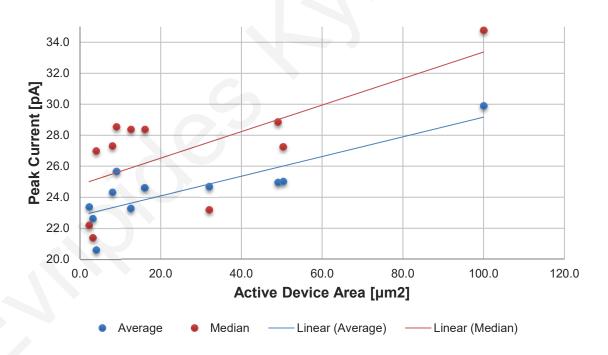

| 4.36 | Chart of peak current versus active device area for devices in Tab. 4.3. Blue                                                                                                                                                                                                                          |

|      | markers indicate average values, whereas red markers indicate median values. A linear regression fit is shown for each set of data.                                                                                                                                                                    |

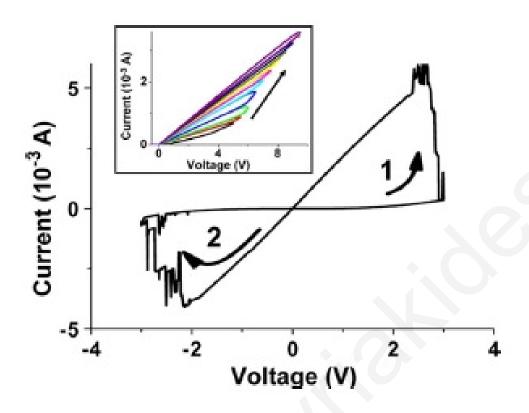

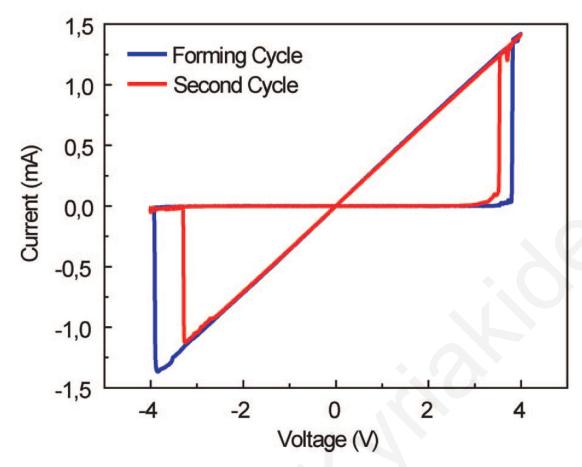

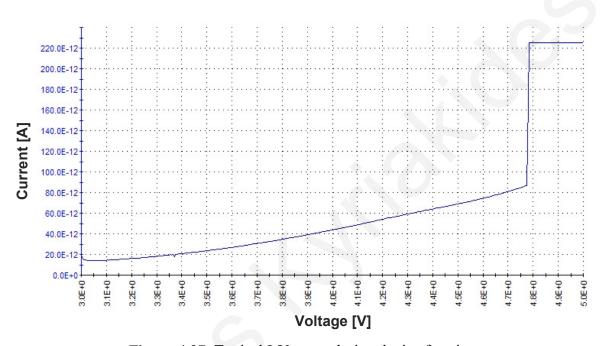

| 4.37 | Typical I-V curve during device forming.                                                                                                                                                                                                                                                               |

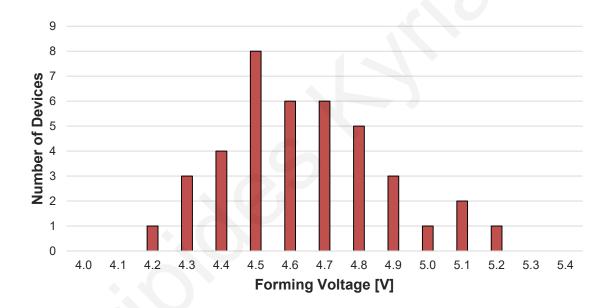

| 4.38 | Forming voltage histogram. The mean value was 4.69 V with standard deviation 0.239 V.                                                                                                                                                                                                                  |

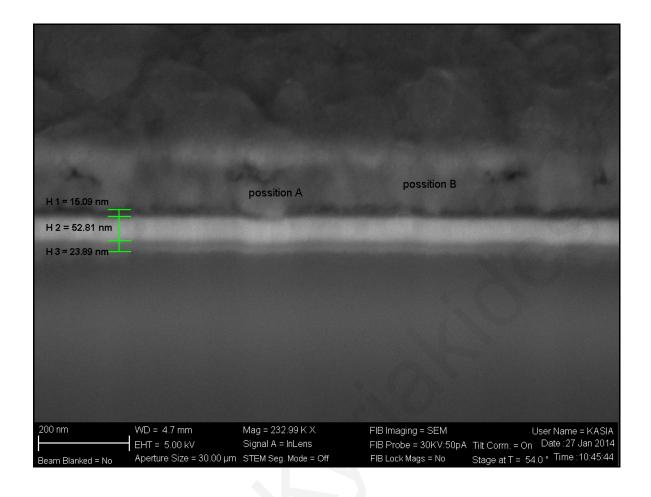

| 4.39 | FIB/FESEM image of copper filament formed in the Ta <sub>2</sub> O <sub>5</sub> layer. The copper filament extending from the top to the bottom electrode is visible in positions A and B.                                                                                                             |

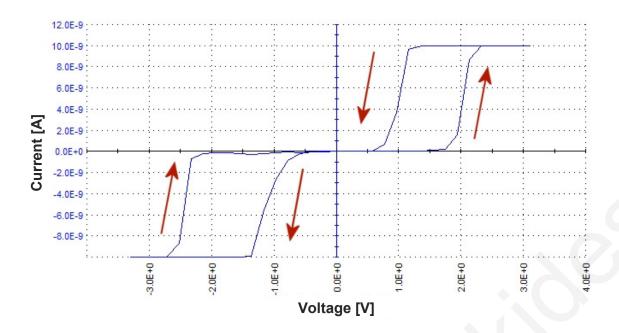

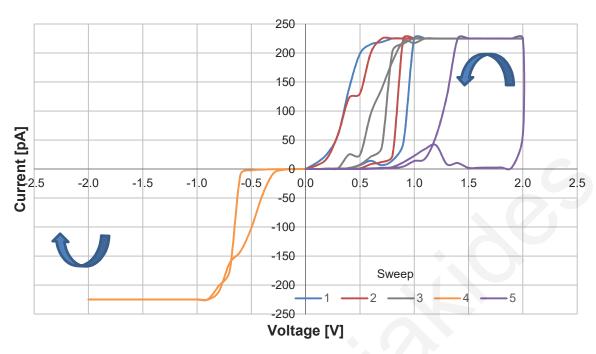

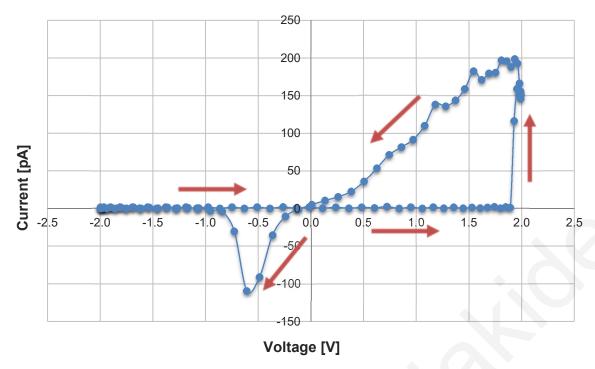

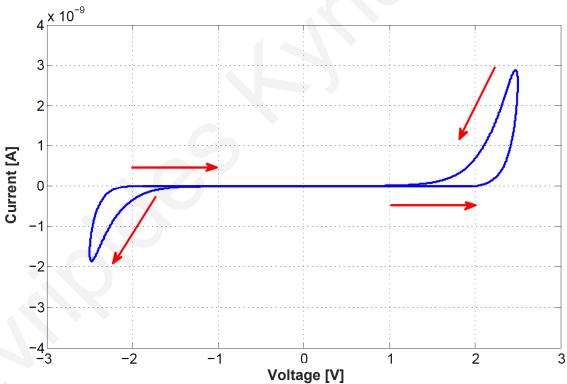

| 4.40 | range is ±3 V and the current compliance set at 10 nA.                                                                                                                                                                                                                                                                                                             |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

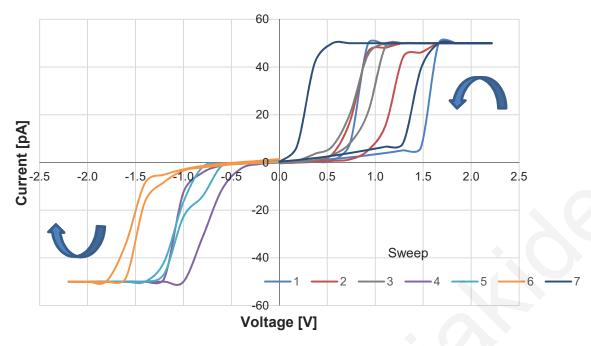

| 4.41 | I-V sweeps of devices in the post-forming region with $\pm 2$ V sweep range and 225 pA compliance current. The order of voltage sweeps is shown in the index on the right of the plot.                                                                                                                                                                             |

| 4.42 | I-V sweeps of devices in the post-forming region with $\pm 2.25$ V sweep range and 50 pA compliance current. The order of voltage sweeps is shown in the index on the right of the plot.                                                                                                                                                                           |

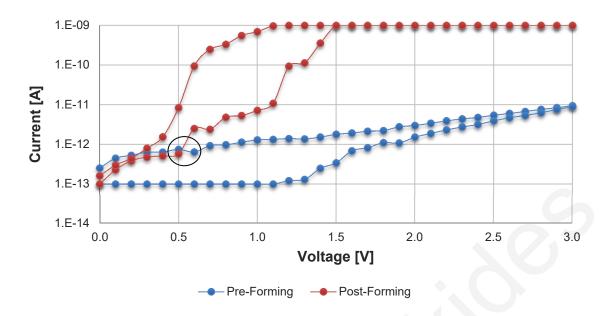

| 4.43 | Semilogarithmic graph for definition of threshold voltage with the threshold voltage circled.                                                                                                                                                                                                                                                                      |

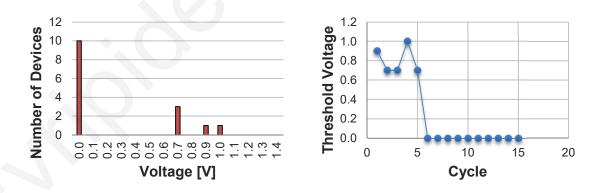

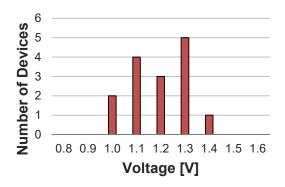

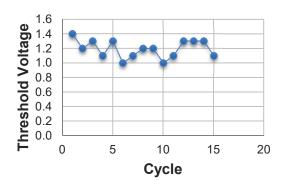

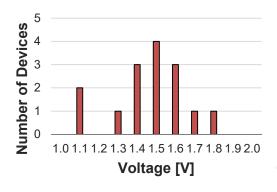

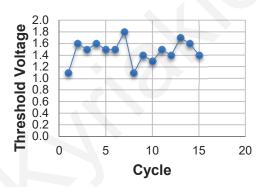

| 4.44 | Threshold voltage histogram (left) and threshold voltage evolution (right) for device A.                                                                                                                                                                                                                                                                           |

| 4.45 | Threshold voltage histogram (left) and threshold voltage evolution (right) for device B.                                                                                                                                                                                                                                                                           |

| 4.46 | Threshold voltage histogram (left) and threshold voltage evolution (right) for device C.                                                                                                                                                                                                                                                                           |

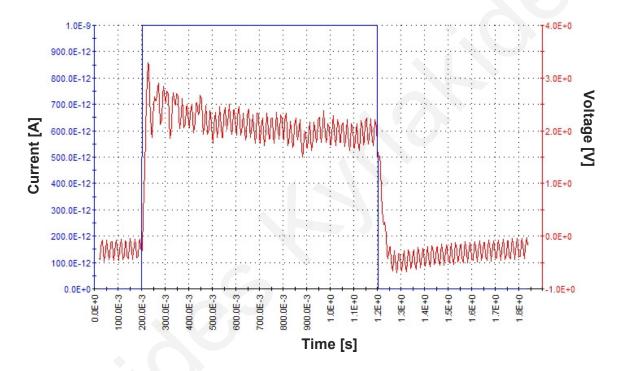

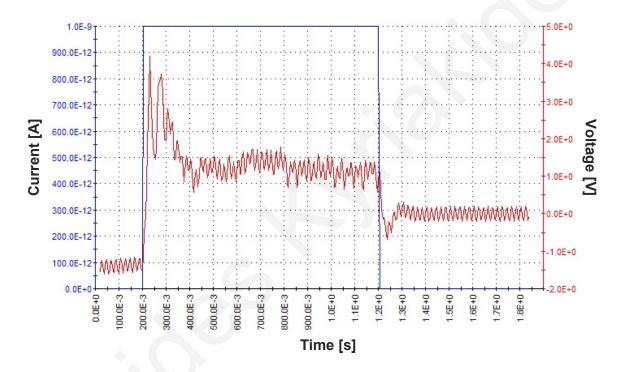

| 4.47 | Typical response of DUT under pulse input.                                                                                                                                                                                                                                                                                                                         |

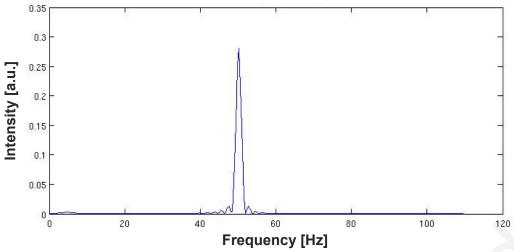

| 4.48 | Power Spectral Density of DC signal.                                                                                                                                                                                                                                                                                                                               |

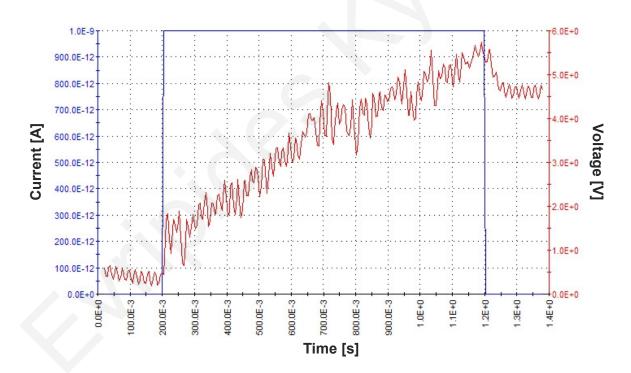

| 4.49 | Pulse applied to device in pre-forming region.                                                                                                                                                                                                                                                                                                                     |

| 4.50 | Pulse applied to DUT in post-forming region.                                                                                                                                                                                                                                                                                                                       |

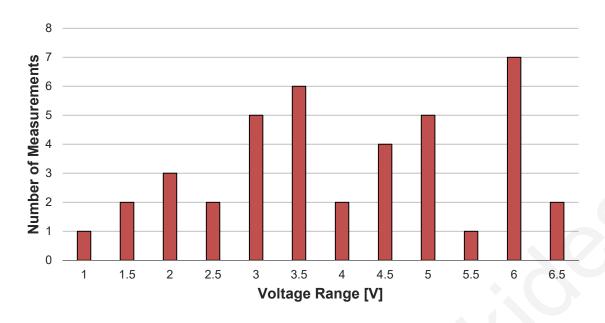

| 4.51 | Histogram of peak voltage range count.                                                                                                                                                                                                                                                                                                                             |

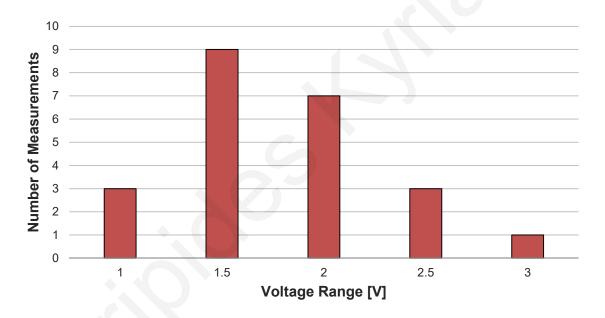

| 4.52 | Histogram of settling voltage range count.                                                                                                                                                                                                                                                                                                                         |

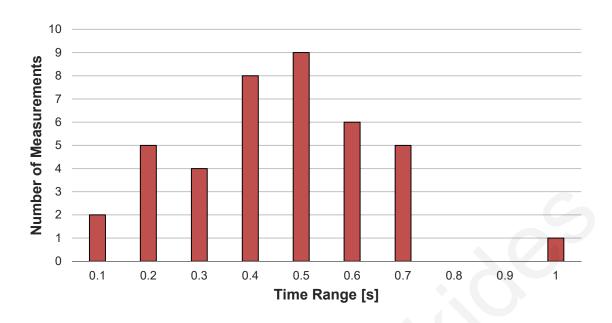

| 4.53 | Histogram of settling time range count.                                                                                                                                                                                                                                                                                                                            |

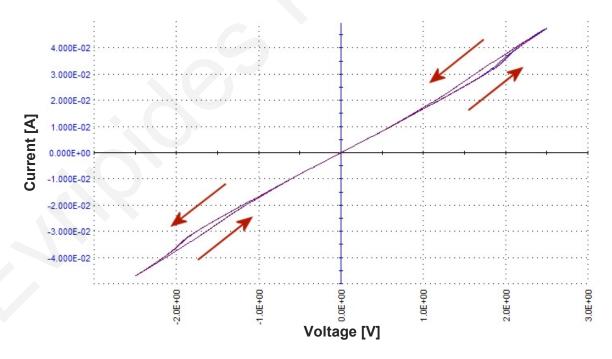

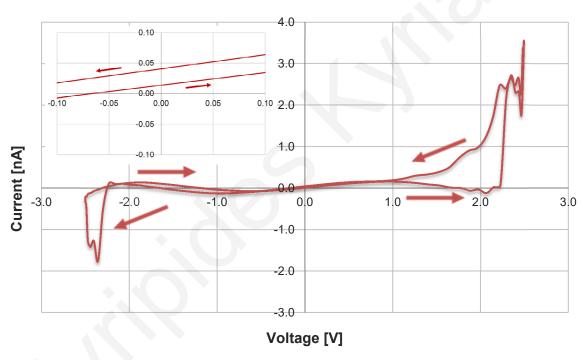

| 4.54 | AC measurement using custom-made measurement module at 10 Hz, with ±2 V sweep range and 200 pA compliance current, showing bow-tie hysteresis loop.                                                                                                                                                                                                                |

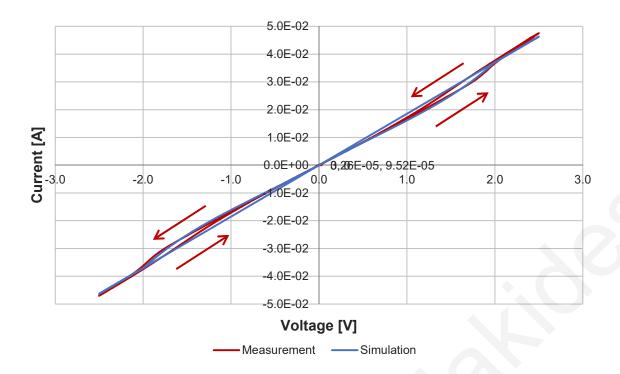

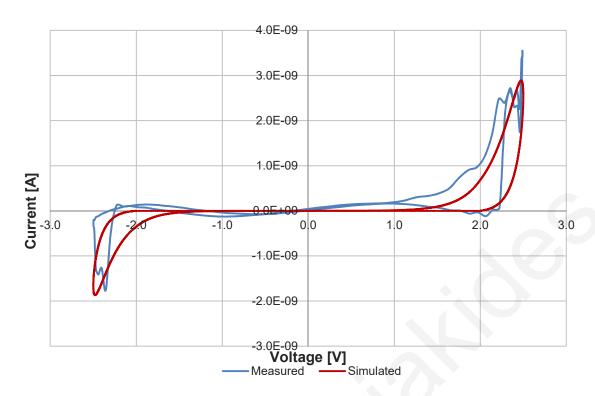

| 4.55 | Extracted response of Cu/Ta <sub>2</sub> O <sub>5</sub> Verilog-A model in Cadence environment for 2.5 V, 1 kHz sinusoidal excitation. Simulation parameters are: $a_1 = 8 \times 10^{-5}$ , $a_2 = 1.5 \times 10^{-6}$ , $b_1 = 4$ , $b_2 = 4.5$ , $c_1 = 2 \times 10^{-5}$ , $c_2 = 2 \times 10^{-5}$ , $d_1 = 1$ , $d_2 = 1$ , $V_p = 1.55$ , and $V_n = 0.9$ . |

| 4.56 | Measured post-forming AC behavior of Cu/Ta <sub>2</sub> O <sub>5</sub> device at 2.5 V, 1 kHz. Inset: Magnification of curve around the origin region.                                                                                                                                                                                                             |

| 4.57 | Comparison of measured and modeled post-forming AC behavior of Cu/Ta <sub>2</sub> O <sub>5</sub> device at 2.5 V, 1 kHz.                                                                                                                                                                                                                                           |

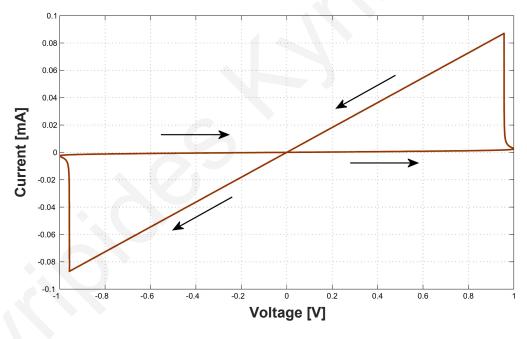

| 5.1  | Hysteresis curve of memristor element resulting from Verilog-A model run in Cadence environment. Adapted from [126].                                                                                                                                                                                                                                               |

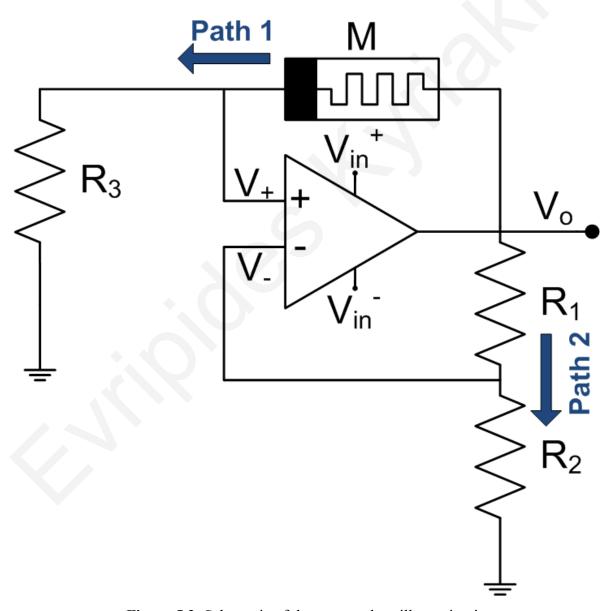

| 5.2  | Schematic of the proposed oscillator circuit. Adapted from [126]                                                                                                                                                                                                                                                                                                   |

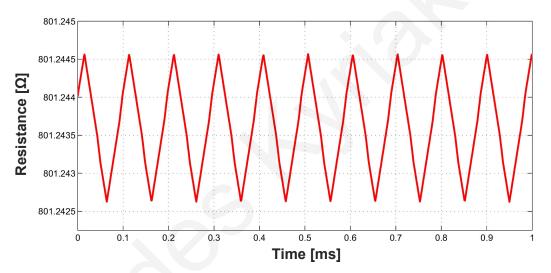

| 5.3  | Resistance variation of memristor during oscillation. Adapted from [126]                                                                                                                                                                                                                                                                                           |

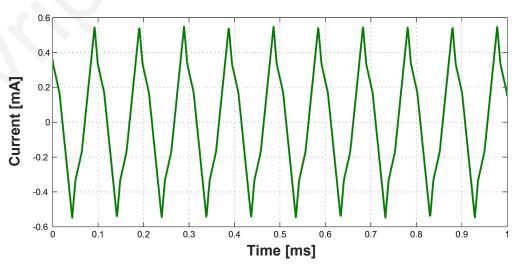

| 5.4  | Current through memristor during oscillation. Adapted from [126]                                                                                                                                                                                                                                                                                                   |

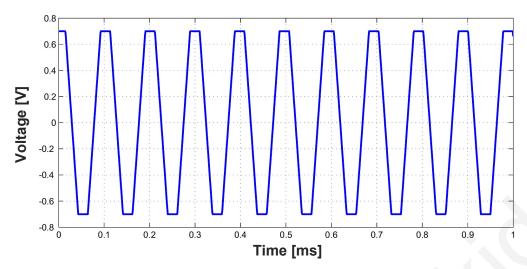

| 5.5  | Circuit output voltage during oscillation. Adapted from [126].                                                                                                                                                                                                                                                                                                     |

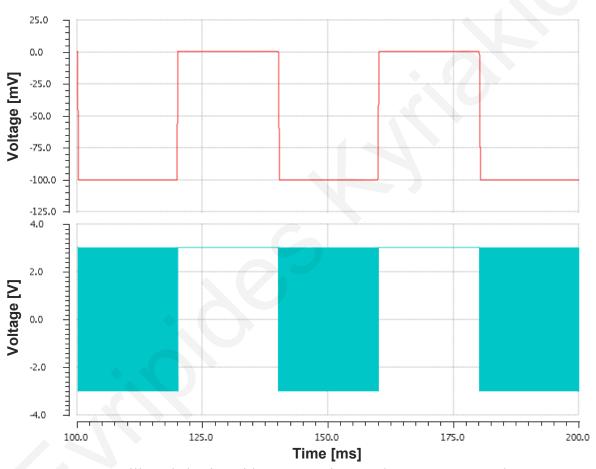

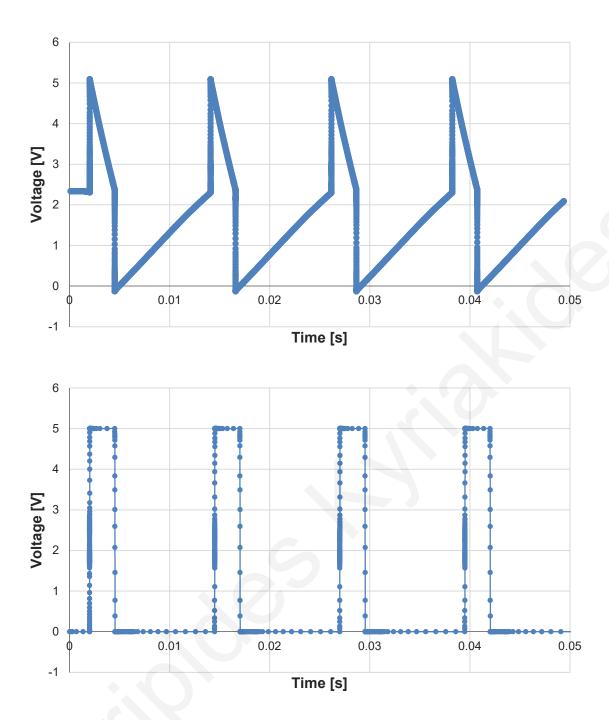

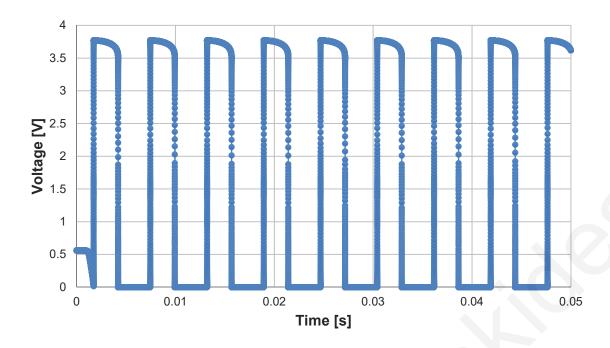

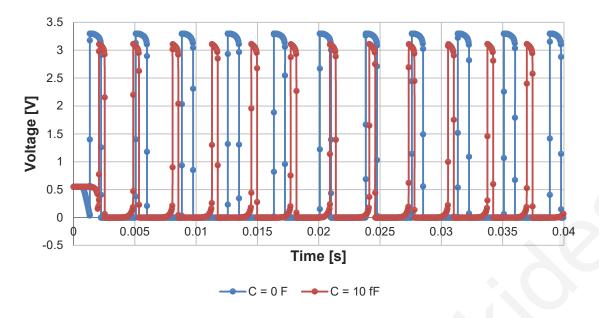

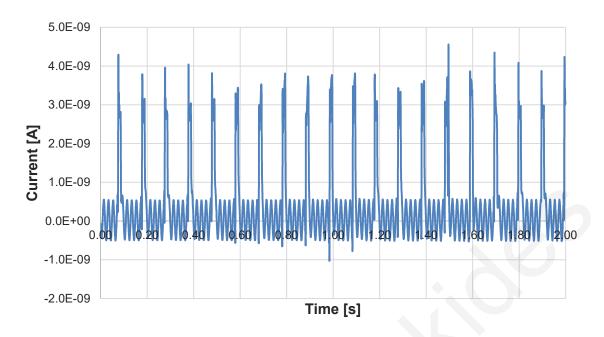

| 3.0  | Output oscillations.                                                                                                                                           |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

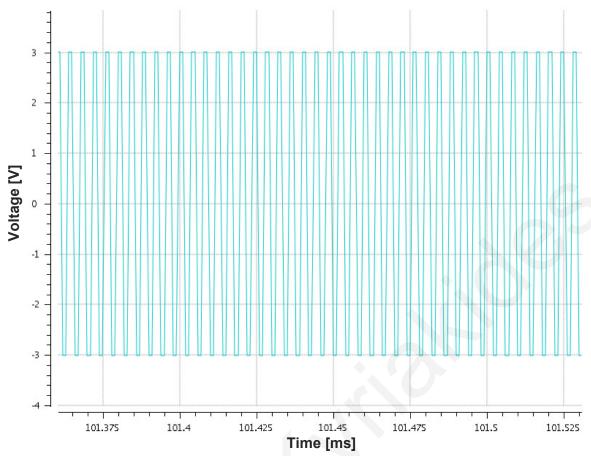

| 5.7  | Oscillator output oscillations with pulse input, visible in higher time resolution.                                                                            |

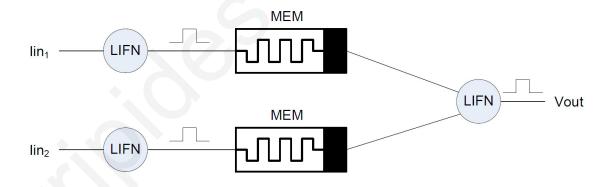

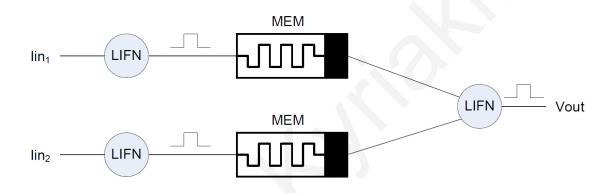

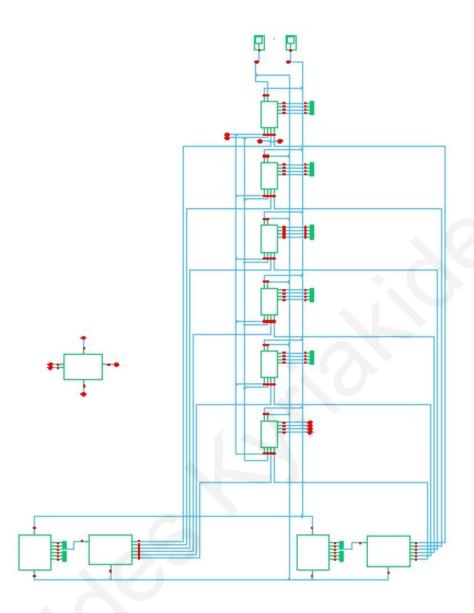

| 5.8  | Block diagram of synaptic plasticity network with two input and one output LIF neurons, connected with two memristors.                                         |

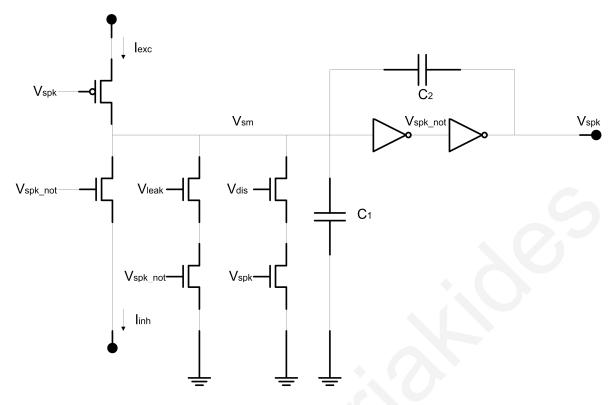

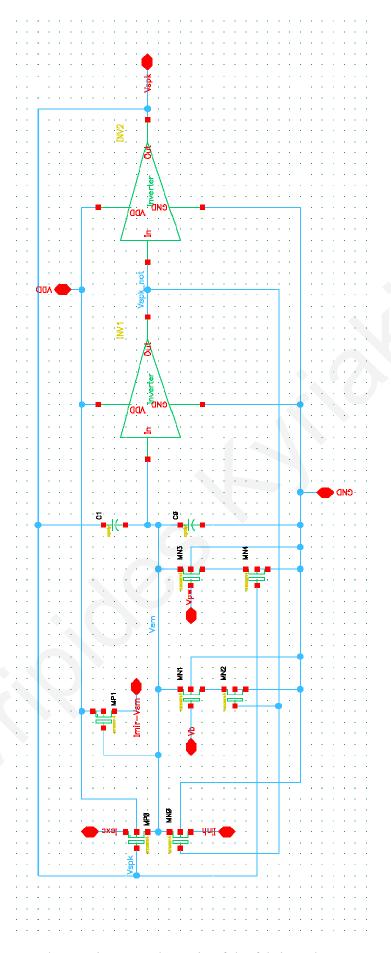

| 5.9  | Schematic of the LIF neuron module.                                                                                                                            |

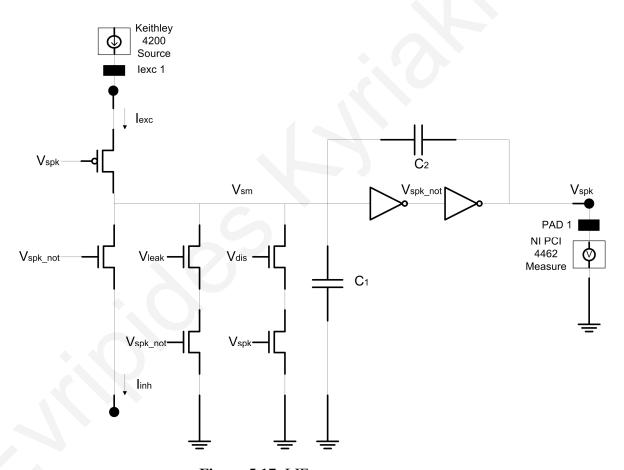

| 5.10 | Simulated traces of internal voltage Vsm (top) and output voltage Vspk (bottom) showing integrate-and-fire functionality of LIF neuron.                        |

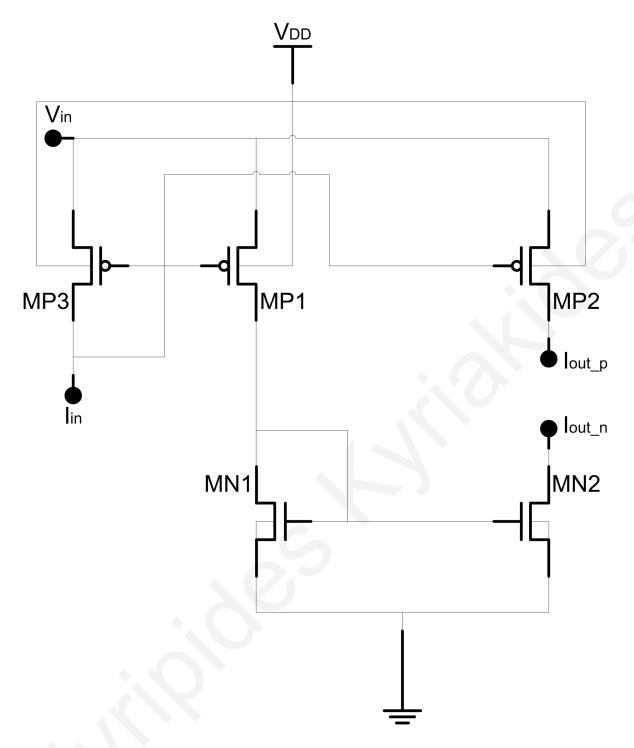

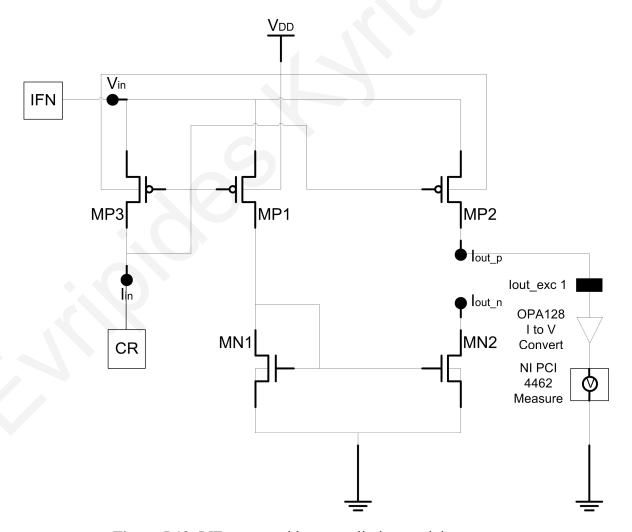

| 5.11 | Schematic of the current limiter module. V <sub>in</sub> represents the input from the previous stage and I <sub>in</sub> the threshold current applied to it. |

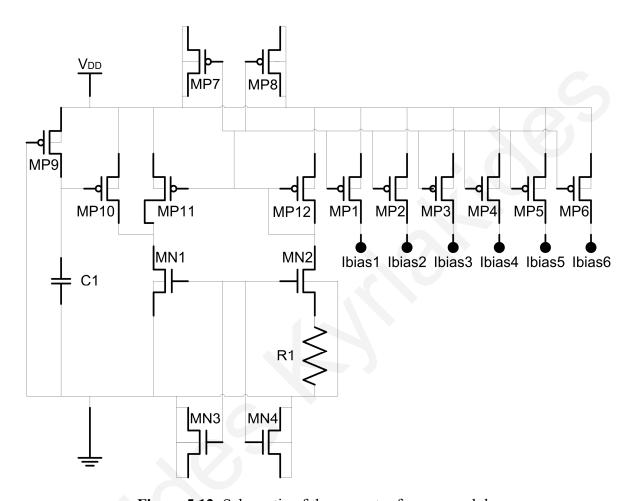

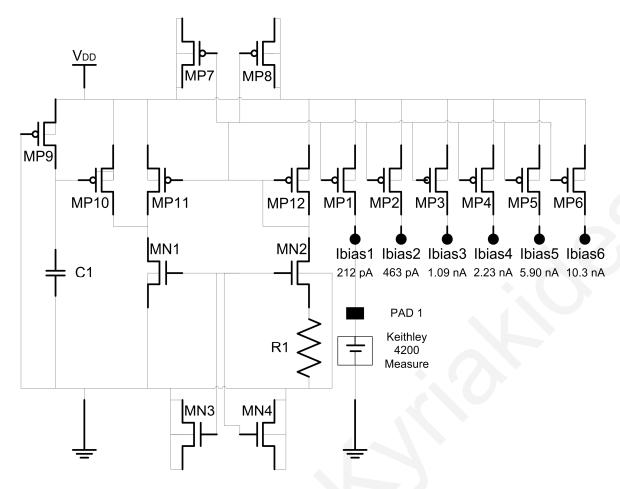

| 5.12 | Schematic of the current reference module.                                                                                                                     |

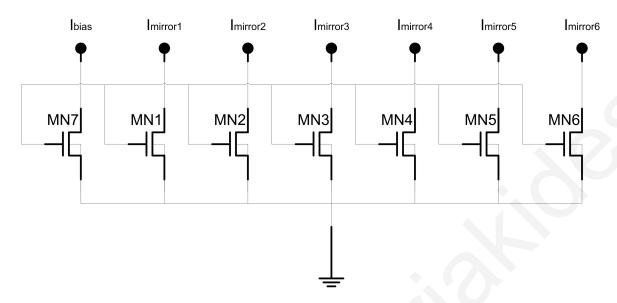

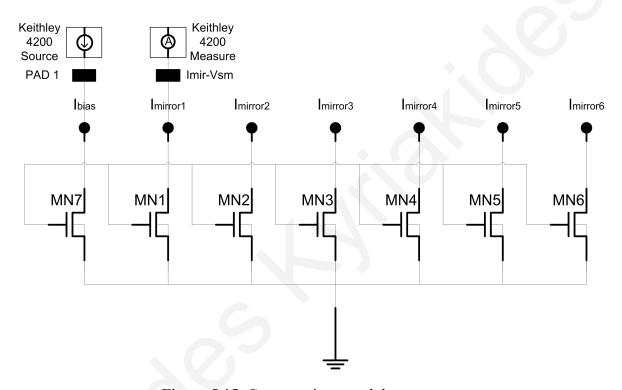

| 5.13 | Schematic of the current mirror module.                                                                                                                        |

| 5.14 | Current reference module test setup.                                                                                                                           |

| 5.15 | Current mirror module test setup.                                                                                                                              |

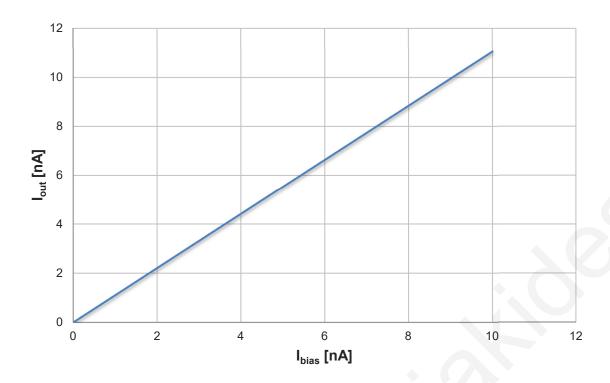

| 5.16 | Current mirror module expected result through simulations.                                                                                                     |

| 5.17 | LIF neuron test setup.                                                                                                                                         |

| 5.18 | Simulated LIF neuron output waveform at 1 nA input current.                                                                                                    |

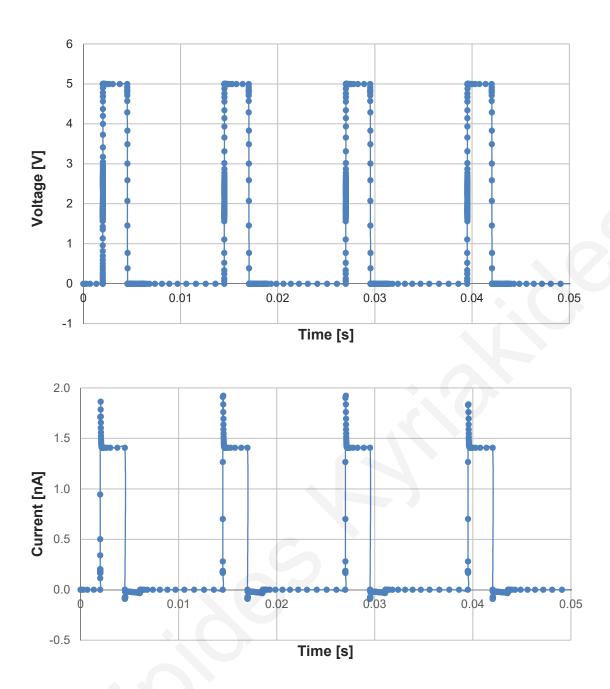

| 5.19 | LIF neuron with current limiter module test setup.                                                                                                             |

| 5.20 | Simulated LIF neuron output voltage (top waveform) and associated current limiter module output current (bottom waveform) showing current limiter operation.   |

| 5.21 | Synaptic plasticity connection diagram.                                                                                                                        |

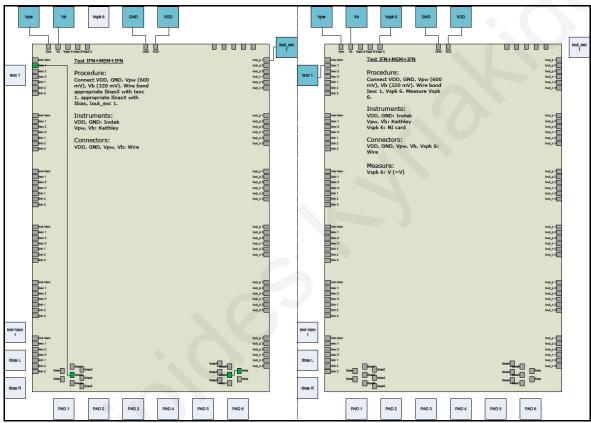

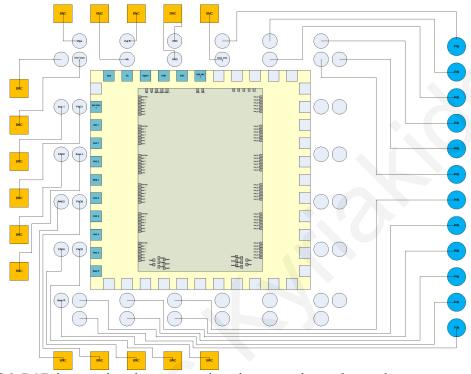

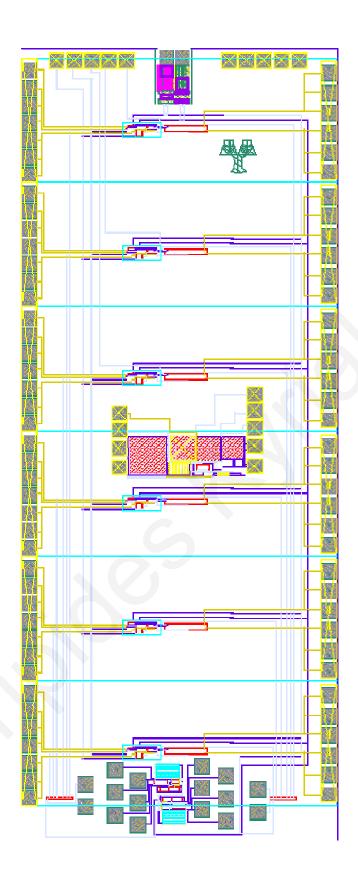

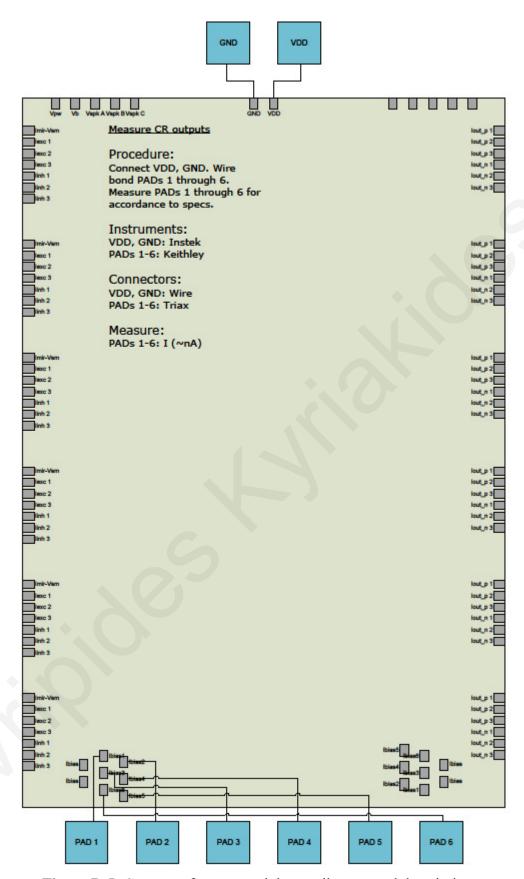

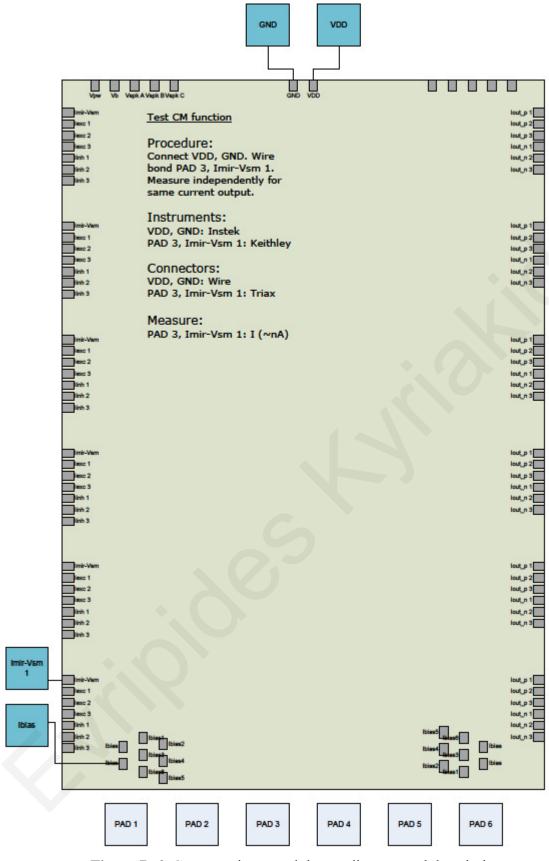

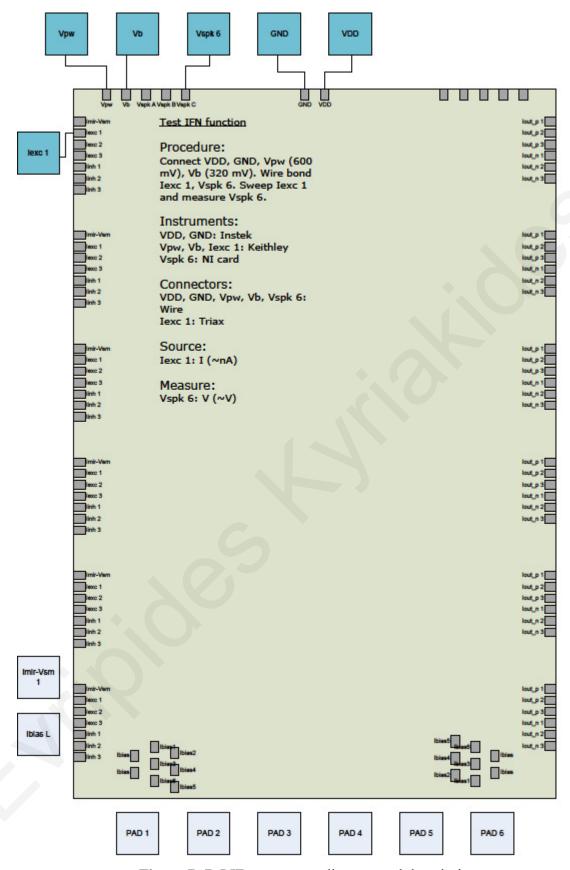

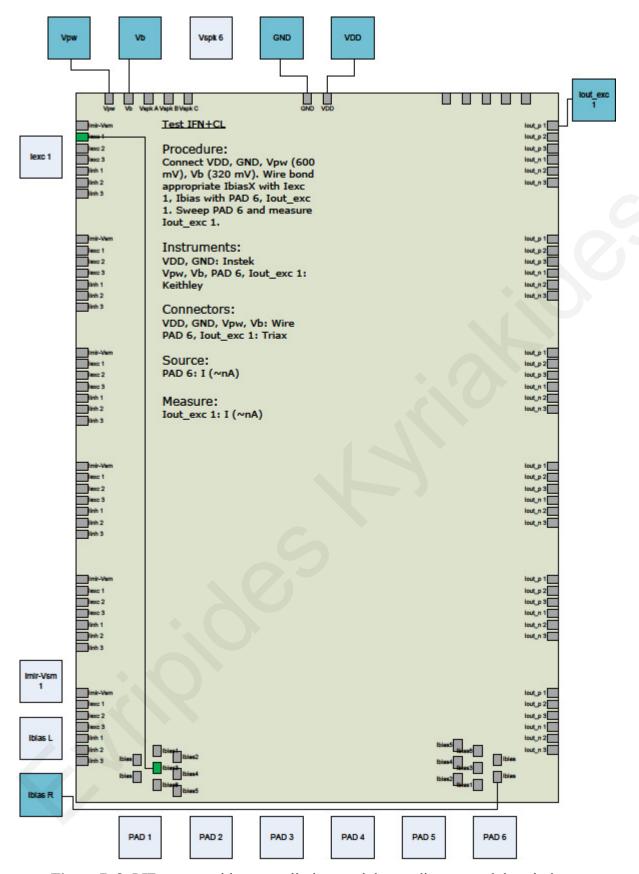

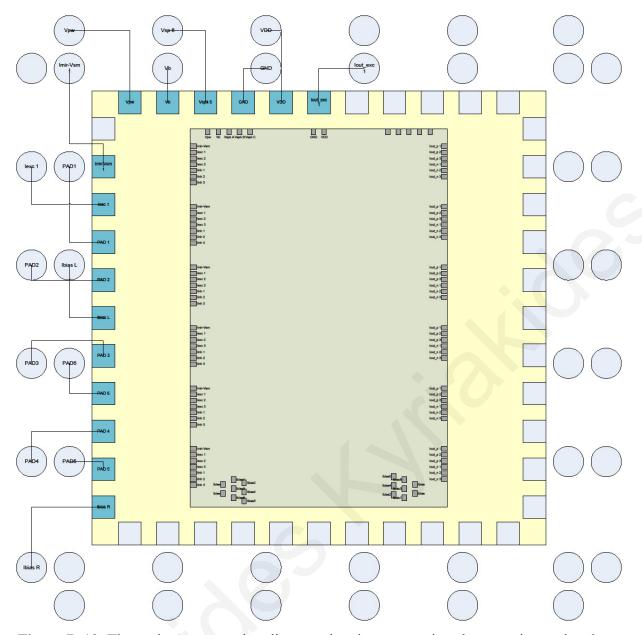

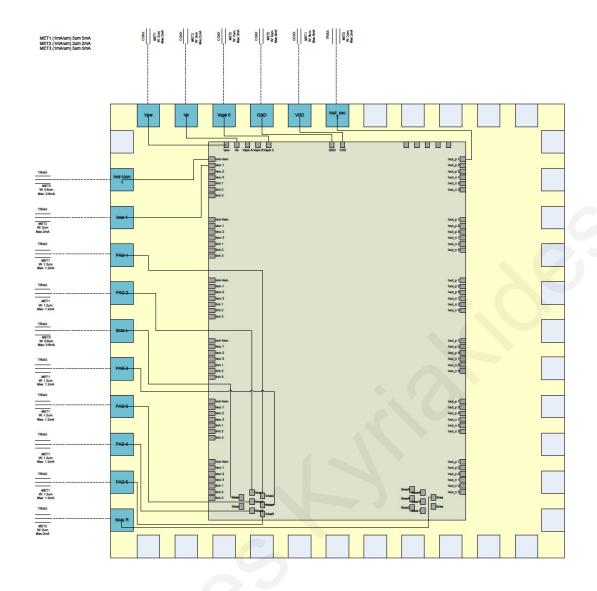

| 5.22 | Network test diagram and description showing connection between input and output neurons. Used pads are shown as green, whereas unused ones are shown as grey. |

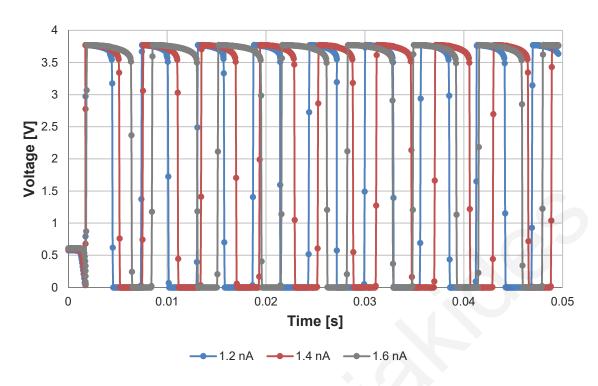

| 5.23 | LIF spiking evolution simulation with increasing excitation current at 1.2 nA, 1.4 nA, and 1.6 nA.                                                             |

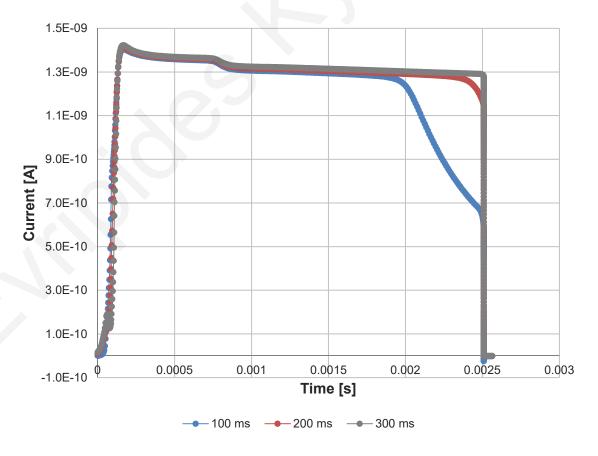

| 5.24 | Gradual potentiation of memristor element. The memristor output is simulated and the spikes after 100 ms, 200 ms, and 300 ms are compared                      |

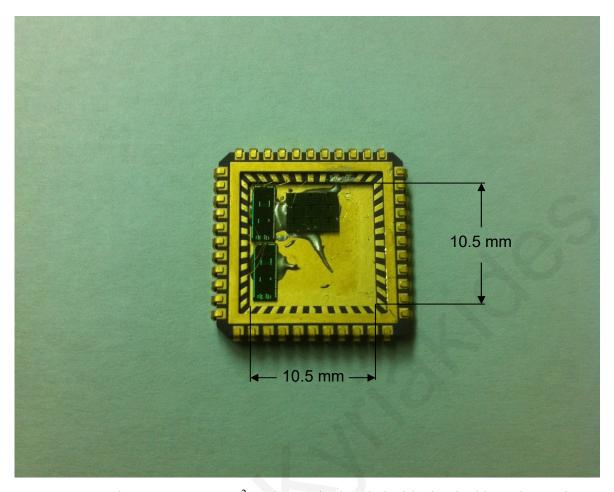

| 5.25 | The $10.5 \times 10.5 \text{ mm}^2$ package wire bonded with circuit chip and memristor dies.                                                                  |

| 5.26 | PCB layout showing connections between the socket and connectors                                                                                               |

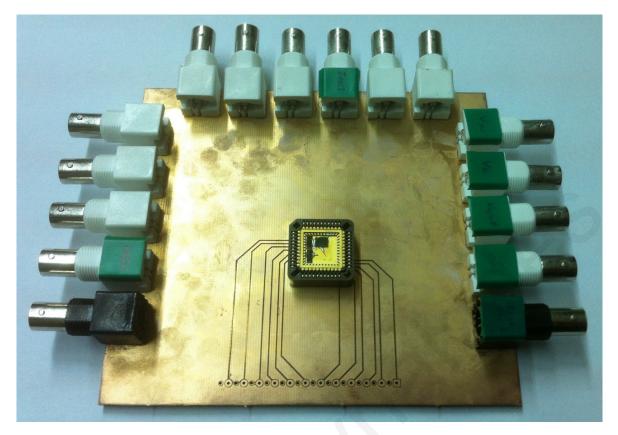

| 5.27 | Complete test setup assembled on the PCB, illustrating the dies wire bonded to the package, the socket attached to the PCB, and the through-hole connectors.   |

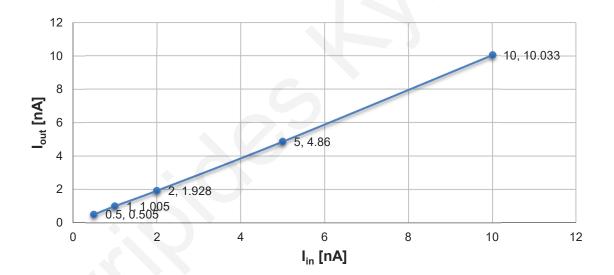

| 5.28 | Current mirror test results. Labels represent I <sub>in</sub> and I <sub>out</sub> values for each data point.                                                 |

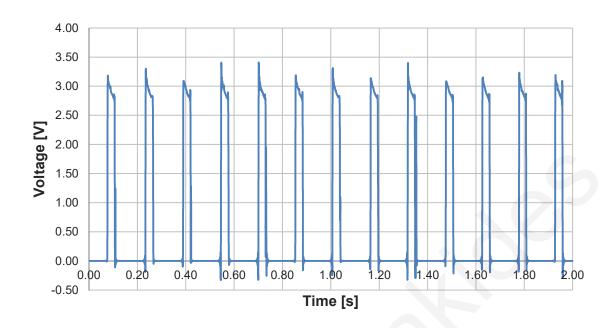

| 5.29 | Measured LIF neuron output.                                                                                                                                    |

| 5.30 | Simulated comparison output of LIF neuron with added junction capacitance.                                                                                     |

| 5.31 | Measured LIF neuron output with current limiter module                                                                                                                                                                         | 205 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

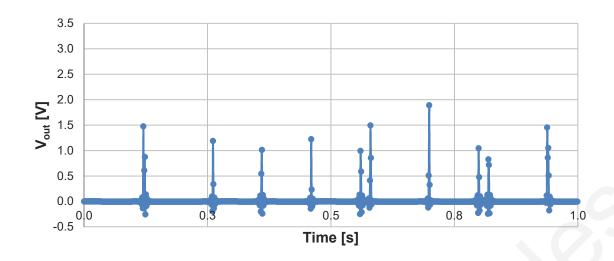

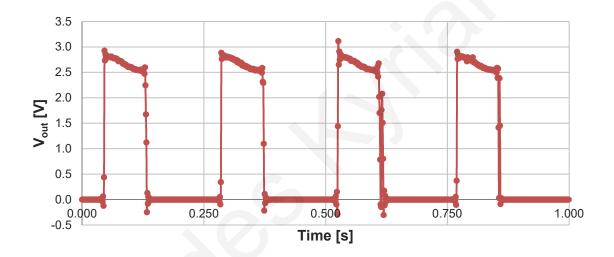

| 5.32 | Spiking pattern measurement of LIF neuron initial output.                                                                                                                                                                      | 206 |

| 5.33 | Spiking pattern measurement of LIF neuron final output.                                                                                                                                                                        | 206 |

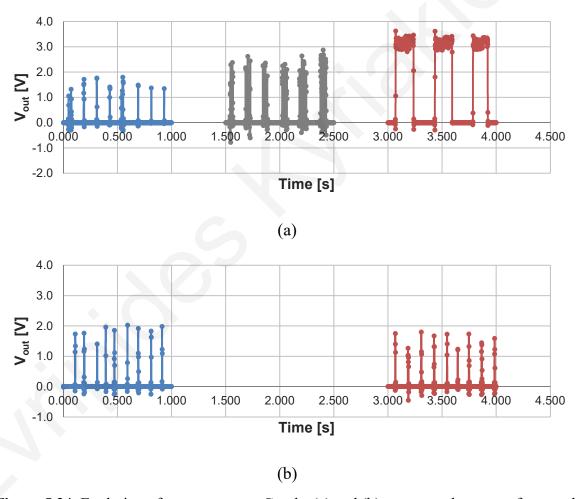

| 5.34 | Evolution of system output. Graphs (a) and (b) represent the output from each input neuron activation. Each output is separated in three sections corresponding from left to right to untrained, training, and trained periods | 207 |

| A.1  | Heidelberg DWL200 optical pattern generator. Adapted from [105]                                                                                                                                                                | 227 |

| A.2  | Centrotherm furnace. Adapted from [105].                                                                                                                                                                                       | 228 |

| A.3  | EVG 150 automatic resist processing cluster. Adapted from [105]                                                                                                                                                                | 228 |

| A.4  | SUSS MicroTec MA150 mask aligner. Adapted from [105]                                                                                                                                                                           | 229 |

| A.5  | Leybold Optics LAB 600 H evaporator. Adapted from [105]                                                                                                                                                                        | 230 |

| A.6  | EVA 600 evaporation system. Adapted from [105]                                                                                                                                                                                 | 231 |

| A.7  | Pfeiffer SPIDER 600 sputtering system. Adapted from [105]                                                                                                                                                                      | 232 |

| A.8  | Plade Solvent wet bench. Adapted from [105].                                                                                                                                                                                   | 233 |

| A.9  | Alcatel AMS 200 etcher. Adapted from [105].                                                                                                                                                                                    | 233 |

| A.10 | FEI Nova 600 Nanolab Dual Beam SEM/FIB. Adapted from [105]                                                                                                                                                                     | 234 |

| A.11 | Typical FIB etching by Nova 600. Adapted from [105].                                                                                                                                                                           | 234 |

| B.1  | The ESPEC SU-261 temperature chamber, shown with a sample loaded for testing, used for controlled heating of the NiTi devices.                                                                                                 | 236 |

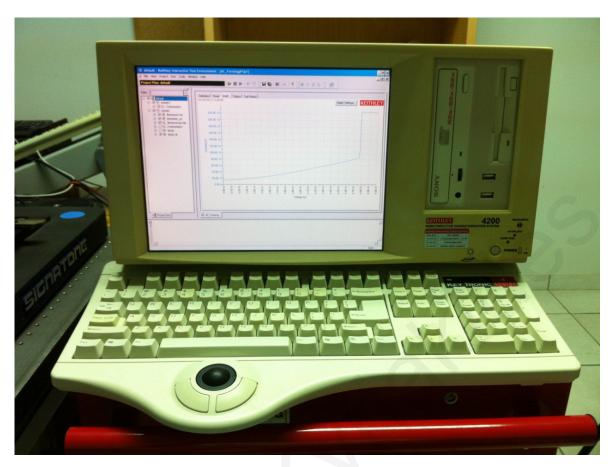

| B.2  | Keithley 4200-SCS Parameter Analyzer for low-level measurements                                                                                                                                                                | 237 |

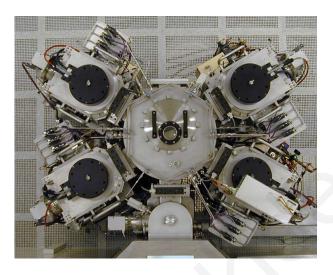

| B.3  | Signatone 1160 Probe Station. Used for characterization of Cu/Ta <sub>2</sub> O <sub>5</sub> devices.                                                                                                                          | 238 |

| B.4  | Board layout of custom-made measurement module.                                                                                                                                                                                | 239 |

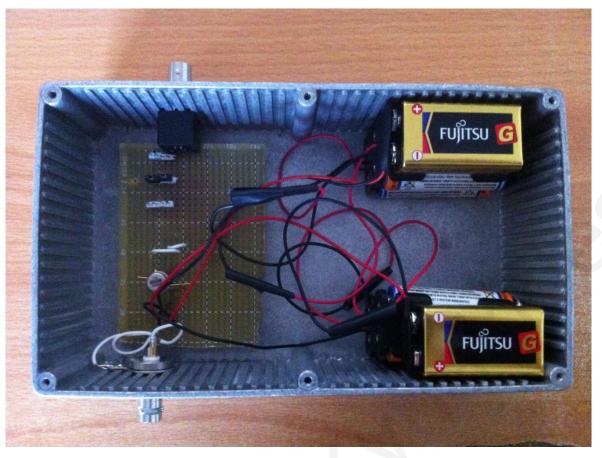

| B.5  | Casing of custom-made measurement module.                                                                                                                                                                                      | 240 |

| B.6  | The NI PCI-4462 acquisition board used for voltage measurements. Adapted from [149].                                                                                                                                           | 241 |

| B.7  | The Keithley 236 SMU used for testing the neuromorphic chip                                                                                                                                                                    | 241 |

| B.8  | The F & K Delvotec 53XX wirebonder used to connect the fabricated chips to a package.                                                                                                                                          | 242 |

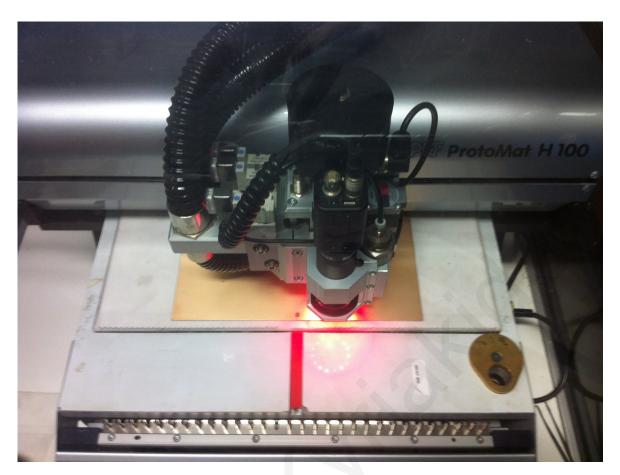

| B.9  | The LPKF ProtoMat H100 PCB system during the PCB milling process                                                                                                                                                               | 243 |

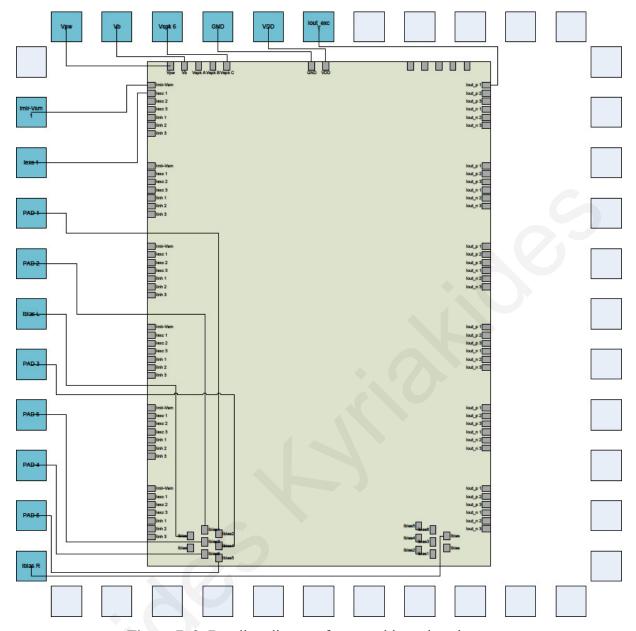

| D.1  | Cadence Virtuoso layout of the fabricated LIF neuron circuit.                                                                                                                                                                  | 251 |

| D.2  | Cadence Virtuoso schematic of the LIF neuron circuit.                                                                                                                                                                          | 252 |