#### THE DATA-DRIVEN MULTITHREADING VIRTUAL MACHINE

Samer Arandi

University of Cyprus, 2011

Since the advent of digital computers, chip designers built faster computers by relying on improvements in fabrication technologies and architectural/organizational optimizations. However, the inability of the sequential model to tolerate long latencies (manifested mainly in the Memory Wall) combined with the Power and Instruction Level Parallelism (ILP) Walls problems eventually rendered this approach ineffective.

The envisaged solution was to switch to multi-core architectures. This switch was an engineering effort that did not address the long memory latencies and the complexity of the designs. In addition, this switch elevated concurrency as a major challenge as it became evident that new concurrent models/paradigms are needed to efficiently utilize the resources of multi-core chips.

The Data-flow model is a formal model that can handle concurrency and tolerate memory and synchronization latencies. Data-Flow systems can also be simpler and thus more power efficient than conventional systems.

In this thesis, we propose re-visiting the Data-flow model and adopting it as the basis for an execution model that efficiently exploits the resources of multi-core architectures. We design and implement a virtual machine supporting the Data-Driven Multithreading (DDM) model of execution, which combines Dynamic Data-Flow concurrency with efficient sequential execution, on multi-core architectures. We refer to this virtual machine as the Data-Driven Multithreading Virtual Machine (DDM-VM). The DDM-VM also supports execution on a cluster of multi-core nodes. We develop a number of alternative approaches facilitating the programming of the DDM-VM, in addition to a number of optimizations for improving the performance.

The evaluation of the DDM-VM for both single nodes and clusters demonstrates that the VM scales well and tolerates latencies and synchronization overheads efficiently, achieving very good performance and outperforming other similar state-of-the-art systems.

The main contribution of this thesis is the design, implementation and optimization of a virtual machine that efficiently exploits data-flow concurrency on commercial multi-cores and delivers high-performance comparing favorably with similar systems. The rest of this thesis contributions are:

• The development of the DDM-VM, an efficient virtual machine that supports DDM execution on multi-core architectures. It utilizes Data-Flow concurrency for scheduling threads and efficient sequential execution within a thread, while optimizing the context management of the Dynamic Data-Flow tagging system. The virtual machine has two individually optimized implementations: The DDM-VM<sub>s</sub> tailored for homogeneous multi-cores and the DDM-VM<sub>c</sub> tailored for heterogeneous multi-cores. The latter is developed for heterogeneous multi-core architectures with a host/accelerator organization and a software-managed memory hierarchy. The DDM-VM<sub>c</sub> is also a high-performance implementation of DDM. When comparing its performance with two similar state-of-the-art systems using a number of computationally-intensive benchmarks, the DDM-VM<sub>c</sub> outperforms both systems and achieves 88% of the theoretical peak performance for one of the benchmarks. For the same benchmark the DDM-VM<sub>c</sub> execution on a cluster of 4 machines achieves 0.44 TFLOPs.

- The development of a fully-automated software prefetching cache with variable cache block sizes and explicit data locality optimizations for handling explicitly-managed memory hierarchies.

- The development of the support for distributed DDM execution. The DDM-VM is the first DDM implementation supporting distributed DDM execution across a cluster of multi-core nodes.

- The development of the support for runtime dependency resolution using specialized I-Structures. The DDM-VM is the first DDM implementation that supports parallel execution of code that contains producer-consumer dependencies that are only resolved at runtime while utilizing compile-time resolution at the same time. This permits taking advantage of the strengths of both approaches and expands the class of programs that can be mapped to the DDM model. It also has the potential to improve the programmability and enhance the yield of compilation methods generating data-flow code.

- The development of a number of performance optimizations and monitoring & visualization tools.

### THE DATA-DRIVEN MULTITHREADING VIRTUAL MACHINE

Samer Arandi

A Doctor of Philosophy Dissertation

Submitted in Partial Fulfillment of the

Requirements for the Degree of

Doctor of Philosophy

at the

University of Cyprus

Recommended for Acceptance

by the Department of Computer Science

November, 2011

© Copyright by

Samer Arandi

All Rights Reserved

2011

## **APPROVAL PAGE**

Doctor of Philosophy Dissertation

### THE DATA-DRIVEN MULTITHREADING VIRTUAL MACHINE

Presented by

Samer Arandi

| Research Supervisor |                                |

|---------------------|--------------------------------|

|                     | Professor Paraskevas Evripidou |

| Committee Chair     |                                |

|                     | Dr. Pedro Trancoso             |

| Committee Member    |                                |

|                     | Professor Ian Watson           |

| Committee Member    |                                |

|                     | Dr. Yiannakis Sazeides         |

| Committee Member    |                                |

|                     | Dr. Costas Kyriacou            |

|                     | University of Cyprus           |

November, 2011

### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my advisor Professor Skevos Evripidou for his continuous support for me both personally and professionally. I am grateful for his patience, guidance and immense knowledge and experience. He has taught me various valuable things through out the period of my studies and made sure I am always on the right track with his deep intuitions and infallible advice. It was a privilege and a pleasure having him as my advisor.

I would also like to warmly thank Dr. Pedro Trancoso for his invaluable help and support since the first day of my studies. Thanks for the sincere encouragement, inspiring opinions and insightful discussions.

It is a pleasure to extend my gratitude to the rest of the committee members: Professor Ian Watson, Dr Yannakis Sazeides and Dr. Costas Kyriacou for their encouragement and insightful comments.

I would also like to thank all my colleagues whom I had the pleasure to work and collaborate with: Thank you George Michael, Andreas Diavastos, Petros Panayi and Kyriacos Stavrou.

I gratefully acknowledge the financial support of the Cyprus Research Promotion Foundation which made my Ph.D. work possible.

There are so many people whose support and friendship I have enjoyed during the course of my Ph.D. I would like to sincerely thank my friends: Sandy Ayas, George Michael, Maria Efthemio, Maria Charalambous, Nuno Martins, Petros Panagyi and Kyriacos Stavrou. Thanks for helping me during my stay in Cyprus and for making my time here a very enjoyable one. Last but not least, I would like to thank my family. My parents: Dr. Najeh Arandi and Samar Arandi for their unconditional love, support and -most importantly- patience, during the past 5 years and for all that they did for me throughout my life, which I cannot reward them back for, no matter what I do or how hard I try. Whatever I am today, its because of them. I would also like to thank my younger brother and sister Ayman and Samah for their love and encouragement and my little nieces Gazal and Masa for all the happiness they brought into our lives.

# **TABLE OF CONTENTS**

| Chapter    | 1:                                                             | Introduction                                                                                                                                                               | 1                                                                                              |

|------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 1.1        | Introdu                                                        | action                                                                                                                                                                     | 1                                                                                              |

| 1.2        | Motiva                                                         | tion                                                                                                                                                                       | 2                                                                                              |

| 1.3        | Proble                                                         | m Statement - Hypothesis                                                                                                                                                   | 4                                                                                              |

| 1.4        |                                                                | ach                                                                                                                                                                        | 4                                                                                              |

| 1.5        | Thesis                                                         | Contributions                                                                                                                                                              | 5                                                                                              |

| 1.6        | Perform                                                        | mance Evaluation                                                                                                                                                           | 7                                                                                              |

|            | 1.6.1                                                          | Methodology                                                                                                                                                                | 7                                                                                              |

|            | 1.6.2                                                          | Results                                                                                                                                                                    | 8                                                                                              |

| 1.7        | Thesis                                                         | Outline                                                                                                                                                                    | 15                                                                                             |

|            | _                                                              |                                                                                                                                                                            |                                                                                                |

| Chapter    | 2:                                                             | Background and Related Work                                                                                                                                                | 16                                                                                             |

|            |                                                                |                                                                                                                                                                            |                                                                                                |

| 2.1        | Introdu                                                        | uction                                                                                                                                                                     | 16                                                                                             |

| 2.1<br>2.2 |                                                                | round Information                                                                                                                                                          |                                                                                                |

|            |                                                                |                                                                                                                                                                            | 17                                                                                             |

|            | Backg                                                          | round Information                                                                                                                                                          | 17<br>17                                                                                       |

|            | Backgr<br>2.2.1<br>2.2.2                                       | round Information                                                                                                                                                          | 17<br>17<br>27                                                                                 |

| 2.2        | Backgr<br>2.2.1<br>2.2.2                                       | round Information          From Monolithic to Multi-core Architectures          Data-flow Architectures                                                                    | 17<br>17<br>27                                                                                 |

| 2.2        | Backgr<br>2.2.1<br>2.2.2<br>Related                            | round Information   From Monolithic to Multi-core Architectures   Data-flow Architectures   d Work                                                                         | 17<br>17<br>27<br>35                                                                           |

| 2.2        | Backgr<br>2.2.1<br>2.2.2<br>Related<br>2.3.1                   | round Information   From Monolithic to Multi-core Architectures   Data-flow Architectures   d Work   Threaded Abstract Machine (TAM)                                       | 17<br>17<br>27<br>35<br>35                                                                     |

| 2.2        | Backgr<br>2.2.1<br>2.2.2<br>Related<br>2.3.1<br>2.3.2          | round Information   From Monolithic to Multi-core Architectures   Data-flow Architectures   d Work   Threaded Abstract Machine (TAM)   Star Superscalar (StarSs)           | <ol> <li>17</li> <li>17</li> <li>27</li> <li>35</li> <li>35</li> <li>36</li> <li>36</li> </ol> |

| 2.2        | Backgr<br>2.2.1<br>2.2.2<br>Related<br>2.3.1<br>2.3.2<br>2.3.3 | round Information   From Monolithic to Multi-core Architectures   Data-flow Architectures   d Work   Threaded Abstract Machine (TAM)   Star Superscalar (StarSs)   Sequoia | <ol> <li>17</li> <li>17</li> <li>27</li> <li>35</li> <li>35</li> <li>36</li> <li>36</li> </ol> |

|         | 2.3.7   | Intel Threading Building Blocks (TBB)                                                              | 40 |

|---------|---------|----------------------------------------------------------------------------------------------------|----|

|         | 2.3.8   | Streaming Platforms                                                                                | 40 |

|         | 2.3.9   | Software Caches on the Cell                                                                        | 40 |

|         | 2.3.10  | Self-Distributing Virtual Machine (SDVM)                                                           | 42 |

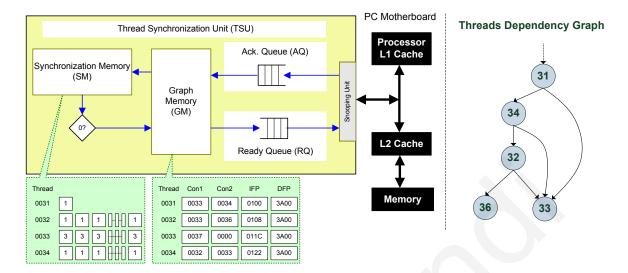

| 2.4     | Data-D  | Driven Multithreading                                                                              | 44 |

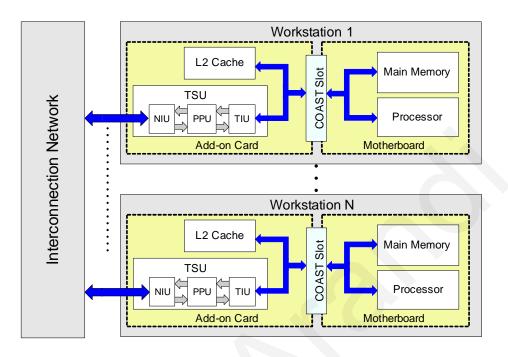

|         | 2.4.1   | The Data-Driven Network of Workstations                                                            | 46 |

|         | 2.4.2   | Thread Flux                                                                                        | 49 |

|         | 2.4.3   | The Data-Driven Multithreading Virtual Machine                                                     | 52 |

| Chapter | • 3:    | The Data-Driven Multithreading Virtual Machine (DDM-VM)                                            | 54 |

| 3.1     | Introdu | action                                                                                             | 54 |

| 3.2     | The Da  | ata-Driven Multithreading Virtual Machine (DDM-VM)                                                 | 55 |

| 3.3     | The Da  | ata-Driven Virtual Machine for the Cell (DDM-VM <sub>c</sub> ) $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 58 |

|         | 3.3.1   | Motivation and Design Rationale                                                                    | 60 |

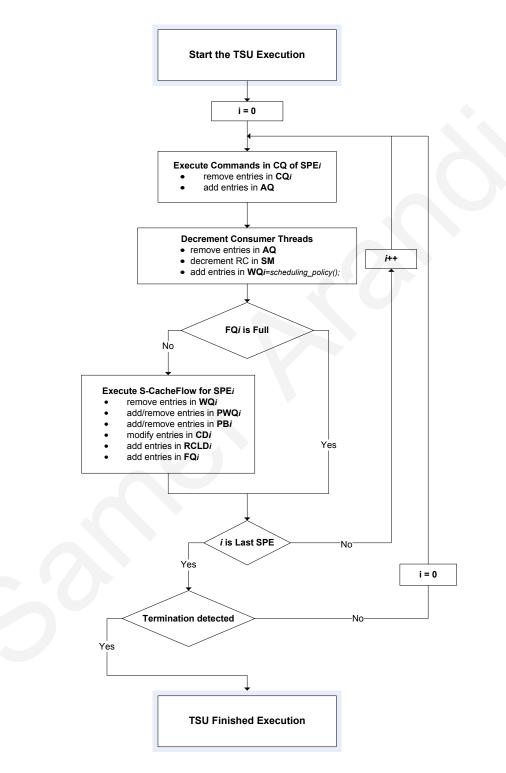

|         | 3.3.2   | The Thread Scheduling Unit (TSU)                                                                   | 62 |

|         | 3.3.3   | The TSU-Processor Interface                                                                        | 66 |

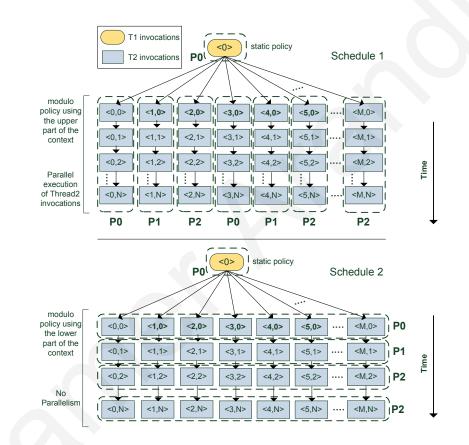

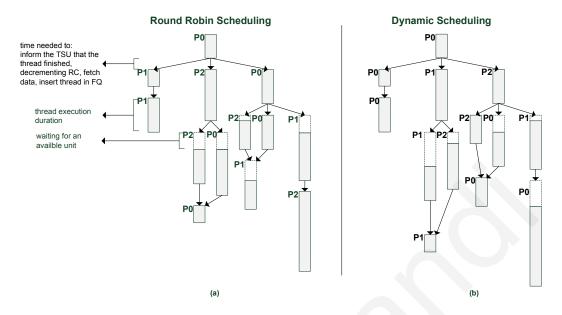

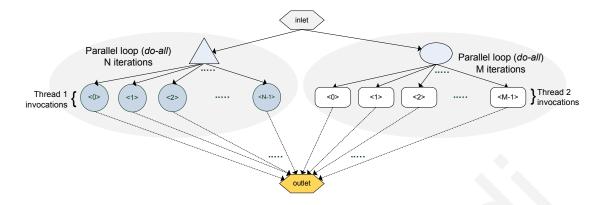

|         | 3.3.4   | The Scheduling Policy                                                                              | 69 |

|         | 3.3.5   | Execution Termination                                                                              | 74 |

| 3.4     | Softwa  | are CacheFlow (S-CacheFlow)                                                                        | 77 |

|         | 3.4.1   | S-CacheFlow Structures                                                                             | 78 |

|         | 3.4.2   | S-CacheFlow Operations                                                                             | 80 |

|         | 3.4.3   | Allocation and Eviction                                                                            | 84 |

|         | 3.4.4   | Exploiting Data Locality                                                                           | 86 |

|         | 3.4.5   | Distributed CacheFlow                                                                              | 93 |

|         | 3.4.6             | Adaptive Multi-buffering/Prefetching                                      | 95  |

|---------|-------------------|---------------------------------------------------------------------------|-----|

| 3.5     | The Da            | ata-Driven Multithreading Virtual Machine for Symmetric Multi-cores (DDM- |     |

|         | VM <sub>s</sub> ) |                                                                           | 99  |

|         | 3.5.1             | The Thread Scheduling Unit (TSU)                                          | 100 |

|         | 3.5.2             | TSU-Processor Interface                                                   | 103 |

|         | 3.5.3             | Handling concurrent access of the TSU structures                          | 103 |

| Chapter | 4:                | Distributed Data-Driven Execution                                         | 105 |

| 4.1     | Overvi            | iew                                                                       | 107 |

| 4.2     | The D             | istributed Thread Scheduling Unit (TSU)                                   | 108 |

|         | 4.2.1             | The TSU Structures                                                        | 108 |

|         | 4.2.2             | The TSU Operations                                                        | 109 |

|         | 4.2.3             | The Network Interface Unit (NIU)                                          | 109 |

| 4.3     | The M             | lemory Address Space and the Program Data                                 | 114 |

|         | 4.3.1             | Data Forwarding and CacheFlow Operations                                  | 116 |

| 4.4     | Distrib           | outed Execution Termination                                               | 119 |

|         | 4.4.1             | Explicit Termination Approach                                             | 120 |

|         | 4.4.2             | Implicit Termination Approach                                             | 120 |

| Chapter | 5:                | Programming Methodology and Optimizations                                 | 125 |

| 5.1     | Introdu           | uction                                                                    | 125 |

| 5.2     | Dynan             | nic Data-flow                                                             | 125 |

| 5.3     | Data-I            | Driven Multithreading (DDM)                                               | 126 |

| 5.4     | DDM-              | VM Programming Methodology                                                | 130 |

|         | 5.4.1             | The Low-Level Interface: DDM-VM Macros                                    | 132 |

|         | 5.4.2   | Identifying the Boundaries of DDM Threads    | . 134 |

|---------|---------|----------------------------------------------|-------|

|         | 5.4.3   | DDM Dependency Graph and Context Maintenance | . 135 |

|         | 5.4.4   | DDM Dependency Graph Creation and Execution  | . 136 |

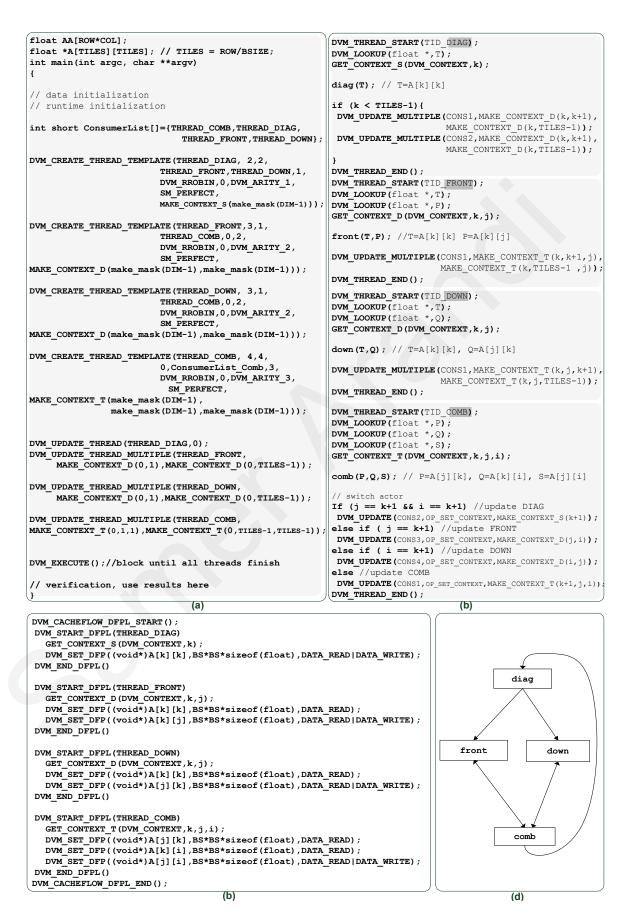

|         | 5.4.5   | Programming Example - LU Decomposition       | . 140 |

| 5.5     | Suppor  | orting Distributed DDM Execution             | . 148 |

|         | 5.5.1   | DDM-VM Macros                                | 148   |

|         | 5.5.2   | Data Distribution                            | 148   |

|         | 5.5.3   | LU Decomposition - Distributed Version       |       |

| 5.6     | DDM-    | -VM Optimizations                            | 156   |

|         | 5.6.1   | Consumer Updating Optimizations              | . 156 |

|         | 5.6.2   | Eliminating Redundant Dependencies           | . 160 |

|         | 5.6.3   | Resource Management                          | 162   |

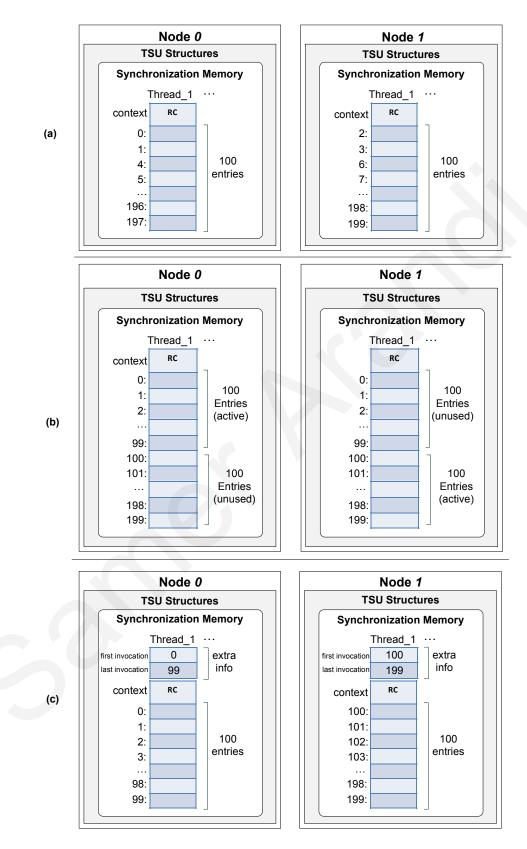

|         | 5.6.4   | Synchronization Memory Organization          | . 164 |

| 5.7     | T-Flux  | Directives                                   | 169   |

| 5.8     | GCC A   | Auto-Parallelization                         | 170   |

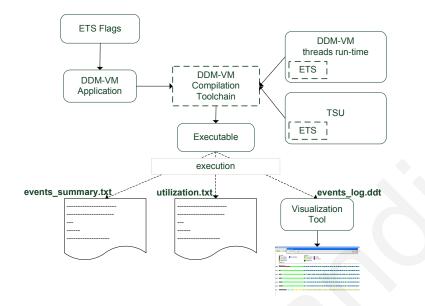

| 5.9     | Monito  | oring and Visualization Tools                | 175   |

| Chapter | · 6:    | Runtime Dependency Resolution                | 179   |

|         |         |                                              |       |

| 6.1     | Introdu | uction                                       | . 179 |

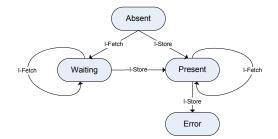

| 6.2     | I-Struc | ctures                                       | . 179 |

| 6.3     | Run-ti  | me Dependency Resolution with I-Structures   | . 180 |

| 6.4     | Examp   | ple                                          | 182   |

| 6.5     | The I-  | Structure Implementation                     | 183   |

| 6.6     | Hopse   | otch Hashing algorithm                       | 184   |

| 6.7      | Discus  | sion                                                   | 185 |

|----------|---------|--------------------------------------------------------|-----|

| Chapter  | 7:      | Evaluation                                             | 187 |

| 7.1      | Introdu | iction                                                 | 187 |

| 7.2      | The DI  | DM-VM <sub><math>c</math></sub> Evaluation             | 187 |

|          | 7.2.1   | Experimental Setup                                     | 188 |

|          | 7.2.2   | Optimizations Evaluation                               | 190 |

|          | 7.2.3   | General Performance Evaluation                         | 194 |

|          | 7.2.4   | Problem Size                                           | 200 |

|          | 7.2.5   | Distributed DDM-VM <sub>c</sub> Execution              | 204 |

| 7.3      | The DI  | $DM-VM_s$ Evaluation                                   | 207 |

|          | 7.3.1   | Thread Granularity                                     | 209 |

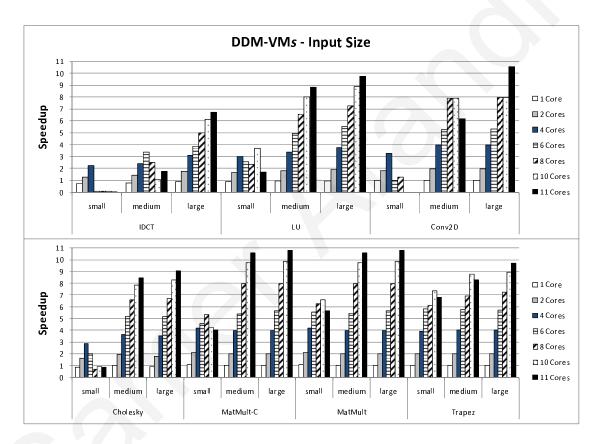

|          | 7.3.2   | Input Size                                             | 209 |

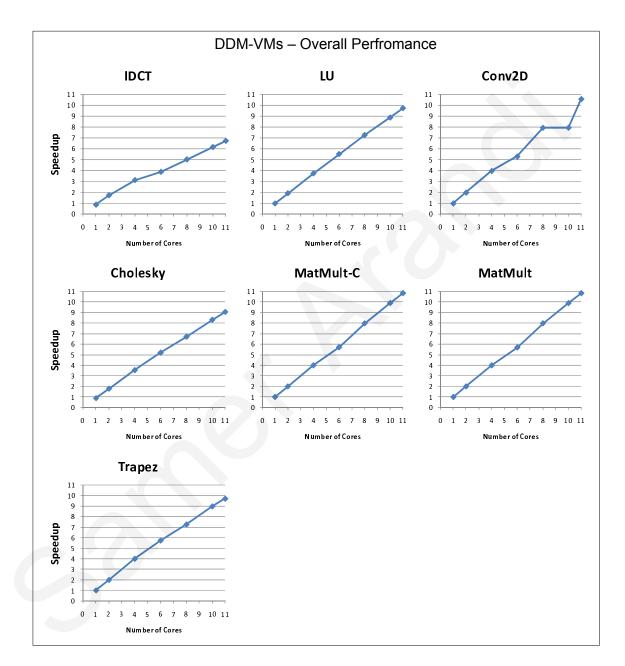

|          | 7.3.3   | Overall Performance                                    | 209 |

|          | 7.3.4   | Runtime Dependency Resolution                          | 210 |

|          | 7.3.5   | Distributed DDM-VM <sub>s</sub> Execution              | 215 |

| Chanton  | 0.      | Future Work and Conclusion                             | 220 |

| Chapter  |         |                                                        |     |

| 8.1      | Future  | Work                                                   | 220 |

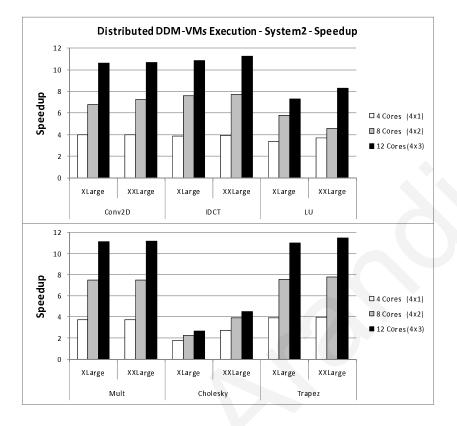

|          | 8.1.1   | Concurrent Collections Source-to-Source Compiler       | 220 |

|          | 8.1.2   | Supporting Dynamic Scheduling in Distributed Execution | 223 |

|          | 8.1.3   | Supporting Prefetching on the DDM-VM <sub>s</sub>      | 225 |

| 8.2      | Conclu  | ision                                                  | 226 |

| Bibliogr | aphy    |                                                        | 229 |

### ix

## Appendices

| Appendix A: | Distributed Data Management Runtime Calls | 239   |

|-------------|-------------------------------------------|-------|

| Appendix B: | TFlux Directives                          | 241   |

| Appendix C: | Monitoring and Visualization Tools        | 245   |

| C.1 DDM     | Execution Events                          | . 245 |

| C.1.1 Opt   | imizations                                | . 250 |

| C.2 TSU S   | Structures Utilization and Statistics     | . 250 |

| C.3 Suppo   | rting Distributed DDM Execution           | . 252 |

239

# LIST OF TABLES

| 1 | The DDM-VM Macros                                                                                                                                    |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | DDM-VM I-Structure Macros                                                                                                                            |

| 3 | The benchmarks suite characteristics - DDM-VM <sub>c</sub> $\ldots \ldots 189$ |

| 4 | The benchmarks suite characteristics - DDM-VM <sub>s</sub> $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 208$                      |

| 5 | Distributed DDM-VM <sub>s</sub> Execution Results - Summary                                                                                          |

| 6 | The TSU Events                                                                                                                                       |

| 7 | Thread Execution Events                                                                                                                              |

| 8 | DDM Trace File Format                                                                                                                                |

# LIST OF FIGURES

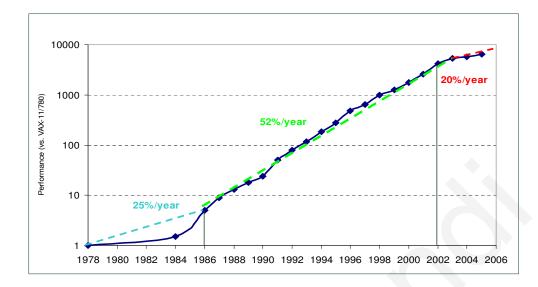

| 1  | Growth in processor performance since the mid-1980 relative to the VAX 11/780    |    |

|----|----------------------------------------------------------------------------------|----|

|    | measured by the SPEC<br>int benchmark (Figure from Hennessy & Patterson [93])    | 2  |

| 2  | A five-stage pipeline with ideal execution of seven instructions                 | 18 |

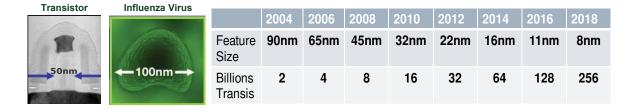

| 3  | A comparison between the sizes of a 50nm transistor and the Influenza virus.     |    |

|    | Table on the right shows the number of transistors available/predicted on a chip |    |

|    | up to 2018 (information from Intel).                                             | 21 |

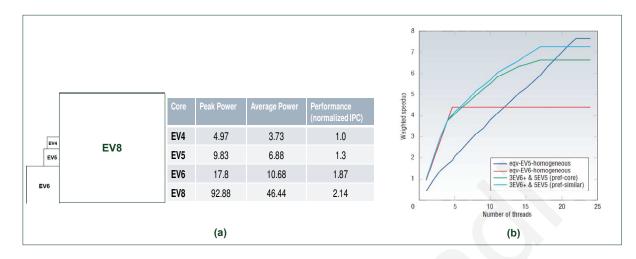

| 4  | (a) Area and Power comparison for four generations of the alpha processor (b)    |    |

|    | Performance comparisons for a number of heterogeneous & homogeneous config-      |    |

|    | urations (figure and data from [69])                                             | 23 |

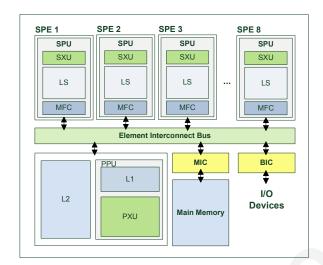

| 5  | The Cell Processor Architecture                                                  | 24 |

| 6  | Different multithreading approaches (a) Blocked Multithreading (b) Interleaved   |    |

|    | Multithreading (c) Simultaneous Multithreading (SMT)                             | 30 |

| 7  | DDM Node                                                                         | 45 |

| 8  | The D <sup>2</sup> NOW Architecture (Figure from[71])                            | 47 |

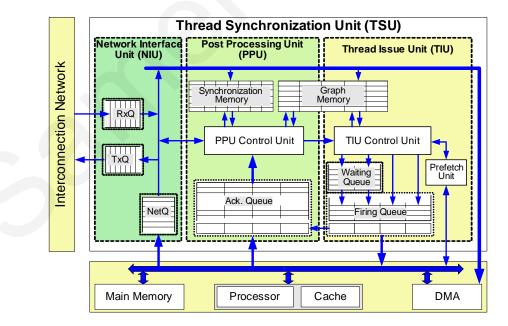

| 9  | The TSU internal structure (Figure from [71])                                    | 47 |

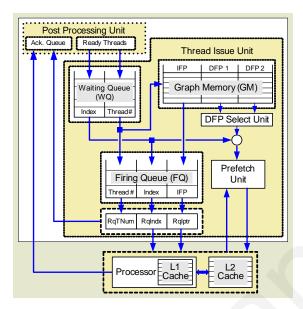

| 10 | The TSU with the basic prefetch CacheFlow policy (Figure from [71])              | 48 |

| 11 | The TFlux Platform (Figure from [113])                                           | 49 |

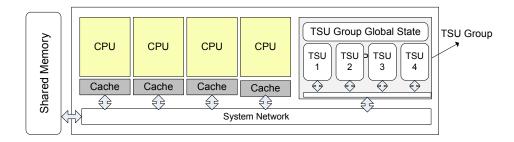

| 12 | TFluxHard chip with 4 cores (Figure from [113])                                  | 51 |

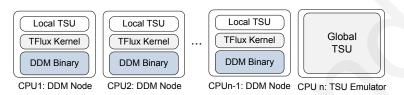

| 13 | TFluxSoft system executing on a system with n CPUs (Figure from [113])           | 51 |

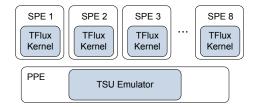

| 14 | The TFluxCell system (Figure from [113])                                         | 52 |

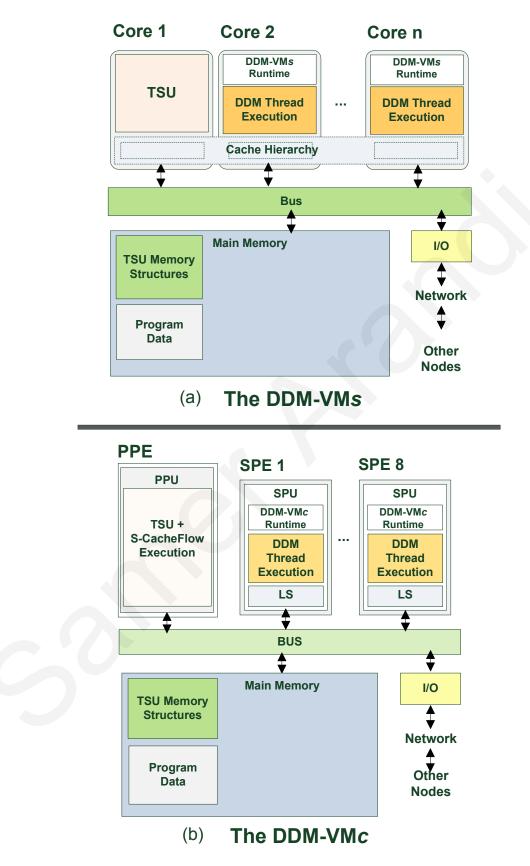

| 15 | The two implementations of the DDM-VM architecture (a) DDM-VM $_s$ (b) DDM-      |    |

|    | VM <sub>c</sub>                                                                  | 57 |

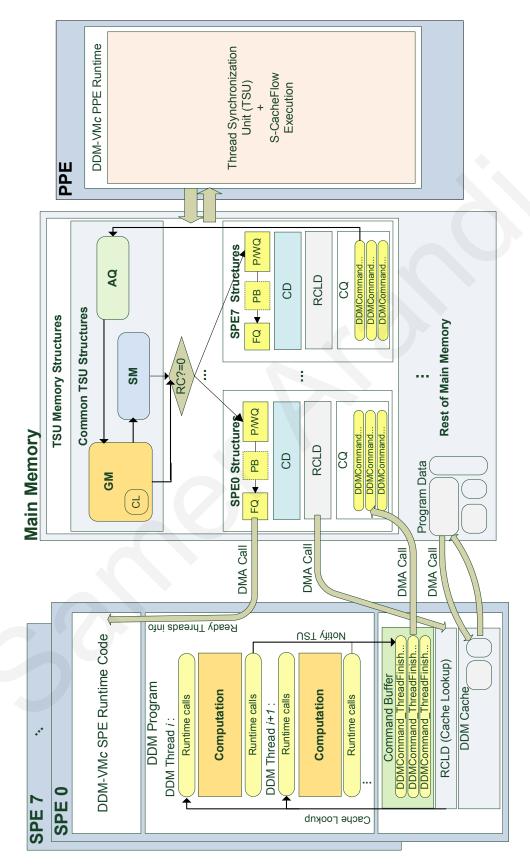

| 16 | The Architecture of the DDM-VM $_c$                                                                                                                                    |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

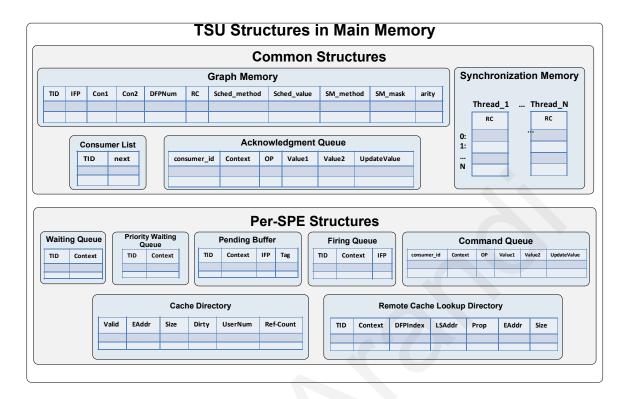

| 17 | The TSU Structures in Main Memory                                                                                                                                      |

| 18 | DDM-VM <sub>c</sub> TSU Activities                                                                                                                                     |

| 19 | Two schedules using the static and modulo policies differently with a drastic ef-                                                                                      |

|    | fects on parallelism                                                                                                                                                   |

| 20 | RoundRobin and Dynamic Scheduling Policies                                                                                                                             |

| 21 | DDM program of two parallel loops with inlet & outlet threads                                                                                                          |

| 22 | S-CacheFlow Allocation Example: the contents of the Remote Cache Lookup                                                                                                |

|    | Directory (RCLD) & the Cache Directory (CD)                                                                                                                            |

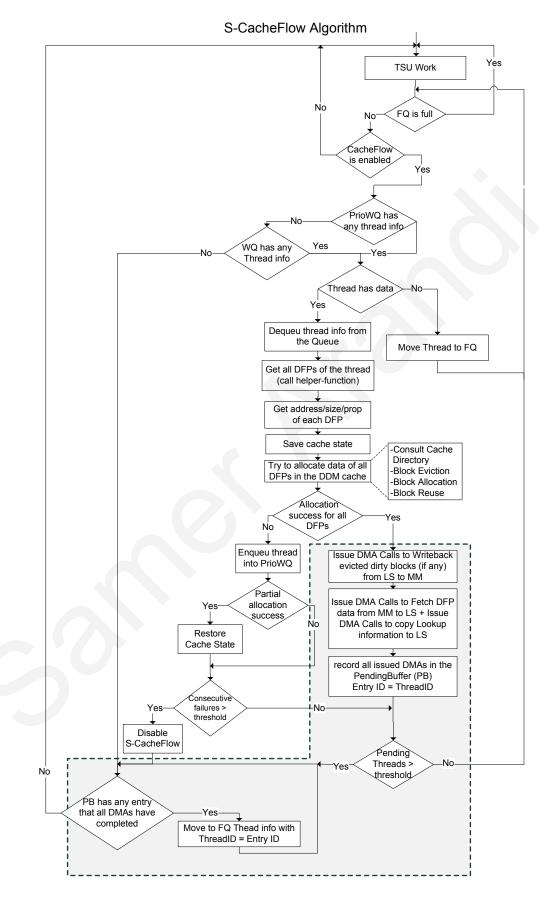

| 23 | S-CacheFlow Algorithm - Pre-Thread Operations (shaded parts are executed on                                                                                            |

|    | the SPE in the Distributed S-CacheFlow implementation)                                                                                                                 |

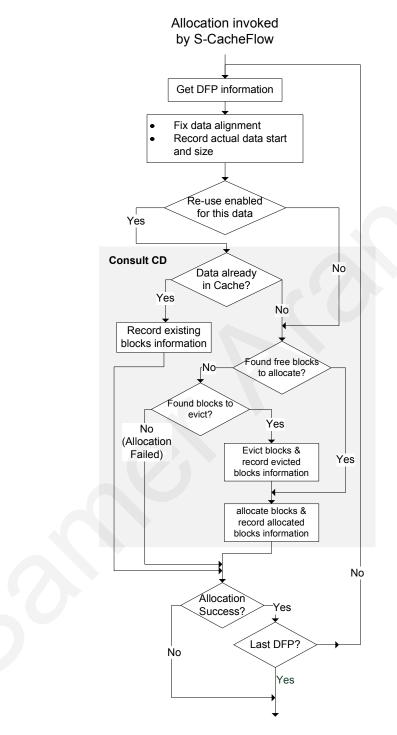

| 24 | Allocation and eviction in the S-CacheFlow algorithm)                                                                                                                  |

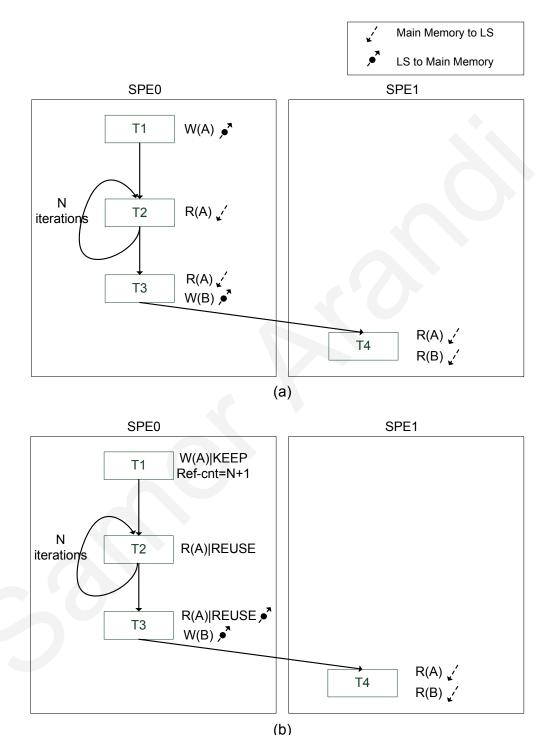

| 25 | An Example of a DDM-VM program Utilizing Locality. (a) no locality (b) with                                                                                            |

|    | locality                                                                                                                                                               |

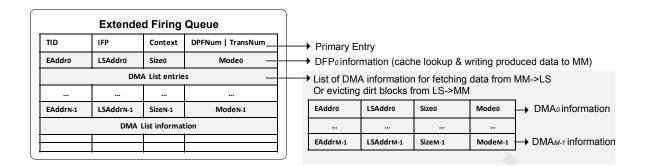

| 26 | The extended FQ                                                                                                                                                        |

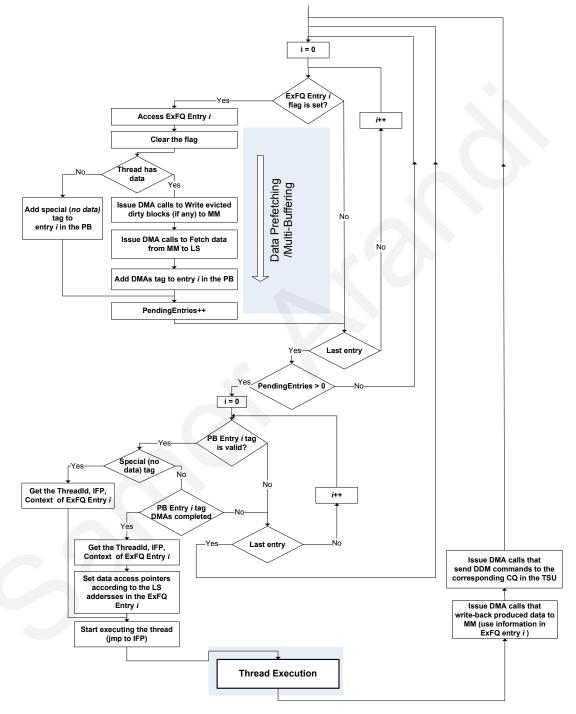

| 27 | DDM-VM <sub>c</sub> SPE runtime activities $\dots \dots \dots$         |

| 28 | Comparison of execution time with and without prefetching                                                                                                              |

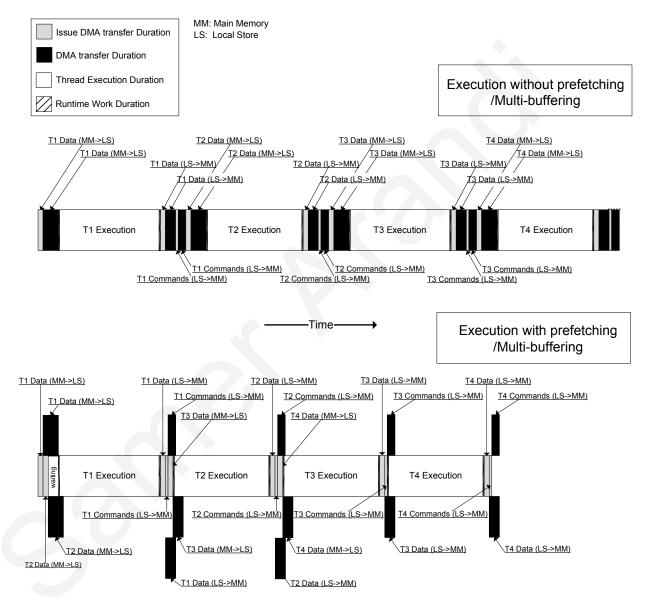

| 29 | The Architecture of the DDM-VM $_s$                                                                                                                                    |

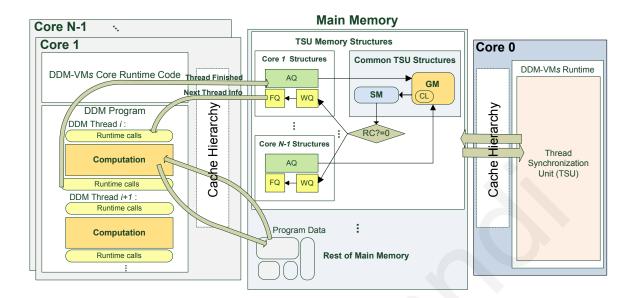

| 30 | The TSU Structures in the DDM-VM $_s$                                                                                                                                  |

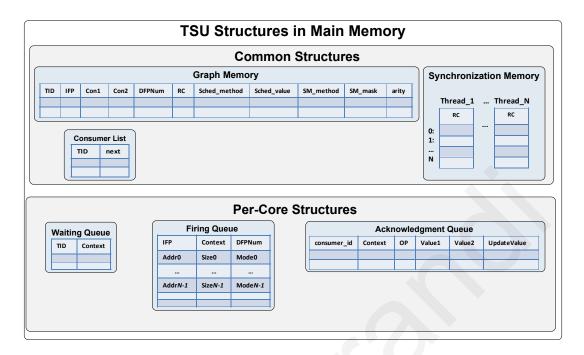

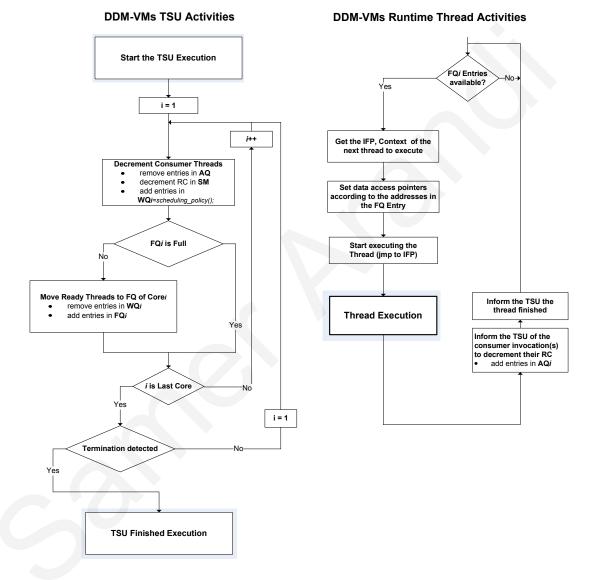

| 31 | The DDM-VM <sub>s</sub> TSU and Runtime Activities $\dots \dots \dots$ |

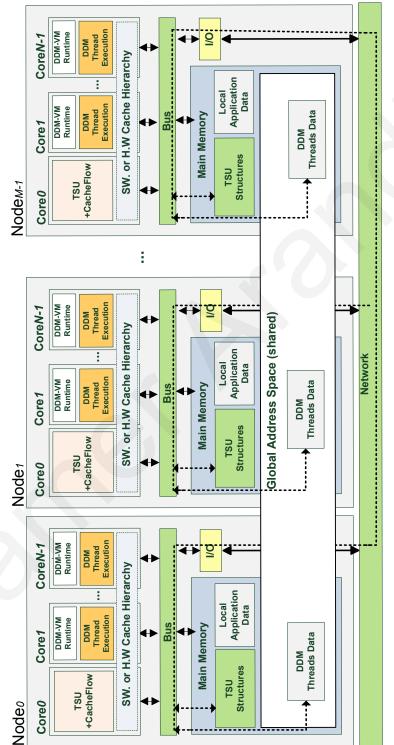

| 32 | The Distributed DDM-VM Architecture                                                                                                                                    |

| 33 | NIU Information Table                                                                                                                                                  |

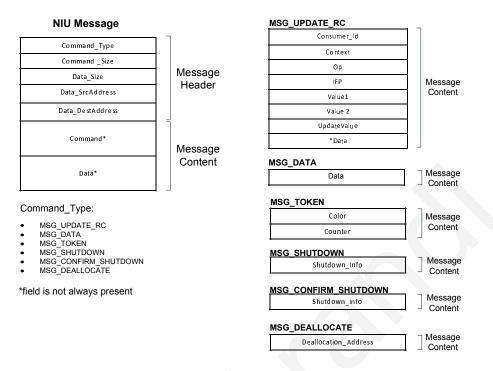

| 34 | NIU Messages                                                                                                                                                           |

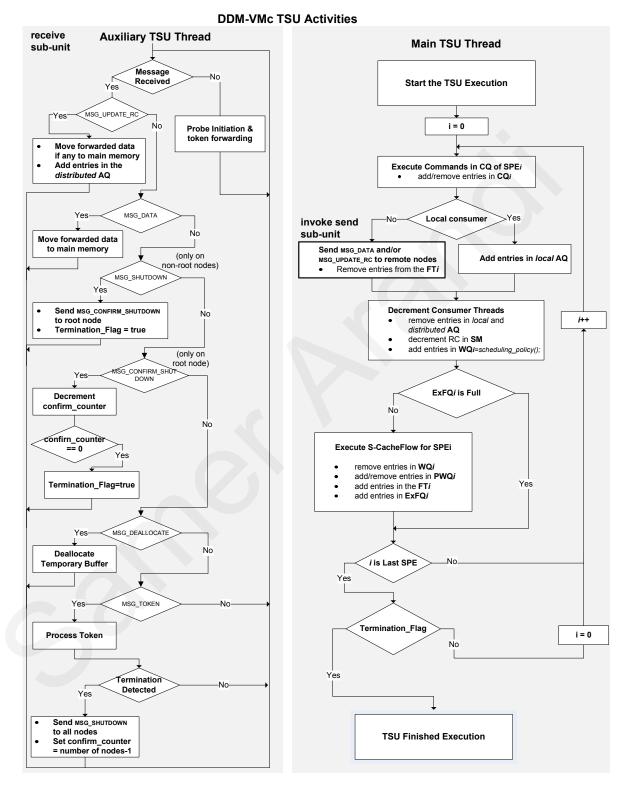

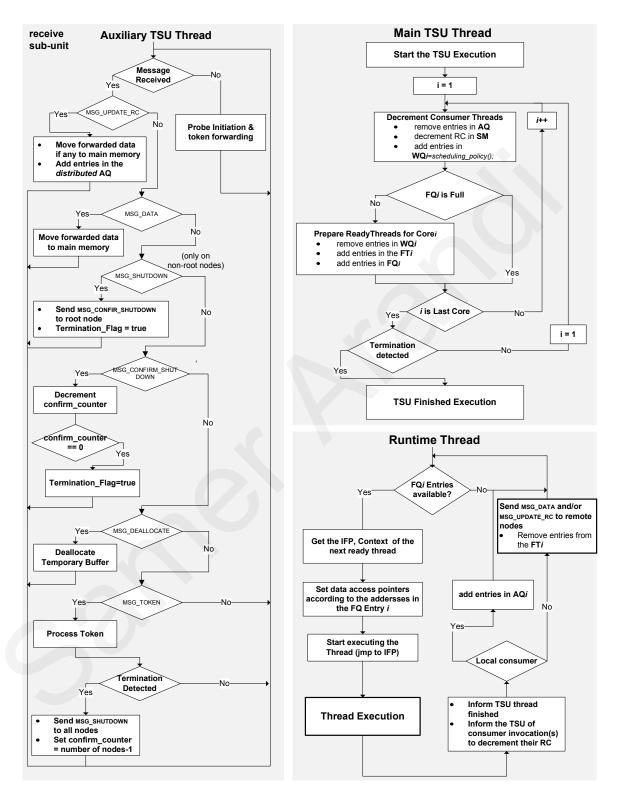

| 35 | TSU Activities on the PPE - Main and Auxiliary PPE Threads                                                                                                             |

| 36 | Distributed DDM-VM <sub>s</sub> TSU & Runtime Threads Activities on All the Cores in |

|----|--------------------------------------------------------------------------------------|

|    | the System                                                                           |

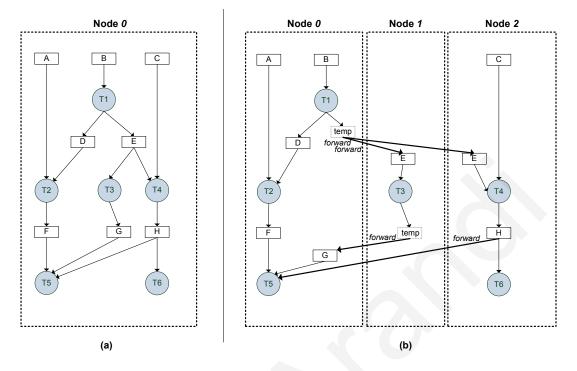

| 37 | Data Forwarding Example                                                              |

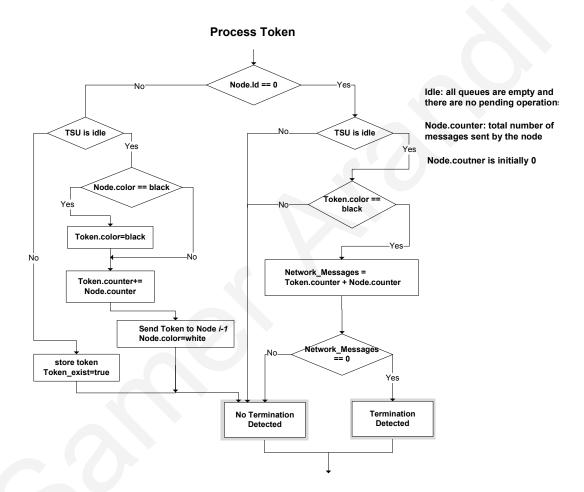

| 38 | Distributed Termination Detection - Probe Initiation and Token Forwarding 121        |

| 39 | Distributed Termination Detection - Token Processing                                 |

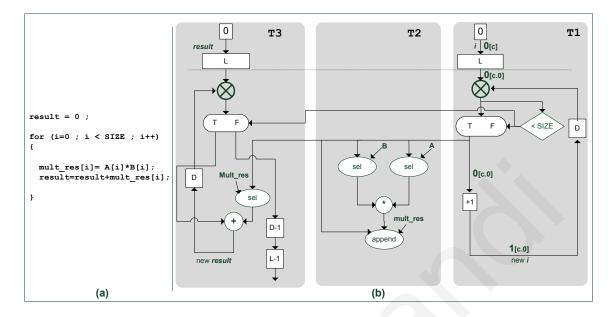

| 40 | The Vector Dot Product (a) Original Program (b) U-Interpreter Dynamic Data-          |

|    | Flow Graph                                                                           |

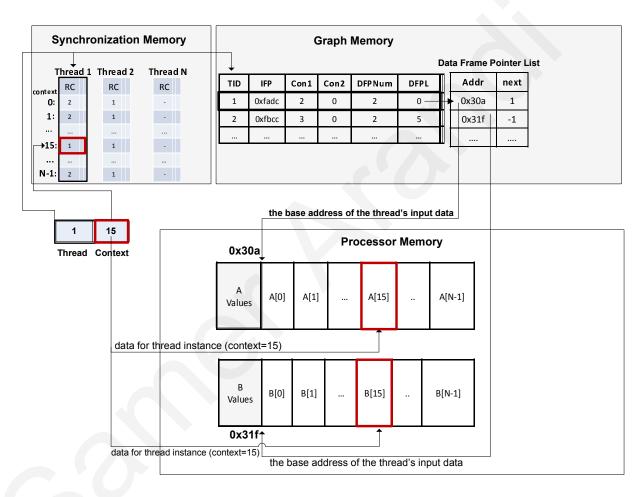

| 41 | Accessing Thread structures using a combination of the meta-data and the dy-         |

|    | namic context in DDM                                                                 |

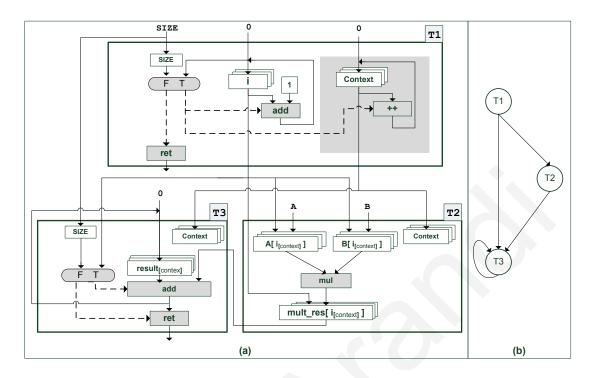

| 42 | The Vector Dot Product DDM Dependency Graph (a) Detailed view (b) High-level         |

|    | view                                                                                 |

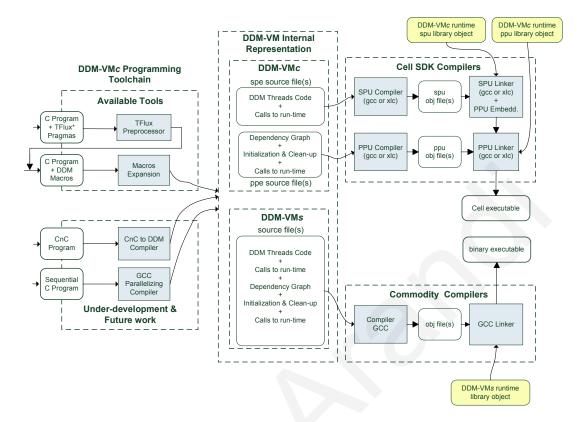

| 43 | The DDM-VM <sub>c</sub> Programming Toolchain                                        |

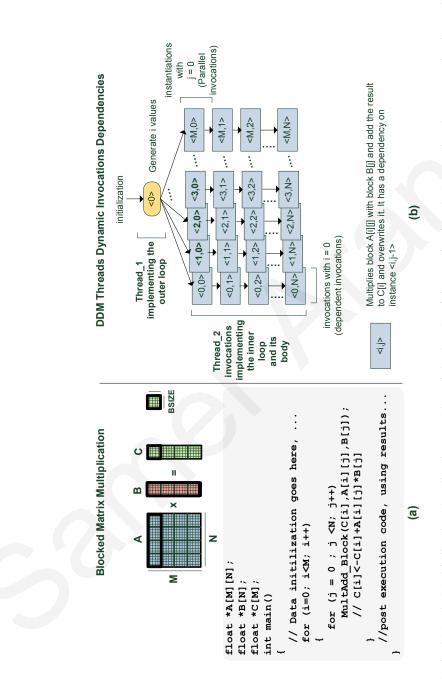

| 44 | The Blocked Matrix Multiplication Application (a) The original code of the appli-    |

|    | cation (b) Dependencies across the dynamic invocations of the DDM threads 133        |

| 45 | The code for the DDM threads using the DDM-VM macros                                 |

| 46 | Initialization, graph creation, graph execution and post-execution code              |

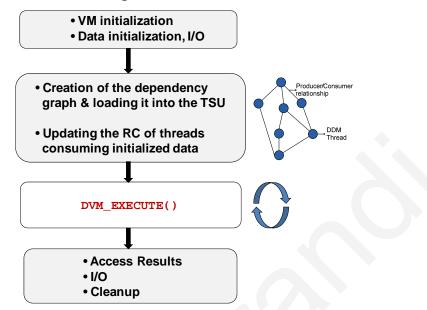

| 47 | The Flow of a DDM-VM Program Execution                                               |

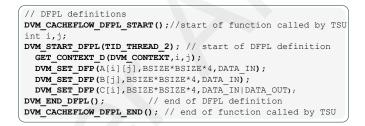

| 48 | DFPL definition macros                                                               |

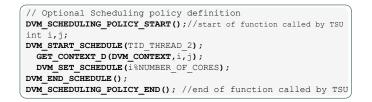

| 49 | Scheduling policy definition macros                                                  |

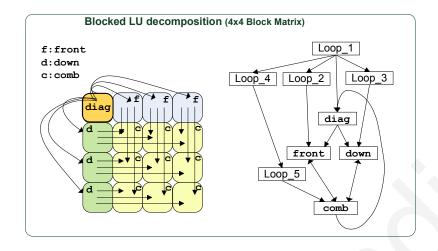

| 50 | The DDM-VM Blocked LU decomposition application - Original program code . 141        |

| 51 | The DDM-VM Blocked LU decomposition application - Dependency graph 142               |

| 52 | The DDM-VM Blocked LU decomposition application - Dependency graph among             |

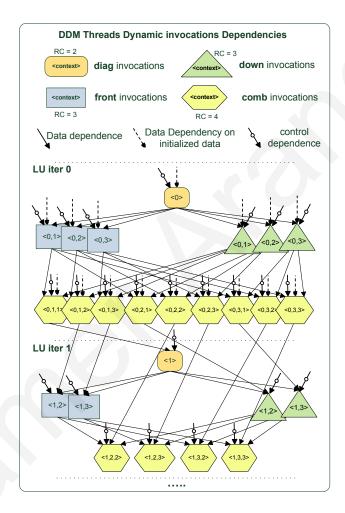

|    | the dynamic threads invocations                                                      |

| 53 | The DDM-VM Blocked LU decomposition application - The code of the DDM                               |

|----|-----------------------------------------------------------------------------------------------------|

|    | threads                                                                                             |

| 54 | The DDM-VM Blocked LU decomposition application. (a) The DFPL definition                            |

|    | macros (b) The main() function                                                                      |

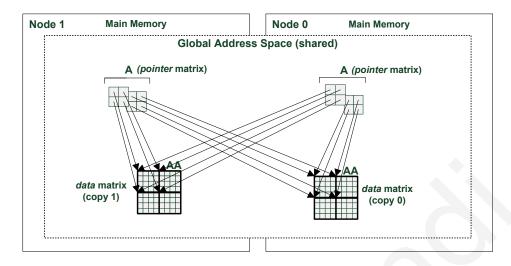

| 55 | Memory Layout for the LU Program - a System with Two Nodes and a 4x4                                |

|    | Blocked Matrix                                                                                      |

| 56 | Distributed DDM-VM LU Program - main() function                                                     |

| 57 | Distributed DDM-VM LU Program - DFPL Definition                                                     |

| 58 | Distributed DDM-VM LU Program - gather_data() function                                              |

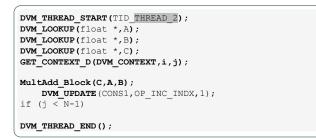

| 59 | The code of <i>THREAD_2</i> of the blocked matrix multiplication DDM-VM program,                    |

|    | shown previously in Figure 45, after applying the incremental update optimization 158               |

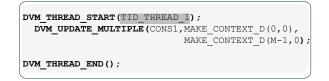

| 60 | The code of <i>THREAD_1</i> of the blocked matrix multiplication DDM-VM program,                    |

|    | shown previously in Figure 45, after applying the compound update optimization . 158                |

| 61 | The code of <i>diag</i> , <i>front</i> and <i>down</i> threads of the blocked LU decomposition DDM- |

|    | VM program, shown previously in Figure 53, after applying the compound update                       |

|    | optimization                                                                                        |

| 62 | The DDM-VM Blocked LU decomposition application after optimization. (a) The                         |

|    | main() function code (b) The code of the DDM threads (c) The DFPL definition                        |

|    | macros (d) the dependency graph                                                                     |

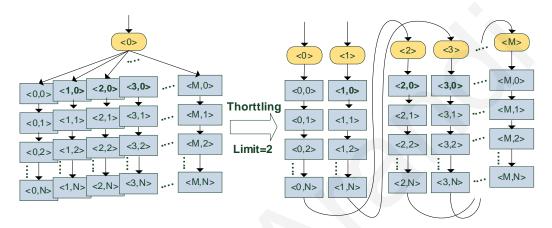

| 63 | Resource Management - Throttling with limit set to 2                                                |

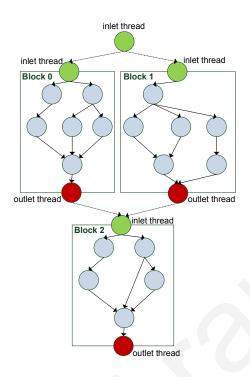

| 64 | Resource Management - Partitioning a program into DDM blocks                                        |

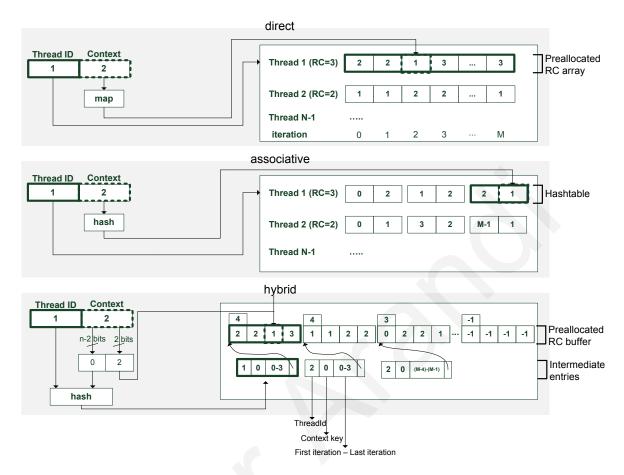

| 65 | Access Mechanisms in the Three SM Implementations                                                   |

| 66 | SM Allocation in Distributed DDM Execution                                                          |

| 67 | LU Decomposition - Using the extended TFlux directives                                              |

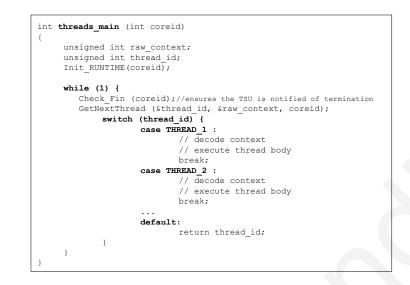

| 6 | 8  | The structure of the generated worker function                                                                                                              |

|---|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6 | 9  | The Event Tracing System (ETS)                                                                                                                              |

| 7 | 0  | Visualization Tool Screenshot - Distributed DDM Execution                                                                                                   |

| 7 | 1  | State Transitions for I-Structure Elements                                                                                                                  |

| 7 | 2  | DDM-VM Program with Run-time Determined Dependencies                                                                                                        |

| 7 | 3  | Resource management control - Effect of Firing Queue (ExFQ) size and Loop                                                                                   |

|   |    | Throttling on performance                                                                                                                                   |

| 7 | '4 | Effect of the different Synchronization Memory implementations on performance . 192                                                                         |

| 7 | 5  | Effect of locality on performance                                                                                                                           |

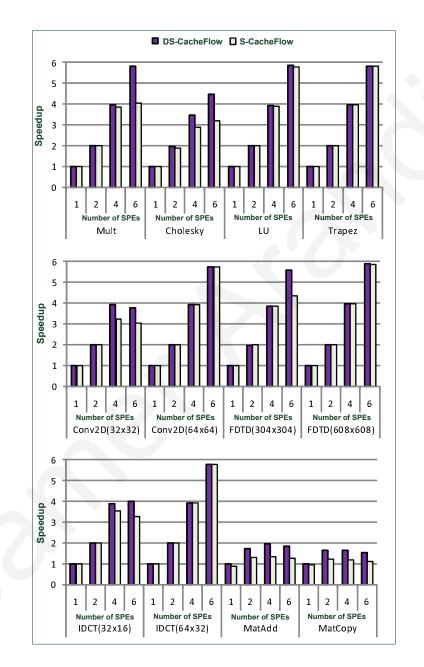

| 7 | 6  | Effect of thread granularity and S-CacheFlow vs. Distributed S-CacheFlow 196                                                                                |

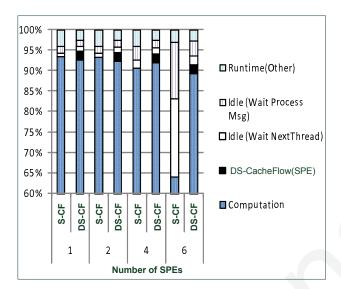

| 7 | 7  | S-CacheFlow vs. Distributed S-CacheFlow - MatMult SPE runtime execution                                                                                     |

|   |    | activities                                                                                                                                                  |

| 7 | 8  | DDM-VM <sub>c</sub> latency tolerance                                                                                                                       |

| 7 | '9 | Effect of problem sizes on performance                                                                                                                      |

| 8 | 0  | Comparison of DDM-VM $_c$ and CellSs Performance for the MatMult and Cholesky                                                                               |

|   |    | applications                                                                                                                                                |

| 8 | 1  | Comparison of DDM-VM $_c$ and Sequoia Performance for the MatMult and Conv2D                                                                                |

|   |    | applications                                                                                                                                                |

| 8 | 2  | Distributed DDM-VM <sub>c</sub> Execution - Speedup                                                                                                         |

| 8 | 3  | GFLOPs performance results for MatMult and Conv2D                                                                                                           |

| 8 | 4  | Effect of thread granularity on performance                                                                                                                 |

| 8 | 5  | Effect of problem sizes on performance                                                                                                                      |

| 8 | 6  | DDM-VM <sub>s</sub> overall performance $\dots \dots \dots$ |

| 87 | Speedup comparison: runtime-determined dependencies (R-D) v.s. runtime &                                                                                                                              |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | compile-time determined dependencies (RC-D) v.s. compile-time determined de-                                                                                                                          |

|    | pendencies (C-D) approaches                                                                                                                                                                           |

| 88 | Execution time comparison: execution time using the runtime-determined depen-                                                                                                                         |

|    | dencies approach v.s. the runtime-determined & compile-time determined depen-                                                                                                                         |

|    | dencies approach normalized to the execution time using the compile-time deter-                                                                                                                       |

|    | mined dependencies approach                                                                                                                                                                           |

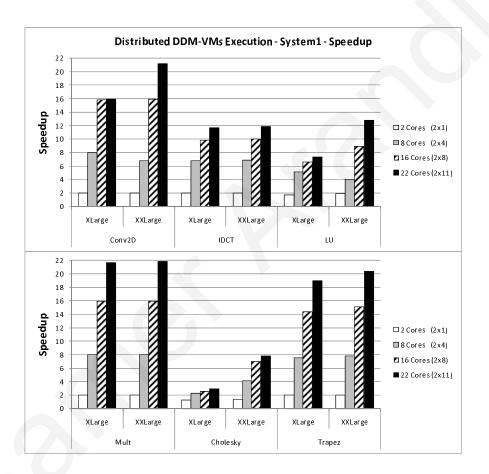

| 89 | Distributed DDM-VM <sub>s</sub> Execution (System-1) - Speedup $\dots \dots \dots$                    |

| 90 | Distributed DDM-VM <sub>s</sub> Execution (System-2) - Speedup $\ldots \ldots \ldots$ |

| 91 | The blocked Matrix Multiplication application. (a) Textual representation of the                                                                                                                      |

|    | CnC program (b) Graphical representation of the CnC program. (c) Equivalent                                                                                                                           |

|    | DDM dependency graph                                                                                                                                                                                  |

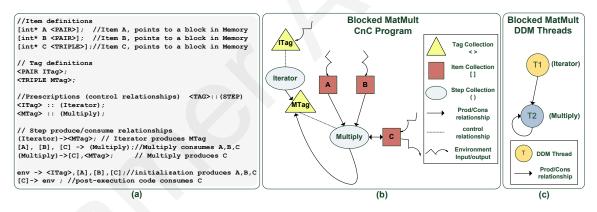

| 92 | Performance comparison between the macro-coded and compiler-generated ver-                                                                                                                            |

|    | sions of the matrix multiplication program                                                                                                                                                            |

| 93 | Format of the Events Summary file - DDM-VM $_c$                                                                                                                                                       |

| 94 | Visualization Tool Screenshot                                                                                                                                                                         |

| 95 | Utilization File Format                                                                                                                                                                               |

|    |                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                       |

|    |                                                                                                                                                                                                       |

# **Chapter 1**

## Introduction

#### 1.1 Introduction

Since the advent of digital computers, in the early 1940s, the computer architecture field has been dominated by the sequential model of execution. Advocates of parallel processing have being predicting the end of sequential computing and the shift to parallel processing [12] since the 1960s. However, chip designers have been using the exponentially increasing number of transistors (predicated by Moore's Law) to postpone the shift indefinitely, by designing more complex processors with larger cache sizes and continuously increasing the clock frequency.

However, the inability of the sequential model to tolerate long latencies (manifested mainly in the Memory Wall problem [132] referring to the widening gap in performance between the processor and the memory) combined with the Power Wall [129] and the Instruction Level Parallelism (ILP) Wall [129] problems eventually rendered this approach ineffective. The Power Wall refers to the prohibitive increase in power consumption and generated heat resulting from the complexity of the designs, and the ILP Wall refers to the scarce degree of exploitable Instruction Level Parallelism (targeted by such designs). Figure 1 shows the slow down in performance gains due to these problems.

Figure 1: Growth in processor performance since the mid-1980 relative to the VAX 11/780 measured by the SPECint benchmark (Figure from Hennessy & Patterson [93])

The envisaged solution was to utilize lower frequencies and use the silicon state to pack more cores on a chip [90]. These chips are known as Chip-Multiprocessors (CMP) or Multi-core Processors. Multi-core processors can be either homogeneous, consisting of similar cores or heterogeneous, consisting of cores with different properties. The motivation behind heterogeneous design is two folds [69]: First, it results in a more efficient utilization of the cores through better adaptation to the diversity of applications. The second advantage comes from a more efficient use of the die area for a given thread-level parallelism, which allows for a more power and area efficient design.

#### 1.2 Motivation

The switch to multi-cores was an engineering effort that did not address the fundamental issues that caused the previously stated problems: the long memory latencies (it actually exacerbates it as we will show shortly) and the complexity of the designs (Out-of-Order execution and large caches) that caused the power wall. Moreover, this switch elevated *concurrency* as a major issue in utilizing the increasing number of cores on a single-chip, as it soon became evident that traditional programming and execution models do not allow for efficient utilization of the large number of resources now available on a single chip. This task is even more complex on heterogeneous multi-core architectures, as different types of resources need to be individually optimized in order to achieve maximum global performance.

Another challenge facing the new multi-core designs is the Memory Wall, as even with lower clock rates, the problem manifests itself due to the increasing number of cores compared to the available resources dedicated for memory on the chip. This gets worse as the number of cores on the die increases [85]. One of the techniques applied to combat the memory wall is to utilize fast explicitly-managed on-chip memories in addition to the slower off-chip memory in the system. This technique is utilized by various stream processors such as the Stanford Merrimac [32] and Imagine [65] processors and modern parallel architectures such as the NVIDIA G80 [89] and the IBM Cell/B.E [63].

Using explicitly-managed memory hierarchies offers a great opportunity for increasing the performance by efficiently utilizing the memory resources, but at the same time poses a considerable challenge, as it typically requires the programmer to explicitly manage all data transfers between on-chip and off-chip memories, manage data allocation in the on-chip local memories, and guarantee a coherent view of the data. This further aggravates the problem of utilizing concurrency on multi-core architectures.

The Data-flow model [33, 11, 131] is a formal model that can handle concurrency in a distributed manner and tolerate memory and synchronization latencies efficiently, since an operation in data-flow is scheduled to execute when its data is ready. Moreover, the semantics of data-flow avoids the need for synchronization constructs like locks, barriers and busy-waiting. Dynamic Data-flow can expose the maximum degree of parallelism in a program as it only enforces *true dependencies*. Thus, the Data-flow model does not suffer from the limitations of the sequential model, mainly, the inability to tolerate memory latencies. Furthermore, Data-Flow systems can be simpler and more power efficient than conventional systems. Consequently, data-flow based models are a competitive candidate as the execution models for exploiting the resources of multi-core architectures.

#### **1.3 Problem Statement - Hypothesis**

In this thesis, we try to explore a Data-Flow based execution model for the efficient utilization of the resources of multi-core architectures.

#### 1.4 Approach

We follow an evolutional path by utilizing Dynamic Data-Flow on conventional Multi-core systems. We advance the state-of-the art of the Data-Driven Multithreading (DDM) model, which combines the distributed concurrency of the Data-Flow model with the efficient execution of the Control-Flow model.

The goal of this thesis is the design, implementation and optimization of a virtual machine supporting the DDM model of execution on multi-core systems. The virtual machine has two implementations, the first is designed for homogeneous multi-cores and the second is designed for heterogeneous multi-cores with a host/accelerator organization that utilize a software-managed memory hierarchy. A representative example of such architectures is the powerful Cell/B.E. processor. The virtual machine also supports distributed DDM execution on a cluster of multi-core nodes.

We summarize the goals of the proposed virtual machine:

- The implementation of a data-driven execution model on homogeneous and heterogeneous multi-cores (intra-node DDM).

- The implementation of automatic management of software-managed memory hierarchies through the development of a prefetching software cache utilizing data-driven caching policies.

- Supporting data-driven execution across distributed multi-core nodes (inter-node DDM).

The proposed virtual machine hides the low-level details of the parallel resources of the underlying machine and uses a unified representation for DDM programs. The VM, composed of the Thread Scheduling Unit (TSU) and the supporting runtime, handles the tasks of thread scheduling, synchronization and execution instantiation implicitly. A special prefetching software cache based on data-driven caching policies is developed to handle software-managed memory hierarchies.

We provide a number of alternative approaches for programming the virtual machine. The programmer can use a set of C macros that expand into calls to the VM or utilize a number of compiler *directives* with the aid of a preprocessor tool. Two other compilation tools are under development. The first utilizes the GCC compiler and the second utilizes the CnC declarative parallel programming language. We also provide monitoring and debugging tools to help with application development. A suite of 10 benchmarks was ported and used for performance evaluation and comparison with state-of-the-art systems.

#### 1.5 Thesis Contributions

The main contribution of this thesis is the design, implementation and optimization of a virtual machine that *efficiently* exploits Data-Flow concurrency on conventional/commercial multi-cores and *outperforms* other existing systems. The rest of the contributions include:

- Contribution 1: Development of the Data-Driven Multithreading Virtual Machine (DDM-VM), an efficient virtual machine that supports Data-Driven Multithreading execution on homogeneous multi-cores and heterogeneous high-performance multi-core systems. The DDM-VM utilizes DDM scheduling for exploiting the resources of multi-core architectures and tolerating synchronization and memory latencies. The DDM-VM has the following properties:

- It adheres to the formal dynamic data-flow constructs as described by the U-Interpreter.

- It has two individually optimized implementations: The DDM-VMs tailored for homogeneous multi-cores and the DDM-VMc tailored for heterogeneous multi-cores.

- The DDM-VM<sub>c</sub> is a high-performance implementation of DDM that achieves better performance than similar state-of-the-art systems. It is also the first DDM implementation optimized for heterogeneous multi-core architectures with a host/accelerator organization and a software-managed memory hierarchy.

- **Contribution 2**: Development of Software CacheFlow (S-CacheFlow), a fully-automated software prefetching cache with variable cache block sizes and explicit data locality optimizations for handling explicitly-managed memory hierarchies. Two implementations of the S-CacheFlow are developed and evaluated. The implementation that distributes part the data transfer tasks to the cores (distributed S-CacheFlow) is adopted as the default due to its performance advantage.

- **Contribution 3**: Development of the support for distributed DDM execution. The DDM-VM is the first DDM implementation supporting distributed DDM execution across a cluster of multi-core nodes. Previous implementation either supported distributed DDM execution across single-processor nodes [73] or DDM execution within a multi-core node [113].

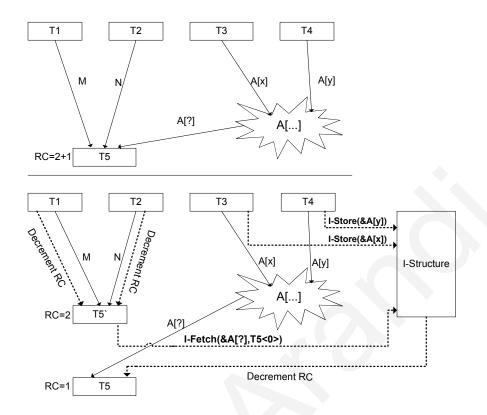

- Contribution 4: Development of the support for runtime dependency resolution using specialized I-Structures. The DDM-VM is the first DDM implementation that supports parallel execution of code that contains producer-consumer dependencies that are only resolved at runtime. The developed approach introduces a *helper/proxy* thread that resolves such dependencies at runtime and updates the consumer(s) accordingly with the help of an *I-Structure*. This permits taking advantage of the strengths of both compile-time and run-time dependency resolution simultaneously and expands the class of programs that can be mapped to the DDM model. It also has the potential to improve the programmability and enhance the yield of compilation methods generating data-flow code.

- Contribution 5: Development of a number of performance optimizations and monitoring & visualization tools.

Programming both implementations of the VM is done via a unified programming interface -utilizing C macros that hides most of the low-level differences of the underlying architectures. This interface is the target of a number of tools that facilitate the programming of the DDM-VM and provide various alternative approaches.

#### **1.6 Performance Evaluation**

#### 1.6.1 Methodology

We evaluate the two implementations of the DDM-VM for both single-node and distributed multi-node execution. The benchmark suite used in the evaluation consists of ten applications featuring kernels widely used in scientific and image processing applications. All of the benchmarks are coded in C using the DDM-VM *macros* and compiled using the compilers available from the IBM Cell SDK V2.1 in the case of the DDM-VM<sub>c</sub> implementation and the GCC 4.4.3 compiler in

the case of the DDM-VM<sub>s</sub>. The DDM-VM<sub>c</sub> implementation runs on a Sony Playstation 3 (PS3) machine with Linux. For the evaluation of the distributed execution we used a cluster of 4 PS3 machines.

The DDM-VM<sub>s</sub> implementation runs on a 12-core machine composed of two six-core AMD Opteron processors. For the evaluation of the distributed execution we use two clusters (to test different configurations of nodes/cores-per-node):

- 1. The first is composed of two 12-core machines (System-1 cluster)

- 2. The second is composed of four 4-core machines (System-2 cluster)

#### 1.6.2 Results

#### **1.6.2.1 DDM-VM**<sub>c</sub> Evaluation

- **Optimizations Evaluation:** To evaluate the effects of resource management and locality and synchronization memory optimizations on the performance, we use the MatMult and Cholesky benchmarks as two case studies. The first application is a representative of applications with a simple dependency graph and the second is a representative of applications with a complex dependency graph. Moreover, both applications are computationally intensive and performance-sensitive. The result of this evaluation is used to guide the performance optimization for all the benchmarks in the rest of the evaluation.

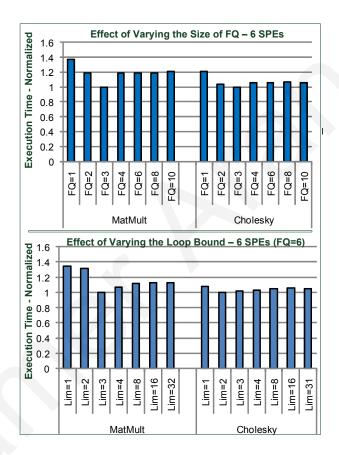

- Effect of Resource Management: To assess the DDM-VM resource management control mechanisms (both at the TSU level and at the program level) we have executed two sets of experiments for both benchmarks. In the first, we have varied the size of the TSU's Extended Firing Queue (ExFQ) and in the second, we have utilized *Loop Throttling* and varied the limit on the number of concurrent invocations of the

throttled threads. The results show that both mechanisms are effective in controlling the concurrency.

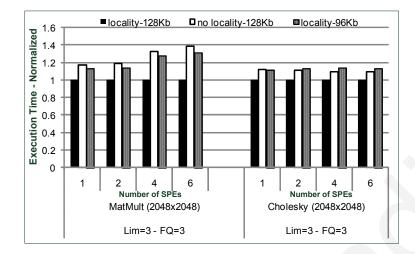

- Effect of Locality Optimizations: We compare the performance of the benchmarks with and without the locality optimization. The results demonstrate that utilizing locality improves the performance for both applications. The main source of improvement is the reduced demand of the private Local Store (LS) memory space, which permits fitting the data of more threads, thus allowing the TSU better chance to prefetch data and overlap latencies with computation. This result demonstrates the deep implications the size of the LS memory has on the execution behavior and consequently the importance of taking into account the size of the working set when choosing the granularity of the threads.

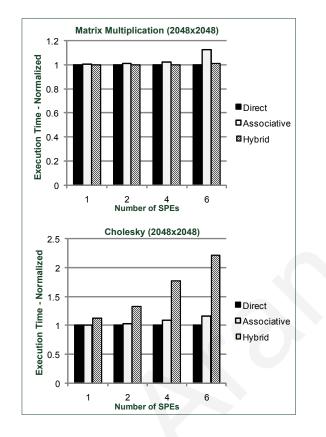

- Effect of Synchronization Memory Organization: As the operation of the Synchronization Memory is critical for the performance of DDM execution, we evaluated 3 different SM implementations. The results show that the *direct* implementation, which preallocates the SM entries achieves the best performance. The *associative* implementation, which allocates the entries on demand performs 2nd best on average. The performance of the *hybrid* implementation, which attempts to conserve the allocations by re-using SM entries depends on the execution pattern (locality of the SM updates) of the executed application.

- General Performance Evaluation:

- Effect of Thread Granularity and Software CacheFlow Implementations:

#### **Thread Granularities**

The results show that the performance improves as the threads granularity increases. As higher granularities amortize better the scheduling overheads of the TSU and S-CacheFlow operations and -further- allow DDM-VM<sub>c</sub> to hide the latency of data transfers through prefetching/multi-buffering.

#### **S-CacheFlow Implementations**

The distributed S-CacheFlow implementation (which distributes part the data transfer tasks to the SPE cores) performs better than the basic S-CacheFlow on all of the benchmarks in general. The advantage of the distributed implementation is clear when the number of cores is higher, as it precludes the PPE from becoming a bottleneck due to the demand of the S-CacheFlow.

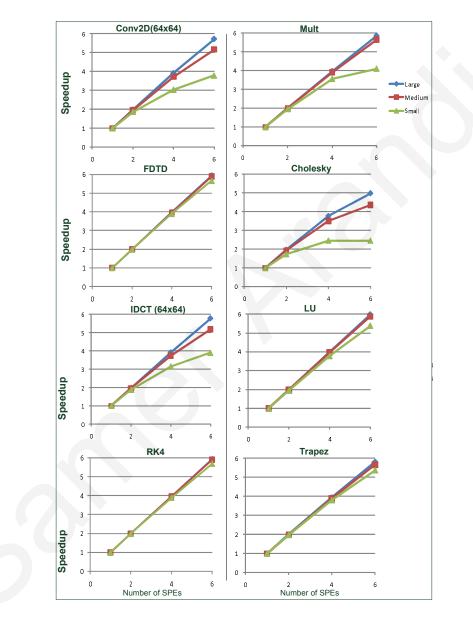

#### - Effect of Problem Size:

To assess the effect of the program size on performance we have executed the benchmarks for different problem sizes. The results show that the system generally scales well across the range of the benchmarks achieving almost linear speedup for the large problem sizes, as large problem sizes result in longer execution time, which amortizes initialization and parallelization overheads.

- Concurrency and Latency Tolerance: To evaluate the potential of the DDM-VM<sub>c</sub> in exploiting concurrency and tolerating synchronization and memory latencies, we have performed a number of experiments in which we limit the number of threads that can be scheduled concurrently to 1 (purely sequential scheduling of DDM-VM applications), 2 and 3. We compare the results with a normal (non-DDM) sequential

program. The results show that enabling the scheduling and execution of multiple concurrent threads permits the TSU to overlap the scheduling and data transfers latencies (via prefetching) with the execution of the threads. This illustrates that DDM-VM<sub>c</sub> effectively leverages the decoupling of synchronization and computation for maximum tolerance of latencies.

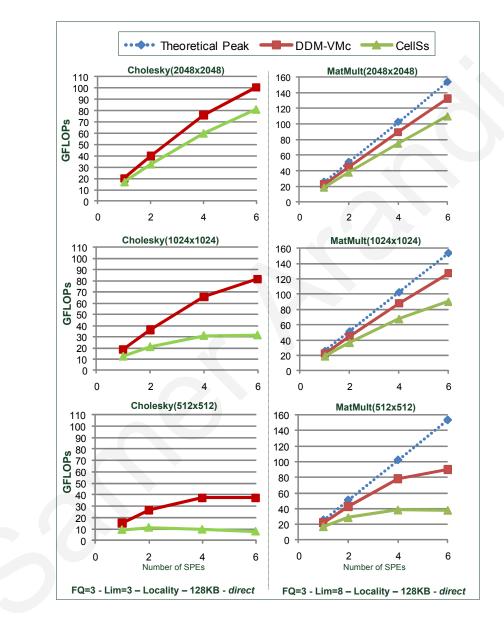

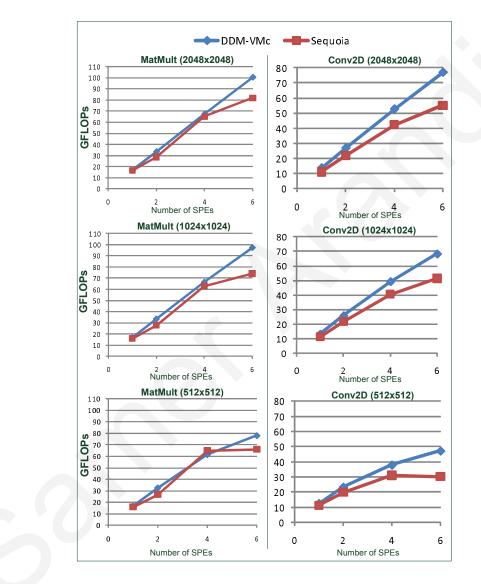

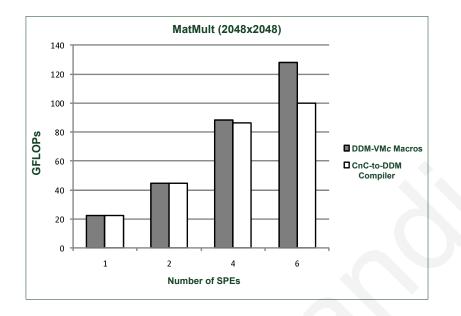

- GFLOPs Performance and Comparison: To examine the efficiency of the DDM-VM<sub>c</sub> we report the GFLOPs performance results of three computationally intensive applications, MatMult, Cholesky and Conv2D and compare them with the CellSs [18, 94] and Sequoia[41] platforms that target the Cell processor.

- \* The results show that MatMult and Conv2D scale almost linearly for the large problem size and achieved 132 GFLOPs (88% of the theoretical peak performance) and 77 GFLOPs, respectively on 6 SPEs. The Cholesky application achieves a speedup of 5 out of 6 despite its complex dependency graph, yield-ing 101 GFLOPs for the large problem size.

- \* Comparing the performance with CellSs for MatMult and Cholesky, DDM-VM<sub>c</sub> achieves an average of 42% and 112% performance improvement for MatMult and Cholesky, respectively. Moreover, DDM-VM<sub>c</sub> achieves the best improvement v.s. CellSs for the smaller problem sizes, which indicates that it introduces less overhead for exploiting concurrency.

- \* Comparing the performance with Sequoia for MatMult and Conv2D, DDM-VM<sub>c</sub> achieves an average of 12% and 25% performance improvement for MatMult and Conv2D, respectively.

The results indicates the efficiency of the DDM-VM<sub>c</sub> and its ability to outperform other platforms on the Cell.

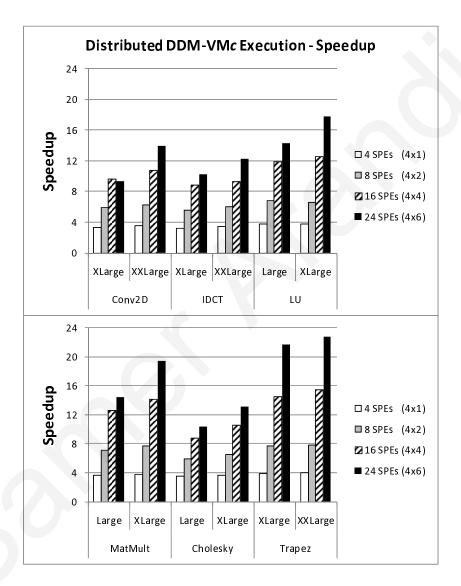

- Distributed DDM-VM<sub>c</sub> Execution: The results of evaluating the distributed DDM-VM<sub>c</sub> execution on a four PS3 cluster shows that:

- The system achieves an average of 80% of the maximum possible speedup when utilizing various number of SPEs per node for all the benchmarks on the largest input size.

- As the input size increases the system scales better: the average speedup (on all the benchmarks) utilizing all the SPEs is 13.4 out of 24 for the smaller input size and 16.54 out of 24 for the larger input size. This is expected as larger problem sizes allow for amortizing the overheads of the parallelization.

- Compared to single-node execution larger input sizes and larger granularities are needed in general for the system to scale due to the additional latencies introduced by the network data and synchronization messages transfer.

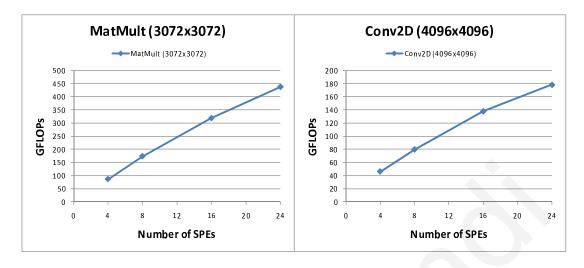

- When utilizing all the SPEs on the four nodes the system delivers an impressive 0.44

TFLOPs for the MatMult benchmark and 178 GFLOPs for the Conv2D benchmark

(the two computationally intensive benchmarks), which demonstrates the efficiency of the distributed execution on the DDM-VM<sub>c</sub>.

#### 1.6.2.2 DDM-VM<sub>s</sub> Results

Overall, the results of the DDM-VM<sub>s</sub> evaluation confirm the findings of the DDM-VM<sub>c</sub> evaluation:

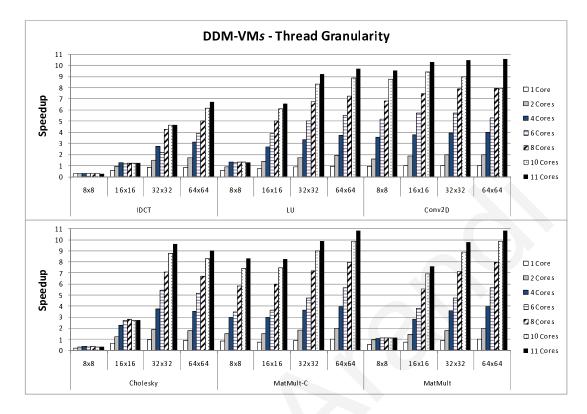

- Effect of Thread Granularity: When executing the benchmarks with varying thread granularities, the results show that the performance improves as the granularity increases, since higher granularities amortize better the scheduling overheads of the TSU.

- Effect of Input Size: When executing the benchmarks for various problem sizes. The performance improves as the input size increases, since larger problem sizes result in longer execution time, which amortizes initialization and parallelization overheads.

- **Overall Performance:** The results of executing all the benchmarks demonstrate that overall, the system scales well over the range of the benchmarks and achieves - when utilizing all the cores - an average speedup of 9.6 out of 11 (the maximum possible speedup is 11 since we reserve one core out of the 12 for the execution of the TSU), which indicates the efficiency and scalability of the system.

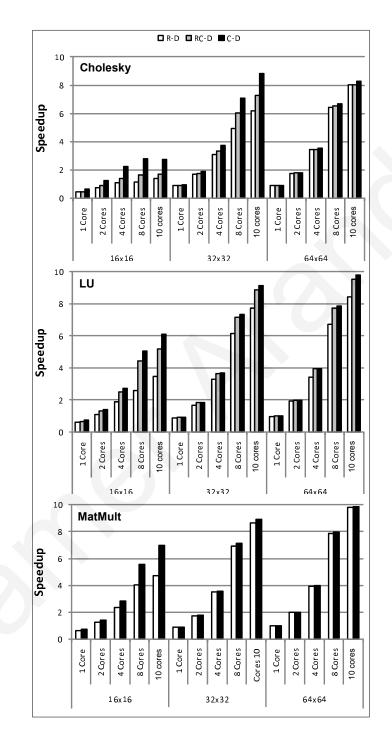

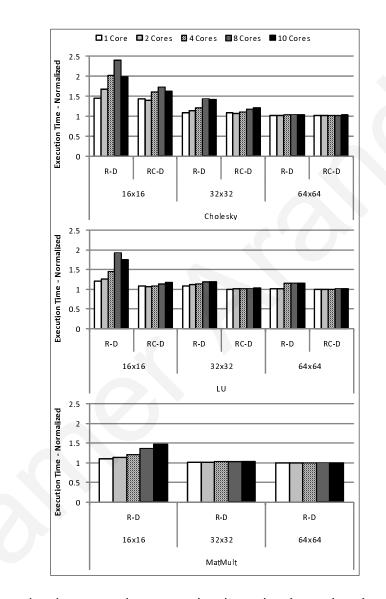

- Runtime Dependency Resolution Evaluation: We evaluate our technique for handling runtime-determined dependencies by studying the effect of the overheads of the I-Structure operations on the performance. We compare the performance of 3 versions of a subset of the benchmarks for various thread granularities. The first version utilizes the compile-time approach for resolving the dependencies. The second version combines both approaches and the third utilizes the runtime approach.

The results demonstrate that:

The best performance is delivered by the version utilizing the compile-time approach, followed by the one utilizing the combination of the compile-time and runtime approaches.

- The performance loss (relative to the compile-time version) is higher for lower granularities and decreases as we increase the granularity. For example, when using 10 cores in one of the applications, the performance loss when utilizing the runtime approach for all the dependencies is 43% for the smallest granularity compared to 13.6% for the largest granularity. When utilizing a combination of the two approaches the loss is 14.8% for the smallest granularity compared to 2.2% for the largest granularity. The same observation applies to the rest of the benchmarks.

- Utilizing run-time dependency resolution (for part or all of the data dependencies in the evaluated programs) achieves acceptable performance compared to the compiletime approach, whilst utilizing thread granularities in the range we normally utilize in DDM-VM programs.

- Distributed DDM-VM<sub>s</sub> Execution: The results of evaluating the distributed DDM-VM<sub>s</sub> execution on the *System-1* and *System-2* clusters confirm the findings of the distributed DDM-VM<sub>c</sub> evaluation:

- The system achieves an average of 80% and 84% of the maximum possible speedup when utilizing various number of cores per node for the largest input size on *System-1* and *System-2* clusters, respectively.

- The system scales better as the input size increases.

- Larger input sizes and granularities (compared to single-node execution) are needed for the system to scale.

#### 1.7 Thesis Outline

In Chapter 2 we present background information followed by a review of the related work. Chapter 3 presents the architecture of the DDM-VM and its two implementations. The chapter also describes the design and implementation of the prefetching software cache utilized for handling software-managed memory hierarchies. In Chapter 4 we describe the support for distributed DDM execution across a cluster of multi-core nodes. Chapter 5 presents the programming methodology and tool-chain utilized with the DDM-VM, in addition to a number of optimizations employed to improve the performance of the DDM-VM. In Chapter 6 we describe the support for runtime dependency resolution. The evaluation results for the two DDM-VM implementations for both single-node execution and distributed execution are presented in Chapter 7. Finally, the conclusion and future work are presented in Chapter 8.

# **Chapter 2**

## **Background and Related Work**

## 2.1 Introduction

In this chapter we present background information and related work focusing on multi-core architectures and data-flow. For multi-core architectures, we follow the evolution of computer architectures from monolithic to multi-core. The debut of the multi-core architectures and the reasons behind it are then presented. We highlight heterogeneous multi-core designs and present the motivation behind this approach and the advantages it promises in respect to power and area efficiency compared to the homogeneous designs. We also illustrate some of the current heterogeneous processors and systems, focusing on the Cell/B.E. heterogeneous processor. We illustrate some of its unique features like the explicitly-managed private memories of its cores.

Following that, we review the data-flow model proposed in the early 70's by Jack Dennis and highlight its strengths and weaknesses. We follow its evolution from the static & dynamic data-flow architectures into the hybrid data-flow/control-flow and multithreading architectures. Finally, we review state-of-art work related to the topic of this thesis.

#### 2.2 Background Information

#### 2.2.1 From Monolithic to Multi-core Architectures

The trend in the last two decades for achieving high-performance was driven by the increase in the operating frequency and extracting more instruction-level parallelism (ILP) by exploiting sophisticated hardware techniques like Out-of-Order & Superscalar execution [118, 110, 49]. This was feasible due to the exponentially increasing number of transistor predicted by Moore's Law [84]. This trend enabled the engineers to come up with very complex designs and use large sizes of cache. Although successful for several years this strategy hit many walls: the memory, power, complexity and ILP walls [132, 90, 129]. We present more details on these issues in the subsequent sections.

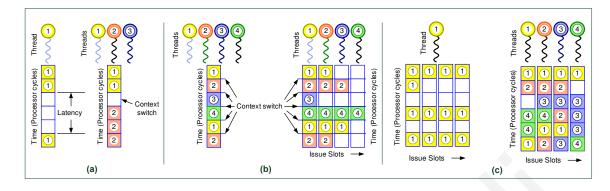

## 2.2.1.1 Pipelining Processors

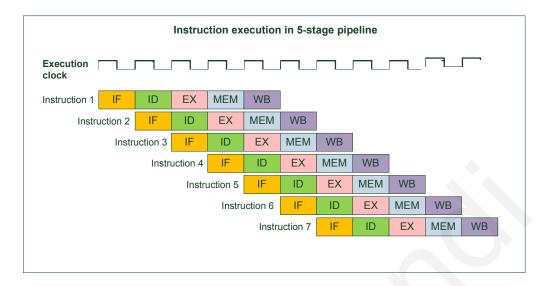

With the success of the Reduced Instruction Set Computer (RISC) architectures in the early 80's, most of the RISC machines utilized pipelining to improve performance. Pipelining exploits parallelism between instructions (Instruction Level Parallelism - ILP) to increases the instruction throughput, which translates into a reduction in the total execution time of the application. However, the ideal potential of pipelining is hardly achieved [93] due to imbalances in the time of the different pipeline stages, the overhead introduced by pipelining and the different pipeline hazards that result from limited hardware resources (structural hazards) or the properties of the executed program (data and control hazards). Figure 2 illustrates the state of a five-stage pipeline with the ideal execution of seven instructions.

To improve the performance of pipelining many techniques, both software and hardware, are deployed. *Resource duplication* and *functional unit pipelining* are utilized to reduce structural

Figure 2: A five-stage pipeline with ideal execution of seven instructions

hazards. *Forwarding* and *Software Scheduling* are utilized to reduce data hazards. The former, forwards the results of some functional units as direct inputs for other units in the pipeline to avoid a stall. The latter -utilized by the compiler- re-arranges instructions so as to increase the distance between dependent instructions. The compiler can also schedule instructions to reduce the effect of branches (the source of control hazards) by filling the branch delay slot usefully which avoids the stall that would have been needed waiting for the result of the branch to be calculated.

*Branch prediction* is utilized by the compiler to reduce control hazards. This involves static prediction of branches where the branch is always assumed to be taken or not-taken and then a restart of the pipeline if the prediction result was wrong. Most of the previous techniques are utilized with *unrolling* which also reduces the number of branches in a loop and consequently the number of control hazards.

Due to the limited accuracy of static prediction most of the recent processors utilize *dynamic branch predication* techniques implemented in hardware. In its simplest form dynamic prediction employs a branch history table that records the results of a branch and indexes it by hashing the

address of the branch instruction. More sophisticated schemes are also utilized which correlate the results of other recent (nearby) branches as well.

#### 2.2.1.2 Dynamic Scheduling

Dynamic scheduling (or out-of-order execution) allows the hardware to re-arrange the order of instruction execution to reduce the effects of hazards without breaking the data dependencies between the instructions of the program. This scheme has the advantage that it allows the processor to tolerate events like a cache-miss by executing other non-dependent instructions while waiting for the data to arrive. It also can handle the cases where the compiler cannot reason about the dependency at compile time. As dynamic scheduling introduces the potential for name dependencies: Write-After-Read and Write-After-Write (WAR and WAW), *register renaming* is utilized to handle this issue by renaming all destination registers including those of pending read or write instructions referring to an earlier instruction.

## 2.2.1.3 Hardware-based Speculation

Hardware-based speculation is a technique that reduces the effect of control hazards further than what branch predication can do. It speculates the outcome of branches and executes the program as if the speculation guess was correct. To support the ability to recover the state of the processor in case the speculation was not correct, instructions are allowed to finish execution however, committing their results to the register file is delayed until after the outcome of the branch is determined.

#### 2.2.1.4 Multi-issue Architectures

Multiple-issue processors try to improve performance by issuing more than one instruction per cycle. These processors can be classified into two types:

- 1. Statically/Dynamically Scheduled Superscalar Processors

- 2. Very Long Instruction Word (VLIW) Processors