Department of Electrical and Computer Engineering

# O/S-enabled on-line Software-Based Self-Test and Recovery for Resilient Shared-Memory Multicore Systems

Michael A. Skitsas

A Dissertation

Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

at the University of Cyprus

© Michael A. Skitsas, 2017

### **VALIDATION PAGE**

#### Michael A. Skitsas

# O/S-enabled on-line Software-Based Self-Test and Recovery for Resilient Shared-Memory Multicore Systems

The present Doctorate Dissertation was submitted in partial fulfillment of the requirements for

the Degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering, and was approved on December 5, 2017 by the members of the Examination Committee.

Research Supervisor

Dr. Maria K. Michael

Research Supervisor

Dr. Chrysostomos Nicopoulos

Committee Chair

Dr. Theocharis Theocharides

Committee Member

Dr. George Ellinas

Committee Member

Dr. Stelios Neophytou

Committee Member

Dr. Michalis Psarakis

## DECLARATION OF DOCTORAL CANDIDATE

| The present doctoral dissertation was submitted in partial fulfillment of the requirements for   |

|--------------------------------------------------------------------------------------------------|

| the degree of Doctor of Philosophy of the University of Cyprus. It is a product of original work |

| of my own, unless otherwise mentioned through references, notes, or any other statements.        |

|                                                                                                  |

|                                                                                                  |

|                                                                                                  |

|                                                                                                  |

# Περίληψη

Καθώς η τεχνολογία εξελίσσεται, τα μεγέθη αποτύπωσης ολοκληρωμένων κυκλωμάτων συρρικνώνονται, τα τρανζίστορ γίνονται λιγότερο αξιόπιστα. Ως αποτέλεσμα αυτής της εξέλιξης, τα μελλοντικά συστήματα αναμένεται να είναι πιο ευάλωτα σε φαινόμενα φθοράς (με την πάροδο του χρόνου και την χρήση). Το ζήτημα της φθοράς με την πάροδο του χρόνου και της βαθμιαίας υποβάθμισης καθιστά αναγκαία την χρήση μηχανισμών που επιτρέπουν την προστασία του συστήματος από ανεπιθύμητες συμπεριφορές διευκολύνοντας έτσι στην ανίχνευση, τον μετριασμό ή / και την αποκατάσταση ορθής λειτουργίας από σφάλματα καθ 'όλη τη διάρκεια ζωής του συστήματος. Πρόσφατα, στην βιβλιογραφία έχουν προταθεί αρκετές τεχνικές για έλεγχο των συστημάτων που να επιτρέπουν τη δυναμική ανίχνευση μόνιμων σφαλμάτων. Η ανίχνευση σφαλμάτων από τα ίδια τα συστήματα με την χρήση λογισμικού είναι μια διαδεδομένη τεχνική στον τομέα ελέγχου ψηφιακών κυκλωμάτων και μικροεπεξεργαστών. Η λειτουργία αυτή βασίζεται στην εκμετάλλευση των υφιστάμενων διαθέσιμων πόρων που υπάρχουν στο σύστημα. Πέρα από την ανίχνευση σφαλμάτων, τα σύγχρονα συστήματα πρέπει να ενισχυθούν με μηχανισμούς που είναι σε θέση να επιδιορθώσουν και να ανακτήσουν την ορθή λειτουργία του συστήματος στην παρουσία σφάλματος, προκειμένου να παραμείνει λειτουργικό παρά την ύπαρξη μόνιμων βλαβών.

Σκοπός αυτής της διατριβής είναι η ανάπτυξη τεχνικών για: (i) ανίχνευση σφαλμάτων, (ii) μεθοδολογίες προγραμματισμού για την αύξηση της διαθεσιμότητας του συστήματος κατά τη διάρκεια των ελέγχου του συστήματος και (iii) ενίσχυση του συστήματος με δυνατότητες αποκατάστασης. Το πρώτο μέρος αυτής της εργασίας εισάγει ένα νέο παράδειγμα ανίχνευσης σφαλμάτων που ελέγχει το σύστημα για σφάλματα στη διακριτότητα των επί μέρους συστημάτων (υπολογιστικών μονάδων) ενός επεξεργαστή σε συστήματα πολλαπλών πυρήνων λαμβάνοντας υπόψιν το ιστορικό της λειτουργίας τους. Συγκεκριμένα, αναπτύχθηκε το πλαίσιο DaemonGuard που επιτρέπει την παρατήρηση σε πραγματικό χρόνο των επί μέρους υπολογιστικών συστημάτων ενός επεξεργαστή εκτελώντας

μια διαδικασία για έλεγχο (σε τοπικό επίπεδο) χωρίς να γίνεται ολικός έλεγχος του επεξεργαστή για σφάλματα σε επίπεδο υλικού. Αυτή η τεχνική στοχεύει στη μείωση του χρόνου εκτέλεσης ελέγχου αποφεύγοντας τον συχνό έλεγχο των μονάδων των οποίων η χρήση ήταν σε χαμηλό επίπεδο. Το δεύτερο μέρος διερευνά τη σχέση μεταξύ του χρόνου κατά τον οποίο το σύστημα βρίσκεται υπό έλεγχο και του συνολικού χρόνου που χρειάζεται να ελεγχθούν όλοι οι πυρήνες του συστήματος. Για αυτό το σημείο στην έρευνα μας, αναπτύσσουμε ένα πλαίσιο εξερεύνησης ικανό να προσδιορίσει την καλύτερη πολιτική προγραμματισμού για να αυξήσει τη διαθεσιμότητα του συστήματος. Επιπλέον, προτείνουμε, αξιολογούμε και ενσωματώνουμε μια νέα μεθοδολογία που στοχεύει στην περαιτέρω βελτίωση των τεχνικών καθώς το σύστημα μεγαλώνει. Για το τελευταίο μέρος της παρούσας διατριβής, προτείνουμε τεχνικές που βελτιώνουν το προτεινόμενο πλαίσιο και μπορούν να υποστηρίξουν δυνατότητες αποκατάστασης της σωστής λειτουργίας παρά την εμφάνιση σφαλμάτων. Συγκεκριμένα, προτείνουμε έναν αποδοτικό μηχανισμό ανάκτησης και επαναφοράς, ο οποίος, μετά την ανίχνευση σφαλμάτων, μπορεί να επαναφέρει το σύστημα στην πιο πρόσφατη έγκυρη κατάσταση ορθής λειτουργίας και να επαναλά-βει την εκτέλεση, υποθέτοντας την απενεργοποίηση του ελαττωματικού πυρήνα, οδηγώ-ντας έτσι σε ένα υποβαθμισμένο μεν, αλλά λειτουργικό σύστημα. Όλες οι προτεινόμενες τεχνικές αξιολογούνται μέσω μιας σειράς πειραμάτων με τη χρήση προσομοίωσης.

## **Abstract**

As technology scales deep into the sub-micron regime, transistors become less reliable. Future systems are widely predicted to suffer from considerable aging and wear-out effects. The issue of aging and gradual degradation necessitates the use of mechanisms that can enable protection against undesired system behavior by facilitating detection, mitigation, and/or recovery from faults throughout the lifetime of the system. Recently, several on-line testing techniques have been proposed in literature enabling dynamic detection of permanent faults. Software-based Self-Testing (SBST) is an emerging new paradigm in the testing domain, which relies on the exploitation of existing available resources resident in the system. Beyond the detection of faults, modern systems must be enhanced with mechanisms able to self-repair and recover the system to a fault-free state, in order to remain functional despite the presence of permanent faults.

The objectives of this work are to develop techniques for: (i) on-line fault detection, (ii) scheduling methodologies to increase the system availability during testing and (iii) enhance the system with recovery capabilities. The first part of this thesis introduces a new paradigm of SBST that performs testing at the granularity of individual microprocessor core components in multi-/many-core systems based on the utilization. In particular, we develop the DaemonGuard, a framework that enables the real-time observation of individual sub-core modules and performs on-demand selective testing of modules that have been stressed. This technique aims to reduce the testing time by avoiding the over-testing of under-utilized units. The second part investigates the relation between system test latency and test time overhead under several scheduling policies. For this part we develop an exploration framework able to identify the best scheduling policy in order to increase system availability under a given test latency constraint. Additionally, a new methodology aiming to reduce the extra overhead related to testing that is incurred as the system scales up (i.e. the number of on-chip cores increases) is integrated and evaluated under the developed exploration framework. For the last part of this thesis, we propose to enhance our framework to support fault recovery capabilities. In particular, we pro-

pose an efficient check pointing and rollback recovery mechanism which, upon fault detection, can restore the system to the most recently valid correct state and resume the normal operation assuming disabling of the faulty core, thereby leading to a healthy (but degraded) system. All the proposed techniques are evaluated through a series of experiments using a full-system, execution-driven simulation framework running a commodity operating system and real multi-threaded workloads.

## **Acknowledgments**

First, I would like to express my deepest gratitude to my research co-advisors, Dr. Maria Michael and Dr. Chrysostomos Nicopoulos for their help, guidance and support during my research studies. I am also indebted to the members of my examination committee Dr. Theocharis Theocharides, Dr. George Ellinas, Dr. Michalis Psarakis and Dr. Stelios Neophytou, who dedicated time to review this dissertation, and provided feedback and suggestions.

I would like to thank the faculty of Electrical and Computer Engineering department, as well as the KIOS administrative assistants. I would also like to acknowledge the University of Cyprus for supporting my research.

Furthermore, I would like to express my gratitude to my colleagues at KIOS Research Center for contributing in the creation of a friendly work environment, their friendship and the constructive discussions. A special thanks to my best man Demetris Stavrou and my friends Demetris Eliades, George Milis, Vasso Reppa, Alexandros Kyriakides, Stavros Hadjitheophanous and Nikodimos Georgiades for their ongoing encouragement towards the completion of my goals.

From these acknowledgments, I could not have left behind my beloved parents, my brother Marios and my sister Polyxeni for their endless support and understanding.

This thesis is dedicated to my wife Ismini for her love and patience and to my three children Andreas, Irene and Argyro for giving me extra motivation and filling my life with wonderful moments!

## **Publications**

#### **Journal Publications**

- 1. **M. A. Skitsas**, C. A. Nicopoulos and M. K. Michael, "Exploring System Availability during Software-Based Self-Testing of Multi-core CPUs,", Under Review, Journal of Electronic Testing: Theory and Applications.

- M. A. Skitsas, C. A. Nicopoulos and M. K. Michael, "DaemonGuard: Enabling O/S-Orchestrated Fine-Grained Software-Based Selective-Testing in Multi-/Many-Core Microprocessors," in IEEE Transactions on Computers, vol. 65, no. 5, pp. 1453-1466, May 1 2016.

#### **Book Chapters**

1. **M. A. Skitsas**, C. Nicopoulos, P. Bernadi, E. Sanchez, M. K. Michael, "Chapter 15: Self-testing of multi-core processors", The Institution of Engineering and Technology (IET), IET Digital Library, to appear.

#### **Conference Proceedings**

- 1. **M. A. Skitsas**, C. A. Nicopoulos and M. K. Michael, "Toward efficient check-pointing and rollback under on-demand SBST in chip multi-processors," 2015 IEEE 21st International On-Line Testing Symposium (IOLTS), Halkidiki, GR, 2015, pp. 110-115.

- M. A. Skitsas, C. A. Nicopoulos and M. K. Michael, "Exploring Check-Pointing and Rollback Recovery Under Selective SBST in Chip Multi-Processors," in Proc. 4th ME-DIAN Workshop, pp. 74-77, Grenoble, FR, 2015.

- M. A. Skitsas, C. A. Nicopoulos and M. K. Michael, "Exploration of system availability during software-based self-testing in many-core systems under test latency constraints," 2014 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), Amsterdam, 2014, pp. 33-39.

- M. A. Skitsas, C. A. Nicopoulos and M. K. Michael, "DaemonGuard: O/S-assisted selective software-based Self-Testing for multi-core systems," 2013 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFTS), New York City, NY, 2013, pp. 45-51.

- M. A. Skitsas, C. A. Nicopoulos and M. K. Michael, "Toward Selective Software-Based Self-Testing in Multi-Core Microprocessors," in Proc. 1st MEDIAN Workshop, pp. 71-76, Annecy, FR, 2012.

# **Contents**

| 1 Introduction |                       |                                                     | 1  |

|----------------|-----------------------|-----------------------------------------------------|----|

|                | 1.1                   | Thesis Objectives                                   | 3  |

|                | 1.2                   | Self-Testing of Multi-Core Microprocessors          | 4  |

|                | 1.3                   | System Recovery in the Presence of Permanent Faults | 5  |

|                | 1.4                   | Contributions                                       | 5  |

|                | 1.5                   | Thesis Outline                                      | 6  |

| 2              | Stat                  | e-of-the-Art Overview                               | 9  |

|                | 2.1                   | Taxonomy of On-line Fault Detection Methods         | 9  |

|                | 2.2                   | Non-Self-Test-based Methods                         | 10 |

|                | 2.3                   | Self-Test-based Methods                             | 12 |

|                |                       | 2.3.1 Hardware-based Methods (BIST)                 | 13 |

|                |                       | 2.3.2 Software-based Methods (SBST)                 | 14 |

|                |                       | 2.3.3 Hybrid Methods (HW/SW)                        | 16 |

|                | 2.4                   | Work Related to this Thesis                         | 17 |

| •              | D.                    |                                                     | 21 |

| 3              | DaemonGuard Framework |                                                     |    |

|                | 3.1                   | Software Level Implementation                       | 22 |

|                |                       | 3.1.1 Deamon-Based Test Programs (Test Daemons)     | 22 |

|                |                       | 3.1.2 Testing Manager Process                       | 23 |

|                |                       | 3.1.3 Recovery Management and Support               | 24 |

|                | 3.2                   | Hardware Level                                      | 24 |

|                |                       | 3.2.1 Hardware Support                              | 25 |

|                |                       | 3.2.2 Shared Memory                                 | 25 |

|                | 3.3                   | Impact of DaemonGuard Framework                     | 26 |

|                | 3.4                   | DaemonGuard Framework: a Profiling Exercise         | 27 |

| 4                | Sele | ctive SB | ST for Shared-Memory Multicore Systems                    | 31              |

|------------------|------|----------|-----------------------------------------------------------|-----------------|

|                  | 4.1  | Introdu  | action                                                    | 32              |

| 4.2 Related Work |      | Related  | d Work                                                    | 33              |

|                  | 4.3  | Daemo    | onGuard Framework for Selective SBST                      | 34              |

|                  |      | 4.3.1    | Daemon-Based Selective SBST - Test Daemons                | 36              |

|                  |      | 4.3.2    | The Testing Manager O/S Process                           | 36              |

|                  |      | 4.3.3    | Hardware support                                          | 37              |

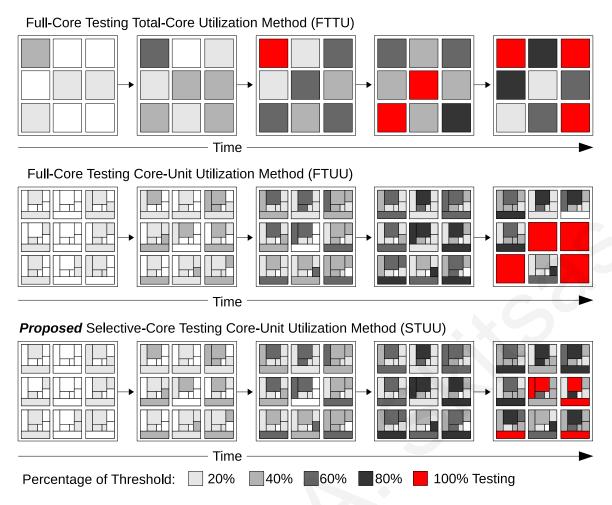

|                  | 4.4  | Propos   | ed selective testing based on functional-unit utilization | 38              |

|                  | 4.5  | Experi   | mental Framework and Results                              | 41              |

|                  |      | 4.5.1    | Evaluation framework                                      | 41              |

|                  |      | 4.5.2    | Impact of the DaemonGuard Framework                       | 42              |

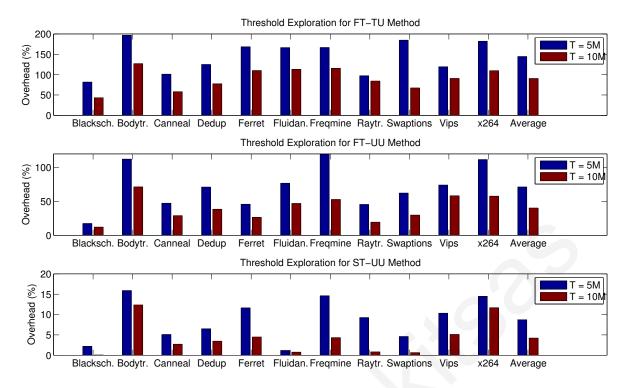

|                  |      | 4.5.3    | Evaluation results of Utilization-Based Selective SBST    | 44              |

|                  | 4.6  | Conclu   | ding Remarks                                              | 47              |

| 5                | Coal | ho Arror | re Selective SBST                                         | 49              |

| 3                | 5.1  |          | action                                                    | <b>49</b><br>49 |

|                  | 5.2  |          | Aware Selective SBST                                      | 50              |

|                  | 5.3  |          | mental Framework and Evaluation                           | 55              |

|                  | 5.5  | 5.3.1    | Evaluation framework                                      | 55              |

|                  |      | 5.3.2    | Evaluation results of the <i>cache-aware</i> DaemonGuard  | 33              |

|                  |      | 3.3.4    | mechanism                                                 | 57              |

|                  | 5.4  | Conclu   | dding Remarks                                             | 59              |

|                  | J.T  | Concid   | dung remarks                                              | 37              |

| 6                | Opti | imizing  | System Availability during SBST                           | 61              |

|                  | 6.1  | Introdu  | action                                                    | 62              |

|                  | 6.2  | Related  | d Work                                                    | 63              |

|                  | 6.3  | Definit  | ions and Framework Overview                               | 64              |

|                  | 6.4  | Test-So  | cheduling Exploration                                     | 67              |

|                  |      | 6.4.1    | Parameters affecting the testing process                  | 67              |

|                  |      | 6.4.2    | Scheduling policies                                       | 68              |

|                  |      | 6.4.3    | Optimization                                              | 70              |

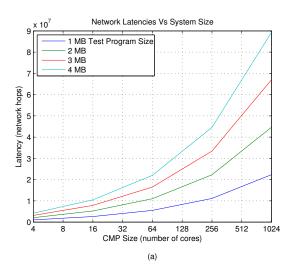

|                  |      | 6.4.4    | Scaling to many-core systems: a clustering approach       | 71              |

|                  | 6.5  | Experi   | mental Framework and Results                              | 73              |

|                  |      | 651      | Evaluation Framework                                      | 73              |

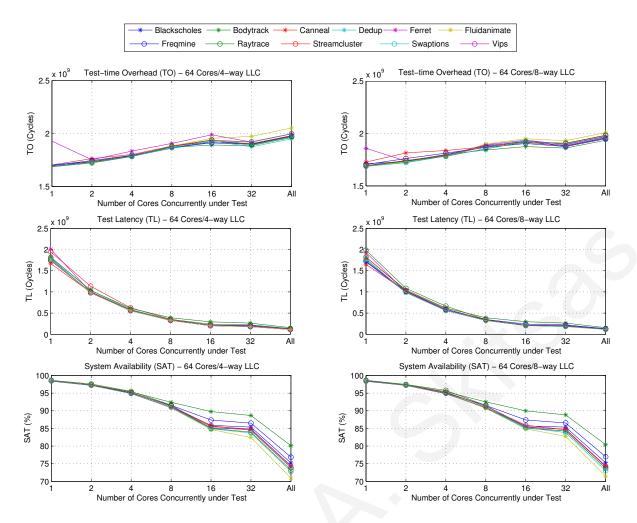

|   |      | 6.5.2    | Exploration Results                                  | 75 |

|---|------|----------|------------------------------------------------------|----|

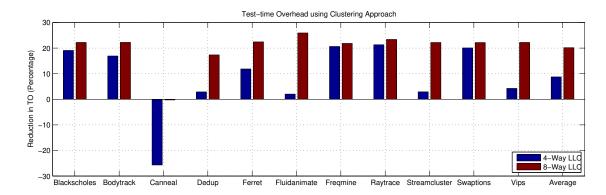

|   |      | 6.5.3    | Evaluating the Clustering Approach                   | 79 |

|   | 6.6  | Conclu   | nding Remarks                                        | 81 |

| 7 | Syst | em Rec   | overy in the Presence of Faults                      | 83 |

|   | 7.1  | Introdu  | action                                               | 83 |

|   | 7.2  | Genera   | al Framework for Fault Detection & Recovery          | 85 |

|   |      | 7.2.1    | Fault Detection                                      | 86 |

|   |      | 7.2.2    | Fault Recovery                                       | 87 |

|   |      | 7.2.3    | System Reconfiguration                               | 87 |

|   | 7.3  | The Pr   | roposed Recovery Mechanism                           | 88 |

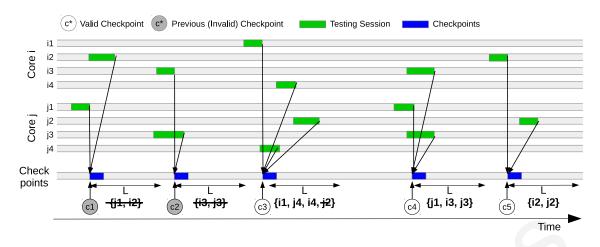

|   |      | 7.3.1    | Reducing the Number of Checkpoints                   | 88 |

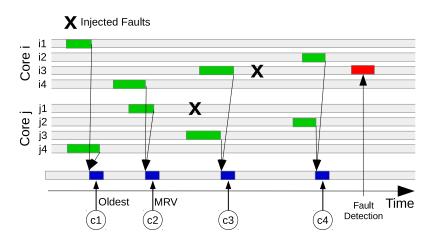

|   |      | 7.3.2    | Identifying the Most-Recently Valid (MRV) Checkpoint | 90 |

|   | 7.4  | Experi   | mental Results                                       | 93 |

|   | 7.5  | Conclu   | nding Remarks                                        | 95 |

| 8 | Con  | clusions |                                                      | 97 |

|   | 8.1  | Future   | Work                                                 | 99 |

# **List of Figures**

| 1.1 | Thesis Overview                                                                 | 6  |

|-----|---------------------------------------------------------------------------------|----|

| 2.1 | Taxonomy of on-line fault detection methods                                     | 10 |

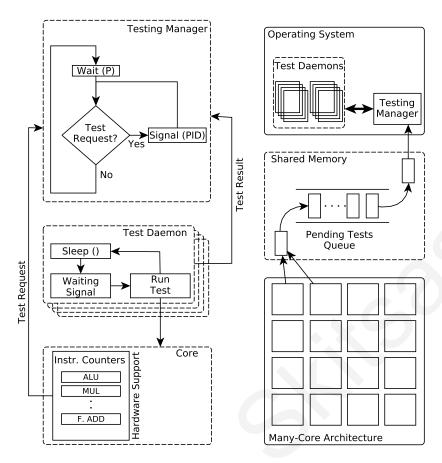

| 3.1 | A high-level overview of the DaemonGuard Framework                              | 22 |

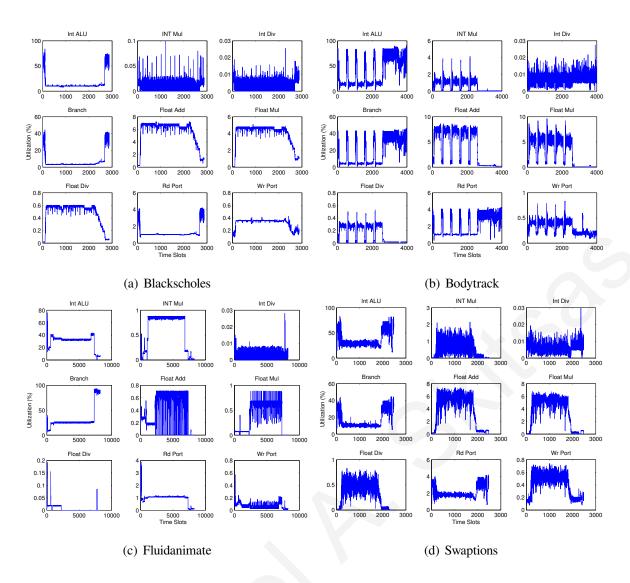

| 3.2 | Profiling experiments of CPU utilization using PARSEC benchmarks                | 28 |

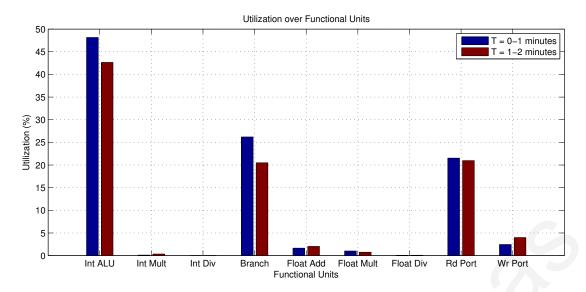

| 3.3 | Utilization of each functional unit for one minute period                       | 29 |

| 4.1 | Architectural overview of the DaemonGuard Framework for selective SBST .        | 35 |

| 4.2 | Abstract illustration of the three examined testing methodologies               | 38 |

| 4.3 | Exploring the impact of the testing threshold $T$                               | 45 |

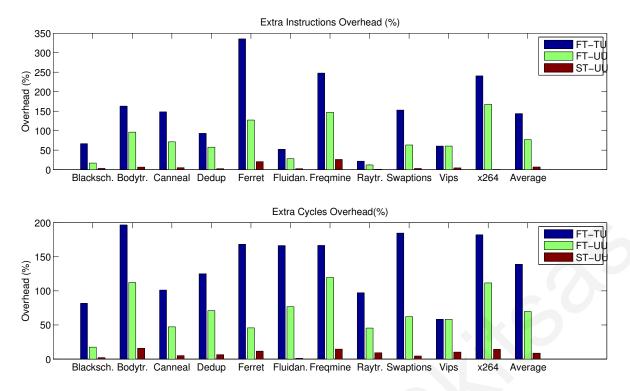

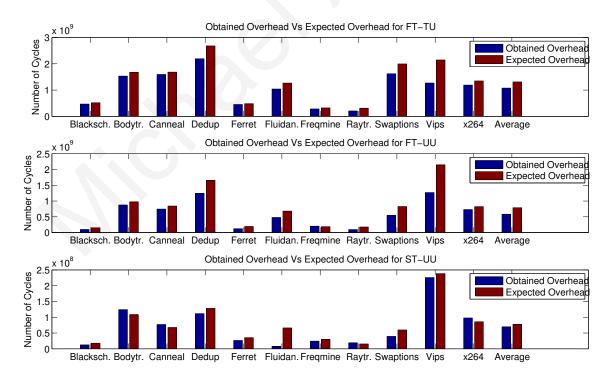

| 4.4 | The testing overhead imposed by the three testing methodologies across all      |    |

|     | benchmarks                                                                      | 46 |

| 4.5 | A comparison between the obtained testing overhead incurred – in terms of       |    |

|     | extra cycles needed – and the <i>expected</i> overhead                          | 46 |

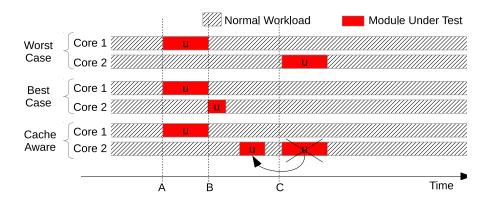

| 5.1 | An abstract example of how cache awareness can benefit the testing process      | 52 |

| 5.2 | A high-level overview of the enhanced – cache-aware – DaemonGuard frame-        |    |

|     | work                                                                            | 53 |

| 6.1 | Architectural overview of the employed framework                                | 65 |

| 6.2 | A high-level statistical analysis investigating the on-chip network latency (in |    |

|     | terms of network hops) as the number of on-chip cores in the CMP increases.     | 71 |

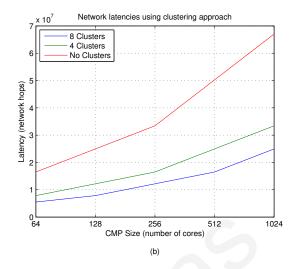

| 6.3 | The results of the 16-core CMP system for all examined PARSEC benchmarks.       | 77 |

| 6.4 | The results of the 64-core CMP system for all examined PARSEC benchmarks.       | 78 |

| 6.5 | An overview of the savings obtained when using the clustering approach          | 81 |

| 7.1 | An example scenario of the proposed check-pointing system, assuming the use     |    |

|     | of selective SBST to detect the presence of permanent faults                    | 89 |

| 7.2 | An example of the use of the MRV algorithm, which reduces the roll-back       |    |

|-----|-------------------------------------------------------------------------------|----|

|     | recovery penalty.                                                             | 92 |

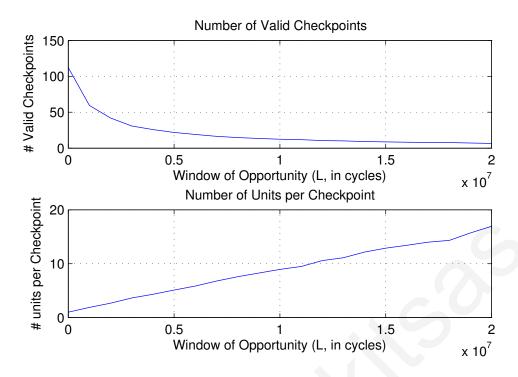

| 7.3 | Reduction of the number of stored checkpoints by applying the proposed mech-  |    |

|     | anism varying the Window of Opportunity                                       | 93 |

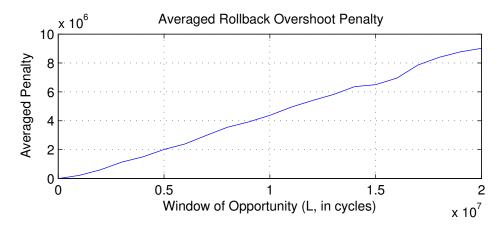

| 7.4 | The average distance between the checkpoint capture time and the time where   |    |

|     | a testing session is completed for the units that are appended to an existing |    |

|     | checkpoint                                                                    | 94 |

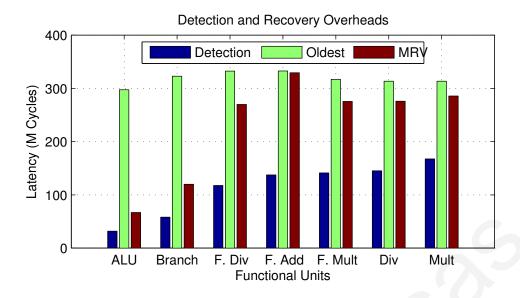

| 7.5 | Detection and recovery overhead. The results are averaged over several fault  |    |

|     | injection experiments                                                         | 95 |

# **List of Tables**

| 2.1 | High-level comparison of relevant online testing techniques                         | 18 |

|-----|-------------------------------------------------------------------------------------|----|

| 4.1 | Simulated system parameters                                                         | 40 |

| 4.2 | The execution times and memory footprints of the employed unit-specific test        |    |

|     | programs                                                                            | 41 |

| 4.3 | Details of the PARSEC benchmark applications used in our evaluation frame-          |    |

|     | work                                                                                | 42 |

| 4.4 | Impact of the DaemonGuard Framework on System Performance, $P=750K$                 |    |

|     | cycles                                                                              | 43 |

| 5.1 | The execution times and memory footprints of the, <i>memory-intensive</i> test pro- |    |

|     | grams used to assess the enhanced, cache-aware DaemonGuard framework                | 56 |

| 5.2 | Testing overhead results of the cache-aware DaemonGuard mechanism                   | 57 |

| 5.3 | The number of test-program-related LLC misses incurred by the three evalu-          |    |

|     | ated testing mechanisms                                                             | 58 |

| 6.1 | Simulated system parameters                                                         | 74 |

| 6.2 | The number of cycles needed to run the test program on the pilot core and           |    |

|     | remaining cores                                                                     | 79 |

| 6.3 | Per-core Time-test Overhead (TO) assuming a 64-core CMP being tested with           |    |

|     | and without the clustering approach.                                                | 80 |

## Chapter 1

## Introduction

The era of nanoscale technology has ushered designs of unprecedented complexity and immense integration densities. Billions of transistors now populate modern multi-core microprocessor chips and the trend is only expected to grow, leading to single-chip many-core systems [1]. However, a side effect of this deep technology scaling is the exacerbation of the vulnerability of systems to unreliable components [2]. Beyond the static variation of transistors that can occur during the fabrication, which is expected to get worse, current and future technology also suffers from dynamic variations. Single-event upsets (soft errors) are another source of concern with a direct impact on the system's reliability. Finally, a third source of unreliable hardware operation that can lead to permanent system failures is the increased sensitivity to aging (time-dependent device degradation) and wear-out artifacts, due to the extreme operating conditions.

The issue of increased vulnerability and the expected increase in the occurrence of transient and permanent failures – as a result of future technologies – render the one-time factory testing of the system inadequate. The new state of affairs necessitates the use of mechanisms that can enable protection against undesired system behavior by facilitating detection, mitigation, and/or recovery from faults throughout the lifetime of the system [3]. Several fault detection techniques have been proposed in order to detect faults during the normal lifetime of the chip. Such schemes broadly fall into two categories: (a) Concurrent methods relying on fault-tolerant mechanisms (i.e., redundancy techniques) [4], and (b) Non-concurrent periodic on-line testing [5], which aims to detect errors that are, subsequently, addressed using various techniques.

Multi-/many-core microprocessor chips with an abundance of identical computational resources would appear to be ideal for implementing high availability solutions on-chip, due to the inherent replication of resources (i.e., the processing cores). Multi-core systems should

remain operational despite the occurrence of permanent and/or transient faults. Detection and diagnosis of such fautls constitute the first and perhaps the most important step towards the implementation of self-healing multi-core systems. The already proposed self-testing techniques for simple and even more complex microprocessors have matured enough, while current and future trends in the self-testing research area are adapting these techniques to multi-/many-core processors. Considering the huge range of today's applications that require many and different types of computational systems, researchers aim to develop self-testing techniques targeting either general-purpose multi-core microprocessors, or embedded microprocessors and microcontrollers that constitute application-specific Systems-on-Chip (Soc).

Non-concurrent periodic online testing is one methodology used traditionally for the detection of permanent faults (hard failures). Moreover, it can be used for circuit failure prediction within the cores of modern microprocessors, due to either infant mortality reasons (early-life failures), or aging-related factors [6–10]. Hardware-based schemes, typically using Built-In Self-Testing (BIST) [11], as well as software-based schemes, known as Software-Based Self-Testing (SBST), can be employed for this problem. The SBST technique [12–20] is an emerging new paradigm in testing that avoids the use of complicated dedicated hardware for testing purposes. Instead, SBST employs the existing hardware resources of a chip to execute specific (software) programs that are designed to test the functionality of the processor. The test routines used in this technique are executed as normal programs by the CPU cores under test. As a result, the major cost of SBST is the *time* overhead incurred by the execution of the appropriate test routines on the CPU. The hardware overhead is either non-existent, or negligible, and no Instruction Set Architecture (ISA) extensions are required.

Beyond the detection of faults, modern systems must be enhanced with mechanisms able to self-repair and recover the system to a fault-free state, in order to remain functional despite the presence of permanent faults. To maintain proper operation of the system, several error recovery techniques have been proposed. These techniques are classified mainly in two categories: (i) Forward Error Recovery (FER), and (ii) Backward Error Recovery (BER). In the first (FER), the usage of redundant hardware is necessary for error detection and recovery. On the other hand, BER requires to store a fault-free state of the system using checkpoints for error recovering. Once an error is detected, the system is able to rollback to the fault-free state and re-execute the affected workload, assuming it supports reconfiguration/fault-containment capabilities to rule out the malfunctioning component. In most cases, BER does not require extra hardware to support the recovery procedure, and the imposed overhead is in execution time, since a portion of the executed workload needs to be re-executed. There is also some

## 1.1 Thesis Objectives

The objectives of this thesis are to develop techniques for: (a) on-line fault detection, specifically SBST methodologies for multi-core systems in order to reduce the imposed testing overhead during testing and to increase the system availability by proposing test scheduling policies, and (b) efficient check-pointing and roll-back mechanisms to assist recovery in the presence of permanent faults. Combining the proposed techniques we aim to develop a dependable system able to tolerate permanent hardware failures encountered during the normal operation of manycore architectures. The first part of this thesis introduces a new paradigm of SBST that performs testing at the granularity of individual microprocessor core components in multi-/many-core systems based on the utilization. This thesis, is the first work that proposed and implemented selective testing. The second part investigates the relation between system test latency and test time overhead under several scheduling policies targeting large systems in terms of number of cores. As a result, we aim to identify the best scheduling policy that increases system availability under a given test latency constraint. Both the on-line fault detection approaches are deployed and evaluated under a real environment using a unix based OS (Solaris) targeting a SparcV9 multi-core architecture. Finally, in the third and last part of this thesis, we enhanced our framework to support fault recovery in the presence of permanent faults.

For the development of the above techniques, we proposed the DaemonGuard Framework, a light-weight, minimally-intrusive framework, which transparently orchestrates the procedure of SBST and accommodates algorithms for the creation of checkpoints and to support the recovery to a fault-free state. The basic DaemonGuard Framework is generic enough and can support different techniques for SBST as well as test programs that target hardware components of a multi-core system at different granularities (i.e. core level, functional unit). The DaemonGuard Framework comprises an always-active OS process (the Testing Manager) and a number of dormant daemons (the test routines), which are awakened according to the implemented technique.

The developed framework in this thesis can be considered as an flexible tool for the scientific community with research interests in the area of self-testing and specifically the SBST. The ability to monitor the system's activity and provide a real-time feedback of the "health" of the system's module combined with the O/S resident processes for testing can help research groups to easily implement, deploy and evaluate new SBST techniques. Besides the scientific

community, the concept of DaemonGuard Framework can be adopted by different industry sectors (i.e automotive industry) towards a low cost reliable solution.

## 1.2 Self-Testing of Multi-Core Microprocessors

The main purpose of this thesis is to provide new approaches for self-testing of multi-core microprocessors. The existing SBST approaches are mainly focused on the development of test programs that are periodically applied at microprocessors. The first part of our research activity, focuses to the reduction of imposed testing overheads from the execution of test programs during the normal operation of systems. The motivation of this approach is to perform test based on the utilization by avoiding testing under-utilized components. To achieve the utilization-based SBST, the individual cores of a multi-core system are divided in several functional units that can be tested independently. This allows us to perform selective testing on the high-utilized functional units.

To achieve this, we utilize the DaemonGuard Framework to enable the real-time observation of individual sub-core modules and the initiation of on-demand selective testing. For this approach, the main component of the DaemonGuard Framework is the Testing Manager software process, which is responsible for the invocation of the various Test Daemons (test programs targeting individual functional units of each core of the system), based on the utilization information provided by hardware instruction counters residing alongside each functional unit within the CPU cores. The main function of the Testing Manager is the checking for pending test requests by any functional unit of any core within the system. Furthermore, the DaemonGuard mechanism is able to exploit the memory hierarchy of the CPU to expedite the testing process. DaemonGuard is augmented with the capability to perform *cache-aware* selective testing, whereby test sessions are initiated not only based on unit utilization, but also on the recent history of test sessions by other similar units in other cores. Consequently, test programs can benefit from cache-resident blocks, thereby avoiding the need for many expensive off-chip memory accesses.

In order to provide a comprehensive framework for the orchestration of testing activity under multi-core systems, a different approach of SBST is also investigated in this thesis. In particular, we investigate the impact of SBST for shared-memory multi-core systems in cases where the need for testing the entire system is necessary. One salient aspect of on-line self-testing is the scheduling of the test programs during a testing session. For the second part of this thesis, we proposed to investigate scheduling methodologies aiming to increase system

availability during testing. The main focus is to investigate the intricate relationship between the test latency and the test-time overhead under different test scheduling policies. We are motivated to study this problem, because, in shared memory systems, the time overhead of SBST for each core is affected by potential test program content already resident in the Last Level Cache as a result of a previous core's testing session.

## 1.3 System Recovery in the Presence of Permanent Faults

For the last part of this thesis, an enhancement of DaemonGuard Framework to support fault recovery capabilities is proposed. When a testing session is completed, during selective testing, a checkpoint that holds the fault-free state of the system must be captured. Since the considered detection mechanism performs on-demand testing at sub-core granularity, checkpoints are captured and stored in the system at irregular time intervals. As a result of this, we are motivated to investigate techniques that aim to solve the problems arising by the application of recovery policy over selective testing.

The main focus of this thesis is the system recovery process, once a permanent fault has been detected. Hence, a recovery mechanism is introduced, which is able to keep the system operational despite the occurrence of permanent faults. The main components of the proposed recovery mechanism are (a) the Checkpoint Manager, and (b) the Recovery Manager, which are responsible, respectively, for the creation of system checkpoints and determining a valid checkpoint (among the multiple stored ones) to roll back.

After the detection of a permanent fault and the subsequent recovery to a fault-free state, the system should be able to isolate the faulty module and reconfigure itself to a fault-free (albeit degraded) operational mode. We assume that the operating system is aware of the reconfiguration policy and, upon rollback, it is able to re-distribute the workload to the fault-free (and still active) cores, and resume execution from the selected checkpoint. Note that the reconfiguration mechanism is beyond the scope of this thesis.

#### 1.4 Contributions

The contributions of this thesis are:

The Development of DaemonGuard Framework, a light-weight framework that can enable SBST from the O/S level. The modular and scalable design of this framework allows the accommodation and evaluation of different SBST approaches.

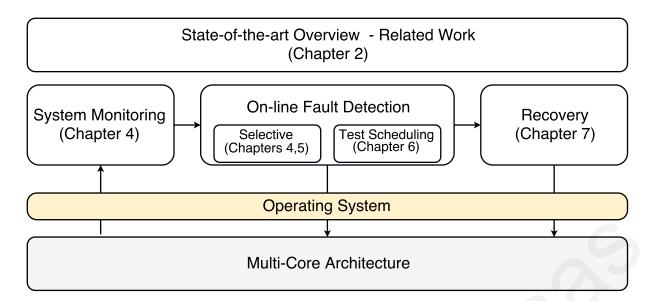

Figure 1.1: Thesis Overview

- The Utilization-Based Selective SBST contributes to the substantial reduction in testing overhead by avoiding the testing of non-utilized functional units.

- A further improvement of Selective SBST, by considering the Cache-Aware Selective

Testing. Testing sessions are initiated not only on utilization statistics per unit, but considering the recent activity of testing in order to exploit the cache-resident blocks of test

data.

- Optimization of test scheduling process in order to minimize the test-time overhead and maximize the system availability.

- A clustering approach of selecting the cores under test is proposed in order ensure the reduction in test-time overheads while the system scales up.

- An efficient checkpointing and roll-back recovery mechanisms for systems that perform on-demand testing on a specific part of the system (i.e. Selective SBST).

#### 1.5 Thesis Outline

The outline of this thesis is illustrated in Figure 1.1. Chapter 2 presents a review of state-of-the-art techniques and methodologies for the self testing of multi-core processors. In Chapter 3 we present the DaemonGuard Framework by describing the most important components. Details about a series of simulation experiments in order to acquire statistics about the executed instructions per functional unit within a core by the application of several benchmarks is also

presented in Chapter 3. Chapter 4 introduces the Selective SBST while Chapter 5 presents the cache-aware selective SBST approach. Test scheduling techniques and optimization of system availability is presented in Chapter 6. In Chapter 7, we propose mechanisms to support recovery in the presence of permanent faults. Finally, in Chapter 8 we present the concluding remarks and future work.

## Chapter 2

## **State-of-the-Art Overview**

## 2.1 Taxonomy of On-line Fault Detection Methods

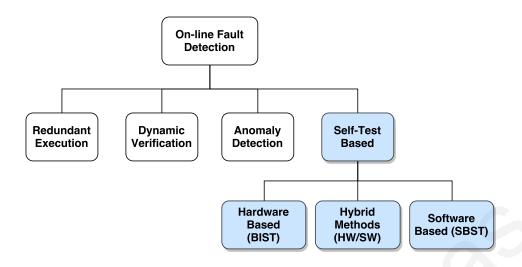

Over the last several years, several self-testing approaches have been proposed towards reliable and dependable multi-core microprocessor systems. Considering the implementation details as well as the architectural level of application, on-line fault detection techniques can be classified in four main categories [3]. Figure 2.1 presents a tree diagram of the taxonomy of on-line fault detection methodologies can be classified are: (a) *redundant execution* where the exploitation of "spare" processing elements (i.e. cores) for the replication of normal workload can lead to the detection of failures, (b) *dynamic verification* where the fault detection is based on the validation of program invariants during runtime, (c) *anomaly detection* where the system is monitored for the detection of symptoms of faults, and (d) the *Self-Test-based* techniques where the on-line fault detection is done by the application of test patterns. Based on the level of implementation and the way that faults are detected in each category, the first three categories can be considered as a Non-Self-Test-based approaches as well.

The main characteristic of Non-Self-Test-based methods is that the detection of faults is achieved by exploiting the normal workload that is applied in the system. As a result of these approaches, in fault-free executions the imposed performance overheads in normal workloads is almost zero while hardware overhead exists either using additional hardware components (i.e. using checkers) or by increasing (i.e. doubling) the resources for the execution of the workload (i.e redundant execution). In Self-Test-based techniques, the detection of faults is achieved by the application of test patterns either by using hardware support (i.e. scan chains), in hardware-based techniques, or by exploiting the available resources and ISA, in software-

Figure 2.1: Taxonomy of on-line fault detection methods

based techniques.

During self-testing, test patterns are applied in a periodic manner where the normal operation of module under test (i.e. core) is suspended and turned into testing mode. As a result of this, Self-Test-based approaches imposed performance overheads in the system. In the era of multi-/many-core architectures with multiple homogeneous cores appearing in the same chip, despite the suspension of the normal operation of the core under test, the entire system remain operational as normal workload can be scheduled in one of the remain available resources.

## 2.2 Non-Self-Test-based Methods

A fault detection approach targeting microprocessor cores is to run two identical copies of the same program (different executions either at the thread or process levels) and compare their outputs. Redundant execution is feasible both at the hardware level and the software level. In the era of multi-/many-core architectures with multiple homogeneous cores integrated on the same chip, and the capability to execute multiple threads (or processes) simultaneously, the hardware-based redundant techniques (such as Dual/Triple Modular Redundancy, DMR, TMR) can be applied with significantly reduced performance overheads, targeting both transient and permanent faults. The application of these hardware-based redundant techniques is feasible because of the rather improbable simultaneous utilization of all the processing resources at any given time. In literature, two forms of redundant techniques at hardware level can be found the structural redundancy (lockstep configuration) and temporal redundancy (redundant multi-threading).

In the former, identical cores are working in close synchronization either at instruction level or even more at cycle level. Aggarwal et al. [21] propose DMR and TMR configurations for CMPs which provide error detection and error recovery through fault containment and component retirement. LaFrieda et al. [22] presents a dynamic core coupling (DCC) technique that allows arbitrary CMP cores to verify each other's execution. Unlike existing DMR techniques that require a static binding of adjacent cores via dedicated communication channels and buffers, the proposed technique avoids the static binding of cores. Li et al. [23] proposed a variation-aware core-level redundancy scheme in order to achieve robust computation in many-core systems with inter-core variations and mixed workloads.

Several Redundancy Multi-Threading (RMT) techniques have been proposed targeted single-core chips that support Simultaneously Multi-Threading (SMT) [24,25]. The evolution of technology and the era of multi-core systems forced researches to develop techniques exploiting the nature of Chip Multi-Processors. Mukherjee et al. [26] studied RMT techniques in the context of both single- and dual-processor simultaneous multi-threaded (SMT) propose a Chip-level Redundant Threading (CRT) for CMP architectures. [27] present a Software-based Redundant Multi-Threading (SRMT) approach for transient fault detection targeting general-purpose chip multi-processors (CMPs). Furthermore, Chen et al. [28] explores how to efficiently assign the tasks onto different cores with heterogeneous performance properties in order to achieve high reliability and satisfy the tolerance of timeliness. Mitropoulou et al. [29] proposes a compiler-based technique that makes use of redundant cores within a multi-core system to perform error checking.

As we mentioned, redundant execution techniques can be found at software level as well. In this case, the redundant execution of workload at different architectural levels (i.e. instruction, thread, process) is based on the re-execution at the same resources. As a result, redundant techniques at this level can only detect transient faults. Oh et al. [30] propose a pure software technique Error Detection by Duplicated Instructions(EDDI) that duplicates instructions during compilation and uses different registers and variables for the new instructions. Reis et al. [31] present SWIFT, a novel, software-only, transient fault detection technique. Recently, Mushtaq et al. [32] propose an error detection mechanism that is optimized to perform memory comparisons of the replicas efficiently in user-space. Kuvaiskii et al. [33] present HAFT, a fault tolerance technique using hardware extensions of commodity CPUs to protect unmodified multi-threaded applications against such corruptions. HAFT utilizes instruction-level redundancy for fault detection and hardware transactional memory for fault recovery.

The second category of on-line fault detection in the considered taxonomy is the **Dynamic**

**Verification**. The operation of this approach is based on the run-time verification of specific invariants that in a fault free execution are true. The verification is based on dedicated hardware checkers. The research challenge within these approaches beyond to maintain a low-cost in terms of hardware implementations, is to provide a comprehensive set of invariants aiming to increase the detected faults. Dynamic Verification was first introduced by Todd Austin in [34], where a novel micro-architecture based technique that permits detection and recovery of all transient and permanent faults in the processor core is proposed. DIVA, a Dynamic Implementation Verification Architecture,) uses a simple checker core to detect errors in a speculative, super-scalar core. Despite, the low-cost implementation requirements compared with a complex super-scalar core, in multi-core systems with simpler microprocessors the overhead becomes significant. Meixner et al. [35] proposes Argus, a low-cost, comprehensive fault detection targeting simple cores. Based on dynamic verification, Argus uses four invariants that guarantee the correct operation of a core, control flow, computation, dataflow and memory. Additionally, Meixner and Sorin [36] proposes the Dynamic Dataflow Verification (DDFV) another approach of dynamic verification using a high-level invariant. Fault are detected by verifying at runtime the dataflow graph.

The last category of Non-Self-Test-based approaches is the **Anomaly Detection** where that faults are detected by monitoring the software for anomalous behavior or symptoms of faults. According the level of symptoms that can detect, anomaly detection approaches can be further classified in three categories [3], (a) those that detect data value anomalies, (b) those that detect micro-architectural behavior anomalies, and (c) those that detect software behavior anomalies. Racunas et al. [37] dynamically predict the valid set of values that an instruction will produce, and consider a departure from this prediction as a symptom of a (transient) fault. Wang and Pater [38] detect transient faults without signification overhead by utilizing symptom. Feng et al. [39] in Shoestring, enhance ReStore by selectively duplicating some vulnerable instructions with simple heuristics. Li et al. [40] propose the detection of faults by deploying low overhead monitors for simple software symptoms at the operating system level. Their approach is rely on the premise that micro-architectural structures eventually propagate symptoms to the operating system.

#### 2.3 Self-Test-based Methods

The last category of the considered taxonomy is the **Self-Test-based Methods** where the detection of faults is based on the application of test patterns. Based on the architectural level

of implementation and application of test patterns, Self-Test-based methods are further classified in three categories: (i) the Hardware-based methods, known as Built-In Self-Test (BIST), where self-testing is maintained by hardware components, (ii) Software based methods, known as Software-Based Self-Testing (SBST) where the application of test patterns in done using software programs, and (iii) the hybrid approaches where self-testing is supported both by hardware level and software level.

#### **2.3.1** Hardware-based Methods (BIST)

Built-In Self-Test (BIST) approaches can, theoretically, perform non-concurrent error detection of microprocessors during their entire lifetime. Hardware-based BIST exploits special circuits located on the chip that produce, monitor, and evaluate the tests needed by the cores. Traditionally, BIST techniques are used for manufacturing testing, but the advances in technology necessitates the application of such techniques during the lifetime and normal operation of the system targeting wear-out and aging-related faults.

Shyam et al. [41] utilize existing distributed hardware BIST mechanisms to validate the integrity of the processor components in an on-line detection strategy. For each of the pipeline components, a high quality input vector set is stored in an on-chip ROM, which is fed into the modules during idle cycles. A checker is also associated with each component to detect any defect in the system.

Li et al. [42] present CASP, Concurrent Autonomous chip self-test using Stored test Patterns, is a special kind of self-test where a the system tests itself during normal operation without any downtime visible to the end-user. The operation of CASP is based on two main functions: (i) the storage of very thorough test patterns in non-volatile memory, and (ii) the architectural and system-level support for autonomous testing of one or more cores in a multi-core system without suspend the normal system operation. The testing procedure under CASP solution is composed by four phases: (1) the test scheduling where one or more cores may be selected for testing, (2) the pre-processing phase where the core under test is temporarily isolated saving the current state, (3) the testing where test patterns are loaded and applied to the core under test and finally, (4) restore the state and resume the operation of tested core. The evaluation of the proposed technique is done using the OpenSPARC T1 multi-core processors where a fault coverage more than 99% using 5MB of stored patterns is achieved.

Lee et al. [43] propose a novel self-test architecture which achieves high fault coverage by using deterministic scan-based test patterns. The main idea of this work is the compression and

storage on the chip while the decompression and application to the circuits under test will take place during the testing. As the testing is performed based on deterministic patterns, pseudorandom patterns are not required and this results in the reduction of testing time. Experimental results on OpenSPARC T2, a publicly accessible 8-core processor containing 5.7M gates, show that all required test data for 100% testable stuck-at fault coverage can be stored in the scan chains of the processor with less than 3% total area overhead for the whole test architecture.

#### 2.3.2 Software-based Methods (SBST)

The SBST technique is an emerging new paradigm in testing that avoids the use of complicated dedicated hardware for testing purposes. Instead, SBST employs the existing hardware resources of a chip to execute normal (software) programs that are designed to test the functionality of the processor itself. The test routines used in this technique are executed as normal programs by the CPU cores under test. The processor generates and applies functional-test programs using its native instruction set. In recent years, several active research teams have been working in the area of SBST focusing on different approaches. The two main phases of SBST towards the detection of a fault are (a) the test-program development, and (b) the execution of the test program on the system.

**Test program development for multi-core architectures** Several research teams are working on the development of test programs with multi-dimensional scope, such as to increase the fault coverage, extend the considered fault models (i.e., to also include delay faults), reduce the test-program size, achieve savings in testing time overhead, etc. More recently, in the age of chip multiprocessors and multi-threading, the development of test programs also focuses on the effective adoption of the underlying hardware to yield self-test optimization strategies that benefit from the targeted architectures.

Foutris et al. [14] propose a Multi-Threaded Software-Based Self-Test (MT-SBST) SBST methodology targeting multi-threaded multi-core architectures. The proposed MT-SBST methodology generates an efficient multi-threaded version of the test program and schedules the resulting test threads into the hardware threads of the processor to reduce the overall test execution time and on the same time to increase the overall fault coverage. MT-SBST approach significantly speeds up testing time at both the core level (3.6 times) and the processor level (6.0 times) against single-threaded execution, while at the same time it improves the overall fault coverage

Kaliorakis et al. [44] propose a test-program parallelization methodology for many-core architectures, in order to accelerate the on-line detection of permanent faults. The proposed methodology is based on the identification of the memory hierarchy parameters of many-core architectures that slow down the execution of parallel test programs in order to identify the parts that can be parallelized and therefor to improve the performance. The evaluation of the methodology in [44] is done using the Intel's Single Chip Cloud Computer showing an up to 47.6X speedup compared to a serial test program execution approach.

**Test program scheduling** One salient aspect of on-line testing and specifically of SBST is the scheduling of the test program(s). In light of the rapid proliferation of multi-/many-core microprocessor architectures, the test scheduling issue becomes even more pertinent. One approach is to periodically initiate testing on the system targeting individual cores, or all the cores simultaneously. In any case, the interruption of the current execution of normal workload is unavoidable. Another approach is the execution of test programs on cores that have been observed to be idle for some time. Recent techniques have proposed the monitoring of the utilization of the system and subsequent selection of specific cores to be tested.

Apostolakis et al. [12] proposed a methodology that allocates the test programs and test responses into the shared on-chip memory and schedules the test routines among the cores aiming at the reduction of the total test application time, and thus, test cost, for the SMP, by increasing the execution parallelism and reducing both bus contentions and data cache invalidations. The proposed solution is demostrated with detailed experiments on several multi-core systems based on OpenRISC 1200 processor.

A recent test-scheduling study for online error detection in multicore systems is discussed in [45]. The authors evaluate the performance of test programs applied on Intel's 48-core Single-chip Cloud Computer (SCC) architecture. Due to possible congestion within common hardware resources used by the various cores, the test time can be quite large with a significant impact on performance. As a result, the authors of [45] develop effective test scheduling algorithms to expedite the test process in such systems.

Skitsas et al. [46] investigate the relation between system test latency and test-time over-head in multi-/many-core systems with shared Last-Level Cache (LLC) for periodic SBST, under different test scheduling policies. The investigated scheduling policies primarily vary the number of cores in the overall system testing session. Given a constraint in test latency, the proposed methodology optimizes the test scheduling process, so as to minimize the test-time overhead and maximize system availability.

**Monitoring system activity** Recently, several techniques proposed the monitoring of system status over the time as an indicator for initiation testing procedure. Power, utilization, performance are among the metrics that are considered in the type of testing activity.

Gupta et al. [47] propose an adaptive online testing framework to significantly aiming to reduce the testing overhead. The proposed approach is based on the ability to assess the hardware health and apply detailed tests. Hardware health assessment is done using in-situ sensors that detect the progress of various wearout mechanisms. Results show a reduction in software test instructions about 80% while the sensor area overhead for a 16-core CMP system is 2.6%.

Haghbayan et al. [48] proposed a power-aware non-intrusive online testing approach for many-core systems. The proposed approach schedules software-based self-test routines on the various cores during their idle periods. The scheduler selects the core(s) to be tested from a list of candidate cores. The selection is based on a criticality metric, which is calculated considering the utilization of the cores and power budget availability.

Skitsas et al. [49] investigate the potential of SBST at the granularity of individual micro-processor core components in multi-/many-core systems. While existing techniques monolithically test the entire core, the proposed approach aims to reduce testing time by avoiding the over-testing of under-utilized units. The methodology is based on a real-time observation of individual sub-core modules and performs on-demand selective testing of only the modules that have recently been stressed. Results indicate substantial reductions in testing overhead of up to 30×.

#### 2.3.3 Hybrid Methods (HW/SW)

Beyond Self-Test-based methods that are purely implemented at one architectural level either on hardware or software, there is a different approach that spans in both architectural levels. The purpose of these hybrid approaches is to further improve the performance of self-test based methods by reducing the testing time, increasing the fault coverage, etc. The hardware architectural support provides the necessary substrate to facilitate testing, while the software makes use of this substrate to perform the testing. For the implementation of such approaches, modifications of the ISA and/or the extension of hardware components may be required.

Inoue et al [50] propose VAST, a Virtualization-Assisted concurrent, autonomous Self-Test that enables a multi-/many-core system to test itself, concurrently during normal operation, without any user-visible downtime. VAST is hardware and software co-design of on-line self-test features in a multi-/many-core system through integration of BIST (i.e. CASP) methods

with a virtualization software. Testing can be done in two ways, stop-and-test and migrate-and-test. Experimental results from an actual multi-core system demonstrate that VAST-supported self-test policies enable extremely thorough on-line self-test with very small performance impact.

Constantinides et al. [51] proposed an online testing methodology using an enhanced ISA with special instructions for fault detection and isolation. Structural tests are performed by applying test patterns using software routines. The test routines are executed periodically, after a number of executed instructions have committed, and checkpoints are used for recovery. The technique of Constantinides et al. is software-assisted, but it requires various hardware modifications. These intrusive modifications are needed, because the goal is to enable very detailed structural testing through existing scan-chain infrastructure.

A hardware and software co-design methodology for functional testing is proposed by Khan et al. [52]. The testing methodology is based on the redundancy concept, whereby two cores execute the same program and capture corresponding footprints. The results of the executions are compared for fault detection. The choice of the test program is based on profiling that can be done offline or online. In [53], the authors propose a thread relocation methodology that uses dynamic profiling based on phase tracking and prediction.

In [54], a scalable self-test mechanism for online testing of many-core processors has been proposed. Several hardware components are incorporated in the many-core architecture that distribute software test routines among the processing cores, monitor behavior of the processing cores during test routine execution, and detect faulty cores. Results indicate a good fault coverage in a limited number of test cycles while the scalability in terms of hardware and timing overhead is maintained making the application to many-core systems feasible.

#### 2.4 Work Related to this Thesis

The developed fault detection techniques under this thesis are classified in the Self-Test-based methods and particular under the Software-based methods. As the scope of this thesis is to reduce the imposed testing overheads and increase the system availability by applying the proposed test scheduling policies, the test program development is beyond the scope of this thesis. Test programs that are used in our framework are adopted from the literature and specifically for the Foutris et al [14].

As we mentioned earlier in this Chapter, several research groups are working on the development of test programs targeting processing elements at different granularities (i.e. functional

Table 2.1: High-level comparison of relevant online testing techniques.

|                                    | Selective SBST                | Full-Core Functional Testing    |      |      | Struct. Testing |           |

|------------------------------------|-------------------------------|---------------------------------|------|------|-----------------|-----------|

|                                    | (Proposed)                    | [12]                            | [14] | [52] | [59]            | [51]      |

| Test-Time Overhead                 | Low                           | High                            |      |      | Low             |           |

| Overall Fault Coverage             | N                             | Moderate to High                |      |      | Very High       |           |

| Fault Coverage per Testing Session | Unit-based                    | Core/System-based               |      |      |                 |           |

| Detection Latency                  | Low to High (based on stress) | Depends on testing period       |      |      |                 |           |

| System Avail. During<br>Testing    | Very High                     | High                            |      |      | None            |           |

| Targeted Module                    | Functional unit               | Core/System                     |      |      |                 |           |

| Test Triggering Method             | Stress-based                  | Periodic                        |      |      |                 |           |

| Frequency of Test Triggering       | High                          | Low (Depends on testing period) |      |      |                 | g period) |

| HW Support                         | Minimal                       | No                              | No   | Yes  | No              | Yes       |

| OS Modif.                          | No                            | No                              | No   | Yes  | Yes             | No        |

units, entire core). Psarakis et al. [18] discussed the role of SBST in the microprocessor test and they proposed a taxonomy for different SBST methodologies according their test program development philosophy. The efficiency of an SBST approach depends on its test program development methodology and the effectiveness of the generated test routines. Another important parameter towards the efficient development of test programs is the automation of the self-test program generation process. The field of automatic test program generation includes generic approaches targeting processor cores [55,56] or approaches targeting specific high-performance processor architectures [57,58].

The main contribution of this thesis the selective SBST where the test programs are applied at sub-core granularity (functional units) based on the utilization. Thus, an important element in this thesis is the usage of test programs that target the individual functional units of the considered architecture. Based on the literature, the most applicable test programs for our framework are those that are developed by Foutris et al. [14] targeting the functional units of a Chip Multi-Threaded (CMT) multiprocessor architecture.

Table 2.1 presents a high-level comparison of the proposed selective SBST technique to other relevant on-line testing techniques (including full-core functional testing). The main contribution of the work in this thesis is the reduction of the test-time overhead, by avoiding un-

necessary testing. As shown in Table 2.1, the "Overall Fault Coverage" of the selective and full-core testing approaches is the same. However, the limitation of selective testing is in terms of "Fault Coverage per Testing Session." The provided fault coverage of each testing session refers only to the particular functional unit under test (since only one functional unit is tested during each test session). Of course, this limitation only applies to each individual test session; once all units are tested over time, the overall fault coverage is identical to the one provided by full-core testing. Note that the under-utilized units are tested periodically. Another important parameter affected by the proposed selective testing technique is the detection latency. Since test triggering is based on utilization (or, more generally, stress), the detection latency could vary from low to high: fault detection in highly-utilized units is much faster than in under-utilized units, due to the more frequent testing sessions. Most importantly, the impact of the proposed testing approach on overall system performance is minimized by utilizing a software-based framework (with minimal hardware support), which runs seamlessly and transparently within the OS of the multi-core system.

# **Chapter 3**

## **DaemonGuard Framework**

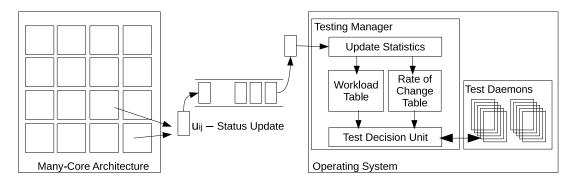

In order to enable on-line software-based self-testing, targeting either sub-core functional units or the entire core and additionally to be able to support recovery in the presence of permanent faults, we proceeded to the development and implementation of the DaemonGuard Framework. This framework is mainly constituted from test programs residing at the operating system level and during their execution are targeting on the detection of permanent fautls. On top of these test programs, another software process, that is running at O/S level as well, is responsible for the orchestration of the testing activity. In particular, The Testing Manager process initiates the execution of the test programs based on a triggering mechanism either by monitoring the activity of the system or based on a predefined time interval (periodically). For each proposed methodology under this work, the Testing Manager process is suitably adapted, i.e in selective testing the execution of test programs is driven by the utilization metrics of the functional units within the cores of the system.

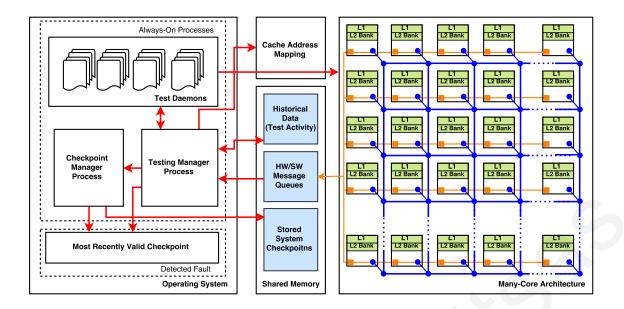

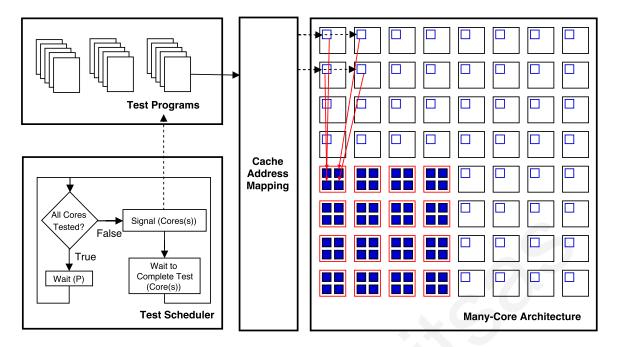

Figure 3.1 depicts a high-level overview of the DaemonGuard framework used to facilitate fault detection and recovery in a multi-/many-core setup. According to the architectural level of implementation, DaemonGuard is implemented in two levels, the Software Level residing within the O/S and the Hardware Level including the memory elements as well. The right side of the figure depicts the many-core architecture where each core of the system has its own private cache memory and is interconnected to the NoC. Additionally, with orange color are the enhancements related to the monitoring as well as the communication with message queues. Arrows with red color indicates the communication between the several components of the DaemonGuard Framework.

Figure 3.1: A high-level overview of the general framework employed in this thesis to facilitate the detection of faults (the focus is on *permanent* faults) and the recovery of the multi-/many-core system to a correct state. Correct system states are maintained in the form of checkpoints.

#### 3.1 Software Level Implementation

In DaemonGuard Framework, fault detection and recovery mechanisms are maintained by software processes that resides in the O/S with the minimum support of hardware components (i.e. for the monitoring of the system). In this section, we are presenting an overview of those software processes that form the fault detection mechanisms, the Test Daemons that are responsible to apply test patterns over the functional components of a core and the Testing Manager process mainly responsible for the invocation of Test Daemons. Additionally, in order to assist the recovery procedure upon the detection of a permanent fault, two software processes are running at the O/S level as well. The first process is responsible for the creation of checkpoints (a fault free state of the system) and the second, implements an algorithm for the selection of a valid checkpoint for recovery.

#### **3.1.1** Deamon-Based Test Programs (Test Daemons)

In multitasking computer operating systems, daemons are programs that run as background processes without any interaction at the user level. Daemons can be characterized as common processes; i.e., they have a Process ID (PID) and all operations pertaining to processes – such as the sleep function and various signals – can be applied. Daemon programs are loaded onto the system once, when the operating system starts up, and they run continuously during the

normal operation of the system. In the most cases, daemons are idle processes waiting for an appropriate signal, or interrupt, in order to become active and perform their task(s). An example of such OS daemon is the *printer server* in unix-based operating systems. The daemon is loaded and executed during the startup phase of the operating system and runs continuously in the background (in idle mode) while waiting for a job to print.

For the purposes of this work, the test programs are normal OS processes that run in the same way as normal applications. As a result, the isolation of test programs is facilitated by the operating system through context switching, whereby the state of a process is stored and restored on-demand, and the execution of both test programs and normal workloads is seamlessly time-multiplexed on the system. Hence, it is the OS that handles the scheduling and isolation of test programs, since the latter are normal OS processes.

#### 3.1.2 Testing Manager Process

The basic component of the DaemonGuard framework is the Testing Manager process which is responsible for the invocation of the various test daemons based on each consider self-testing methodology. Just like all the other other processes running during normal system operation, the O/S is responsible to schedule the Testing Manager process as well. The ability of the implementation of different algorithms (i.e. scheduling policies) for the orchestration of self-testing in multi-core systems is one of the characteristics of Testing Manager. This and the possibility to exploit information by monitoring the system allow us to implement and evaluate several efficient techniques and different scheduling schemas related with SBST.

Beyond the invocation of test daemons, the Testing Manager process is responsible for the collection of test results in order to initiate the recovery mechanism in the case that a permanent fautl is detected. In particular, upon completion of a test session, the corresponding test daemon sends the test result back to the Testing Manager. We note here that in our work, the analysis of the test results (i.e., the comparison of the test results with the golden/expected results) is carried out by each test daemon individually, followed by a pass/fail signal from each test daemon to the Testing Manager. An alternative implementation could delegate the analysis of every test result to the Testing Manager.

For the scheduling approaches of this work, two different self-testing scheduling policies are considered, (a) the utilization-based approach where a feedback about the executed instructions determines the initiation of a testing session at the granularity of sub-core unit, and (b) the periodic testing of entire system where the testing procedure is applied at core level. More

details and the benefits of each approach are given in the Chapters 4, 5 and 6.

#### 3.1.3 Recovery Management and Support

Beyond the detection of faults, modern systems must be enhanced with mechanisms able to self-repair and recover the system to a fault-free state, in order to remain functional despite the presence of permanent faults. Once an error is detected by on-demand SBST, the system must be able to recover via rollback to a fault-free state. Hence, a recovery mechanism is introduced in DaemonGuard Framework, which is able to keep the system operational despite the occurrence of permanent faults. The main components of the proposed recovery mechanism are (a) the Checkpoint Manager, and (b) the Recovery Manager, which are responsible, respectively, for the creation of system checkpoints and determining a valid checkpoint (among the multiple stored ones) to roll back. Both mechanisms are resides in the O/S and are triggered by the Testing Manager process.

In the very simple form, the Checkpoint Manager is triggered upon the completion of each testing session (either for a sub-core functional unit or the entire core) and initiates the process for the creation of a checkpoint with the fault-free state of the system. As the main part of this work is based on on-demand testing (Selective SBST), an efficient Checkpoint Manager is proposed in order to reduce the number of checkpoints within the system. Details about the algorithm and its implementation are given in Chapter 7.

The second process related with the recovery mechanism is responsible to determine a valid checkpoint for rollback. Considering the utilization-based testing, the most recent checkpoint cannot ensure the fault-free state as the checkpoint is created upon the completion of a testing session targeting in many cases part of a core and not the entire system. As a result, an intelligent mechanism for to determine a valid checkpoint for recovery is introduced. Chapter 7 provides details about the Most Recent Valid Checkpoint algorithm.

#### 3.2 Hardware Level

The DaemonGuard Framework is mainly developed to support Software-Based Self-Testing orchestrated by the O/S. However, to support the on-line SBST, a minimum hardware enhancements are required. The cores of the system are enhanced with monitoring components per functional units (counting the executed instructions) in order to support the utilization-based Selective SBST (see Chapters 4 and 5) while some modifications on the Cache Address

Mapping component are required in order to support the clustering approach of test scheduling techniques in large systems (see Chapter 6).

#### 3.2.1 Hardware Support

The proposed selective testing methodology relies on the run-time gathering of information regarding the utilization of the various functional units within each core of the system. The term "utilization" refers to the number of instructions that have made use of the specific unit during normal operation. In order to collect this data, we assume the presence of a set of hardware instruction counters. There is one such counter for each functional unit within each core. instruction counters are developed to support the needs of this work and specifically the Selective SBST. Since, our scope is to develop the DaemonGuard as a generic Framework that can support different forms of SBST that may required feedback from the system, the instruction counters can be replaced by any other components or can be enhanced to include other type of information (i.e. historical data).

Furthermore, as one of the contributions of this work is to maintain the scalability of multicore systems in terms of the number of cores, low-cost enhancements of hierarchical memory

system are considered as well. In particular, in Chapter 6 we proposed the clustering approach