## COMPLEX FUNCTIONAL OXIDES FOR THERMAL MANAGEMENT AND RESISTIVE SWITCHING APPLICATIONS

DOCTOR OF PHILOSOPHY DISSERTATION

**CHARIS ORFANIDOU**

### COMPLEX FUNCTIONAL OXIDES FOR THERMAL MANAGEMENT AND RESISTIVE SWITCHING APPLICATIONS

### **CHARIS ORFANIDOU**

A Dissertation Submitted to the University of Cyprus in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

### Charis M. Orfanidou

# COMPLEX FUNCTIONAL OXIDES FOR THERMAL MANAGEMENT AND RESISTIVE SWITCHING APPLICATIONS

The present Doctoral Dissertation was submitted in partial fulfillment of the requirements for the Degree of Doctor of Philosophy at the **Department of Mechanical and Manufacturing Engineering** and was approved on the **December 12, 2018** by the members of the Examination Committee.

| Research Supervisor Ioannis Giapintzakis, Profes | SO1 |

|--------------------------------------------------|-----|

|                                                  |     |

|                                                  |     |

| Daniele Ielmini, Professor                       |     |

|                                                  |     |

| Julius Georgiou, Associate Professor             |     |

|                                                  |     |

|                                                  |     |

| Theodora Kyratsi, Associate Professor            |     |

|                                                  |     |

|                                                  |     |

### DECLARATION OF DOCTORAL CANDIDATE

The present doctoral dissertation was submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy of the University of Cyprus. It is a product of original work of my own, unless otherwise mentioned through references, notes, or any other statements.

Charis M. Orfanidou

#### **ABSTRACT**

Ever-increasing miniaturization and high-demanding computer memory and processor industry require fast, miniaturized, reproducible and "cool" electronic devices. Novel materials that are able to lower processor temperature, and new device structures for faster and miniaturized computer memories are currently investigated.

In this thesis technological application related features of  $La_5Ca_9Cu_{24}O_{41}$  and  $Li_xCoO_2$  materials have been studied. In particular, a feasibility simulation study using  $La_5Ca_9Cu_{24}O_{41}$  material for heat channeling in Extremely-Thin-Silicon-on-Insulator devices was accomplished, and an experimental study of Resistive Switching phenomena in  $Li_xCoO_2$ -based memory cells was carried out in order to identify the mechanism governing these phenomena.

La<sub>5</sub>Ca<sub>9</sub>Cu<sub>24</sub>O<sub>41</sub> was selected for this study, as a material with highly anisotropic thermal conductivity, while at the same time is an electrical insulator. For that reason the possible use of it in electronic devices can be of high research interest.

Li<sub>x</sub>CoO<sub>2</sub> is an extensively studied material and widely known for its use as a cathode material in Li-ion rechargeable batteries. Nevertheless, it has recently been shown to also exhibit resistive switching characteristics. The fundamental mechanism underlying the resistive switching behavior could be of high research and industrial interest.

#### ПЕРІЛНЧН

Η υψηλά απαιτητική βιομηχανία υπολογιστών για γρήγορη σμίκρυνση των επεξεργαστών και της μνήμης τους απαιτεί ηλεκτρονικές συσκευές γρήγορες, με το μικρότερο μέγεθος, με σταθερότητα και λειτουργία σε χαμηλές θερμοκρασίες. Νέα υλικά που επιτρέπουν την λειτουργία των επεξεργαστών σε χαμηλή θερμοκρασία, και νέες δομές για ταχύτερες και μικρότερες σε μέγεθος μνήμες ηλεκτρονικών υπολογιστών μελετώνται.

Για την διατριβή αυτή, έχουν μελετηθεί ιδιότητες των υλικών La<sub>5</sub>Ca<sub>9</sub>Cu<sub>24</sub>O<sub>41</sub> και Li<sub>x</sub>CoO<sub>2</sub>, σχετικές με τη χρήση τους σε τεχνολογικές εφαρμογές. Συγκεκριμένα, μελέτη προσομοίωσης πιθανής χρήσης του υλικού La<sub>5</sub>Ca<sub>9</sub>Cu<sub>24</sub>O<sub>41</sub> για διοχέτευση της υψηλής θερμικής ροής στο εξωτερικό μέρος μίας εξαιρετικά-λεπτής-συσκευής-πυριτίου-πάνω-σεμονωτή (ETSoI) έχει επιτευχθεί, και επίσης η μελέτη του φαινομένου της μεταγωγής αντίστασης του υλικού Li<sub>x</sub>CoO<sub>2</sub> με σκοπό να εντοπιστεί ο μηχανισμός που διέπει αυτό το φαινόμενο πραγματοποιήθηκε.

Το υλικό La<sub>5</sub>Ca<sub>9</sub>Cu<sub>24</sub>O<sub>41</sub> επελέγη για τη μελέτη αυτή ως υλικό με υψηλό βαθμό ανισοτροπίας στη θερμική αγωγιμότητα, ενώ την ίδια στιγμή είναι ένας ηλεκτρικός μονωτής. Για το λόγο αυτό η πιθανή χρήση του La<sub>5</sub>Ca<sub>9</sub>Cu<sub>24</sub>O<sub>41</sub> σε ηλεκτρονικές συσκευές μπορεί να είναι υψηλού ερευνητικού ενδιαφέροντος.

Το Li<sub>x</sub>CoO<sub>2</sub> είναι ένα υλικό ευρέως γνωστό για τη χρήση του ως υλικό καθόδου σε επαναφορτιζόμενες μπαταρίες Li-ion και εκτενώς μελετημένο. Παρόλα αυτά, έχει προσελκύσει την προσοχή μας από την πρώτη επίδειξη της μεταγωγής στην αντίστασή του το 2011 από τον A Moradpour *et al.* Η απλότητα του προτεινόμενου μηχανισμού θα μπορούσε να είναι ερευνητικά και από τη σκοπιά της βιομηχανίας πολύ ενδιαφέρουσα.

#### **ACKNOWLEDGEMENTS**

First of all, I would like to thank my research supervisor Professor Ioannis Giapintzakis for his guidance, support and clear communication throughout the years of my PhD study.

I would also like to express my gratitude to Professor Daniele Ielmini, Associate Professors Julius Georgiou, and Theodora Kyratsi and Assistant Professor Dimokratis Grigoriadis for serving on my dissertation committee.

A major part of my work could not come true without the helpful collaboration with Mr. Panagiotis Ioannou (PhD candidate), Mrs. Christiana Nicolaou (PhD candidate), and Dr. Cristian Nicolae Mihailescu who deposited by Pulsed Laser Depositon and characterized by X-Ray Diffraction all Li<sub>x</sub>CoO<sub>2</sub> samples I measured. I would like to thank them all and also Dr. Evripides Kyriakides for helpful discussions and the development of the I-V measurements setup, and Dr. Elli Symeou for the support, and the joyful communication during all these years in the laboratory. Additionally, I thank Associate Professor Mathew Zervos for many enlightening discussions and helpful suggestions in the laboratory related with semiconductor physics.

Above all I would like to thank my family and friends for their continuous support and unconditional love, Polina, Minas, Vaios, Konstantina, and Dimitris. Especially I thank my little and adorable niece Polina for her bright spirit and positive energy that always reminds me how nice and kind the world can be!

Charis M. Orfanidou

December 12, 2018

### **FUNDING**

Part of this work was funded by the European Commission, FP7 – PEOPLE, Marie – Curie Actions Initial Training Network (ITN), project title: "Low-dimensional quantum magnets for thermal management", LOTHERM contract number: PITN-GA-2009-238475, 2009 – 2013.

I would like to acknowledge financial support from the Graduate School at the University of Cyprus through the program of PhD student fellowships for the academic year 2017 - 2018.

### LIST OF PUBLICATIONS

- C. M. Orfanidou, P. S. Ioannou, E. Kyriakides, Ch. Nicolaou, C. N. Mihailescu, V. S. Nguyen, V. S. Mai, O. Schneegans, and J. Giapintzakis, "Stoichiometry and volume dependent transport in lithium ion memristive devices", AIP Adv., 8(11):115211 (2018).

- V. H. Mai, A. Moradpour, P. Auban-Senzier, C. Pasquier, K. Wang, M. J. Rozenberg, J. Giapintzakis, C. N. Mihailescu, *C. M. Orfanidou*, E. Svoukis, A. Breza, Ch. B. Lioutas, S. Franger, A. Revcolevschi, T. Maroutian, P. Lecoeur, P. Aubert, G. Agnus, R. Salot, P.-A. Albouy, R. Weil, D. Alamarguy, K. March, F. Jomard, P. Chrétien and O. Schneegans, "Memristive and neuromorphic behavior in a Li<sub>x</sub>CoO<sub>2</sub> nanobattery", *Sci. Rep.*, 5:7761 (2015).

- 3. *Charis M. Orfanidou* and John Giapintzakis, "Heat channeling in extremely thin Silicon-on-Insulator devices: a simulation study", *IEEE Trans. on Electron Devices*, 60(10):6588902, pp. 3330–3334 (2013).

#### LIST OF CONFERENCES

- 1. *C. M. Orfanidou*, C. N. Mihailescu, V. H. Mai, V. S. Nguyen, O. Schneegans, G. Stan and J. Giapintzakis, **oral** presentation: "Resistive switching behavior in Li<sub>x</sub>CoO<sub>2</sub>-based devices fabricated on Si", E-MRS Fall Meeting 2016, Warsaw, Poland.

- V. S. Nguyen, V. H. Mai, A. Moradpour, P. Auban-Senzier, C. Pasquier, K. Wang, P.-A. Albouy, R. Weil, M. J. Rozenberg, J. Giapintzakis, C. N. Mihailescu, *C. M. Orfanidou*, E. Svoukis, A. Breza, Ch. B. Lioutas, T. Maroutian, P. Lecoeur, P. Aubert, G. Agnus, S. Franger, A. Revcolevschi, R. Salot, D. Alamarguy, P. Chrétien, and O. Schneegans, *poster* presentation: "Lithium cobalt oxide thin films towards resistive memories", NANOTECH FRANCE 2015, Paris, France.

- 3. *C. M. Orfanidou*, C. N. Mihailescu, V. H. Mai, V. S. Nguyen, O. Schneegans, G. Stan and J. Giapintzakis, **oral** presentation: "Resistive switching in MIM devices based on Li<sub>x</sub>CoO<sub>2</sub>", E-MRS Spring Meeting 2015, Lille, France.

- 4. *C. M. Orfanidou*, C. N. Mihailescu and J. Giapintzakis, **oral** presentation: "Thin films of low-dimensional quantum magnets & Simulation of heat channelling effect", Advances in Quantum Magnets Dynamics, 2013, Kolymbari, Crete, Greece.

- 5. *C. M. Orfanidou* and J. Giapintzakis, **oral** presentation: "Thermal Management at High Transistor Density Semiconductor Devices", 9<sup>th</sup> International Conference on Nanosciences & Nanotechnologies, NN12, 2012, Thessaloniki, Greece.

- 6. *C. M. Orfanidou* and J. Giapintzakis, **oral** presentation: "La<sub>5</sub>Ca<sub>9</sub>Cu<sub>24</sub>O<sub>41</sub> Layers as 1D Heat Spreaders for Thermal Management Solutions", COMSOL Conference 2011, Stuttgart, Germany.

- 7. *C. M. Orfanidou* and J. Giapintzakis, **oral** presentation: "La<sub>5</sub>Ca<sub>9</sub>Cu<sub>24</sub>O<sub>41</sub> Layers as 1D Heat Spreaders for the Design of Thermal Management Solutions", XXVII Pan-Hellenic Conference on Solid State Physics and Materials Science, 2011, Limassol, Cyprus.

## TABLE OF CONTENTS

| ABS | SIKA | .C1lll                                                                            |

|-----|------|-----------------------------------------------------------------------------------|

| ПЕ  | РІΛН | ΨHiv                                                                              |

| ACI | KNO  | WLEDGEMENTSv                                                                      |

| FUN | NDIN | Gvi                                                                               |

| LIS | T OF | PUBLICATIONSvii                                                                   |

| LIS | T OF | CONFERENCESviii                                                                   |

| LIS | T OF | FIGURESxiii                                                                       |

| LIS | T OF | TABLESxix                                                                         |

| ABI | BREV | VIATIONSxx                                                                        |

| 1   | Int  | roduction1                                                                        |

|     | 1.1  | Motivation on Thermal Management topic1                                           |

|     | 1.2  | Motivation on Resistive Switching topic2                                          |

|     | 1.3  | Thesis Structure                                                                  |

|     |      |                                                                                   |

| 2   |      | Ca <sub>9</sub> Cu <sub>24</sub> O <sub>41</sub> for Thermal Management lications |

|     | 2.1  | Introduction5                                                                     |

|     | 2.2  | Thermal Management Solutions for Electronic devices6                              |

|     | 2    | .2.1 Passive and Active Thermal Management                                        |

|   |     | 2.2.2  | Novel Thermal Management Solutions                                | 9  |

|---|-----|--------|-------------------------------------------------------------------|----|

|   | 2.3 | Las    | 5Ca <sub>9</sub> Cu <sub>24</sub> O <sub>41</sub> (LCCO) compound | 9  |

|   |     | 2.3.1  | LCCO crystal structure                                            | 9  |

|   |     | 2.3.2  | Thermal conductivity of LCCO                                      | 11 |

|   | 2.4 | Mo     | odel of Simulation Studies                                        | 12 |

|   |     | 2.4.1  | Software used in Simulations                                      | 12 |

|   |     |        | Finite Elements Analysis (FEA)                                    |    |

|   |     | 2.     | .4.2.1 Domain discretization                                      | 14 |

|   |     | 2.     | .4.2.2 Selection of interpolation functions                       | 15 |

|   |     | 2.     | .4.2.3 Formulation of the System of Equations                     | 15 |

|   |     | 2.     | .4.2.4 Simulation of the System of Equations                      | 16 |

|   |     | 2.4.3  | Model of Heat Conduction                                          | 16 |

|   |     | 2.     | .4.3.1 Geometry                                                   | 16 |

|   |     | 2.     | .4.3.2 Heat transfer in Solids                                    | 17 |

|   |     | 2.     | .4.3.3 Boundary conditions                                        | 19 |

|   | 2.5 | Sin    | nulation Studies                                                  | 20 |

|   |     | 2.5.1  | Heat Channeling in ETSoI devices.                                 | 20 |

|   |     | 2.5.2  | Further Analysis                                                  | 26 |

|   |     | 2.     | .5.2.1 Time dependent thermal analysis                            | 26 |

|   |     | 2.     | .5.2.2 Grid sensitivity analysis                                  | 28 |

|   |     | 2.     | .5.2.3 Effect of domain size                                      | 29 |

|   |     | 2.     | .5.2.4 Effect of boundary conditions and heat sink temperature    | 31 |

|   | 2.6 | Co     | nclusion                                                          | 33 |

|   |     |        |                                                                   |    |

| 3 | R   | esisti | ve Switching Applications & State of the Art 3                    | 35 |

|   | 3.1 | Int    | roduction                                                         | 35 |

|   | 3.2 | No     | n-volatile memories                                               | 36 |

|   |     | 3.2.1  | Flash memory                                                      | 37 |

|   | 3.2.2               | re-KAM memory                                                                                         | 38   |

|---|---------------------|-------------------------------------------------------------------------------------------------------|------|

|   | 3.2.3               | M-RAM memory                                                                                          | 39   |

|   | 3.2.4               | PC-RAM memory                                                                                         | 40   |

|   | 3.3 Re              | sistive Switching Phenomena                                                                           | 41   |

|   | 3.3.1               | Resistive-RAM memory (RRAM)                                                                           | 41   |

|   | 3.3.2               | Electrical polarization schemes for RS memory cells                                                   | 42   |

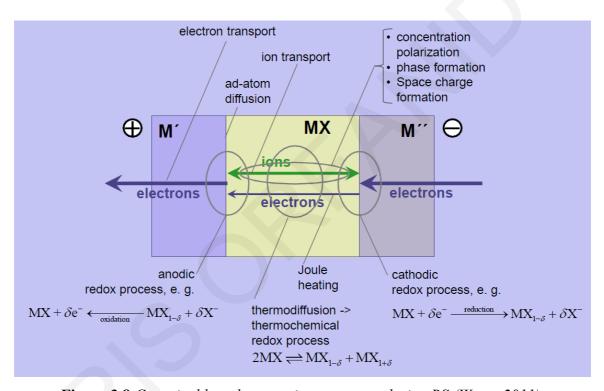

|   | 3.3.3               | Electrochemical processes                                                                             | 42   |

|   |                     | Classification of the electrochemical mechanisms involved in RS mena                                  | 44   |

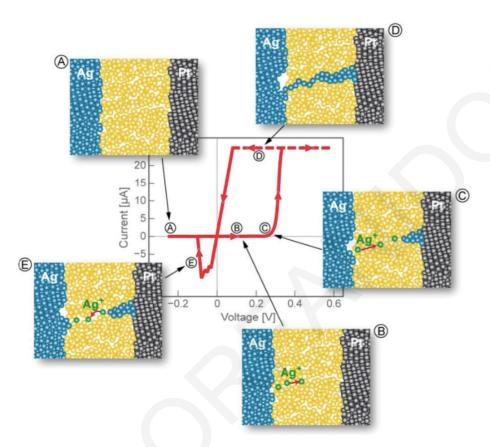

|   | 3                   | .3.4.1 Electrochemical Metallization Memory (ECM)                                                     | 44   |

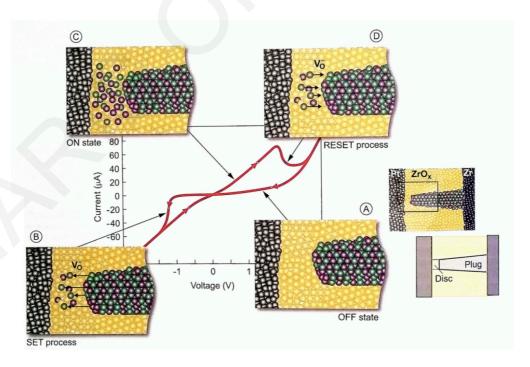

|   | 3                   | .3.4.2 Valence Change Memory (VCM)                                                                    | 46   |

|   | 3                   | .3.4.3 Thermochemical memory (TCM)                                                                    | 47   |

|   | 3.4 Li <sub>x</sub> | CoO <sub>2</sub> material                                                                             | 48   |

|   | 3.4.1               | Li <sub>x</sub> CoO <sub>2</sub> crystal structure                                                    | 48   |

|   | 3.4.2               | Electrical properties of Li <sub>x</sub> CoO <sub>2</sub>                                             | 50   |

|   | 3.5 Re              | sistive Switching in Li <sub>x</sub> CoO <sub>2</sub> -based memory cells                             | 51   |

|   | 3.6 Co              | nclusion                                                                                              | 53   |

|   |                     |                                                                                                       |      |

| 4 | Li <sub>x</sub> Co( | O <sub>2</sub> for Resistive Switching Applications                                                   | 54   |

|   | 4.1 Int             | roduction                                                                                             | 54   |

|   | 4.2 Ex              | perimental techniques                                                                                 | 55   |

|   | 4.2.1               | Pulsed Laser Deposition (PLD)                                                                         | 55   |

|   | 4.2.2               | Radio Frequency (RF) and Direct Current (DC) Sputtering technique                                     | es56 |

|   | 4.2.3               | X-ray diffraction (XRD)                                                                               | 58   |

|   | 4.2.4               | I-V measurements setup                                                                                | 60   |

|   | 4.3 Re              | sistive Switching phenomena in Au/Li <sub>x</sub> CoO <sub>2</sub> /SiO <sub>2</sub> /Si memory cells | 62   |

|   | 4.3.1               | Resistive switching behavior                                                                          | 62   |

|   | 4                   | .3.1.1 PLD-grown Li <sub>x</sub> CoO <sub>2</sub> thin films                                          | 62   |

|     |        | 4.    | .3.1.2 RF magnetron sputtering grown $Li_xCoO_2$ thin films                                           | 63 |

|-----|--------|-------|-------------------------------------------------------------------------------------------------------|----|

|     | ۷      | 4.3.2 | Effect of Li <sub>x</sub> CoO <sub>2</sub> layer thickness                                            | 66 |

|     | ۷      | 4.3.3 | Effect of SiO <sub>2</sub> layer thickness                                                            | 67 |

|     | ۷      | 4.3.4 | Effect of type and orientation of Si substrates                                                       | 68 |

|     | ۷      | 4.3.5 | Effect of Au top electrode size.                                                                      | 69 |

|     | ۷      | 4.3.6 | Effect of top electrode material                                                                      | 70 |

|     | 2      | 4.3.7 | Effect of Li content in Li <sub>x</sub> CoO <sub>2</sub> thin films.                                  | 72 |

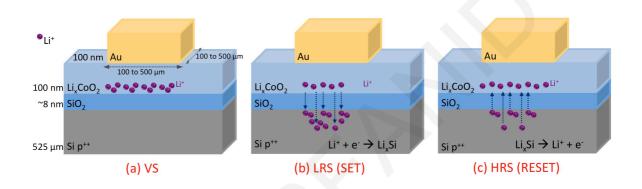

|     | 4.4    | Res   | sistive switching mechanism in Au/Li <sub>x</sub> CoO <sub>2</sub> /SiO <sub>2</sub> /Si memory cells | 75 |

|     | 4.5    | Co    | nclusion                                                                                              | 77 |

|     |        |       |                                                                                                       |    |

| 5   | Co     | onclu | ısion                                                                                                 | 78 |

|     | 5.1    | Las   | 5Ca <sub>9</sub> Cu <sub>24</sub> O <sub>41</sub> for Thermal Management Applications                 | 78 |

|     | 5.2    | Lix   | CoO <sub>2</sub> for Resistive Switching Applications                                                 | 79 |

|     |        |       |                                                                                                       |    |

| Rei | ferenc | es    |                                                                                                       | 80 |

## LIST OF FIGURES

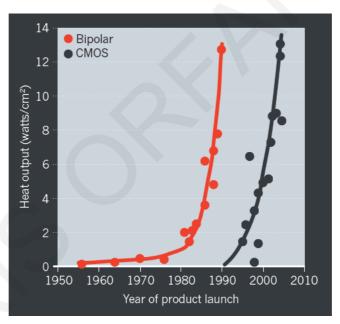

| Figure 2.1 As transistors technology is switching from bipolar to CMOS, microchips' hea                           |

|-------------------------------------------------------------------------------------------------------------------|

| output was lowered, but with the increase of device densities have quickly driven up again                        |

| (Ball 2012)                                                                                                       |

|                                                                                                                   |

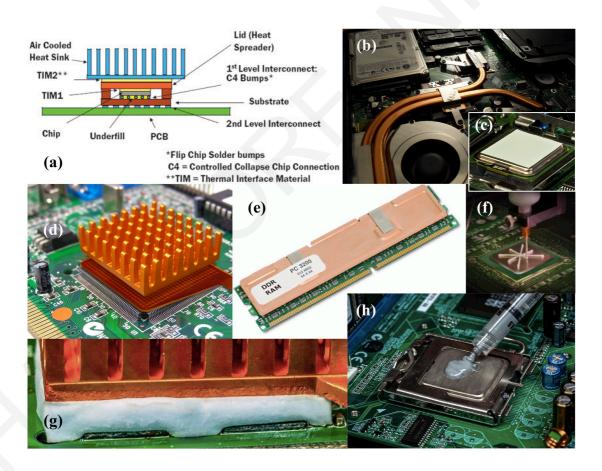

| Figure 2.2 Passive thermal management components. (a) Diagram of a flip-chip IC in a                              |

| high-performance package with attached heat sink, (b) laptop heat pipe, (c) phase change                          |

| interface material, (d) heat sink, (e) heat spreader on RAM, (f) thermally conductive                             |

| grease, (g) heat sink on gap filler thermal pad, (h) thermal conductive paste                                     |

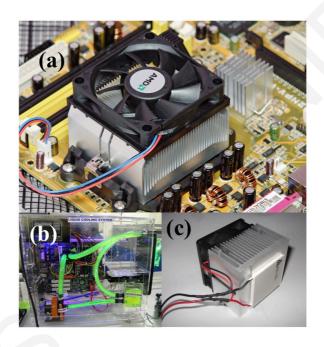

| Figure 2.3 Active thermal management components. (a) Heat sink with fan from AML                                  |

| Semiconductor Company, (b) liquid cooling system, (c) Peltier cooling plate                                       |

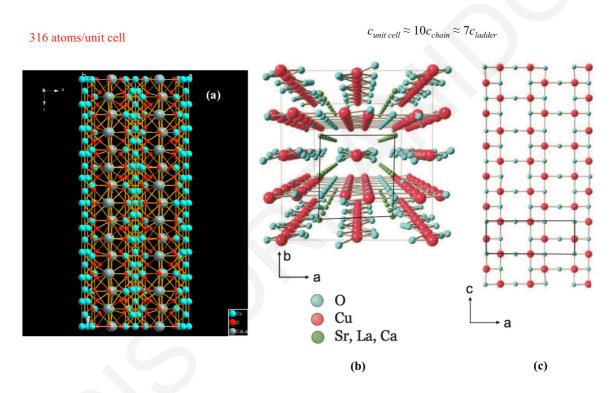

| Figure 2.4 Crystal structure of LCCO. (a) LCCO has a unit cell of high complexity with a                          |

| huge volume and 316 atoms/unit cell as well as incommensurability along the c-axis. (b,                           |

| Top view of the a-b plane, where the black square indicates the dimensions of the unit cell                       |

| (c) Top view of the a-c plane where the black square indicates the dimensions of the ladder                       |

| unit cell. Figures (b) and (c) taken from (Otter 2012a)                                                           |

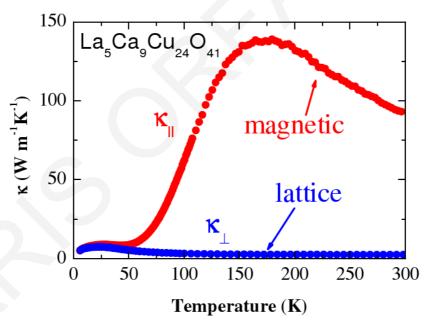

| <b>Figure 2.5</b> Thermal conductivity of the spin ladder material LCCO, measured parallel ( $\kappa_{\parallel}$ |

| and perpendicular (κ±) to the ladders. Data from (Hess 2001)                                                      |

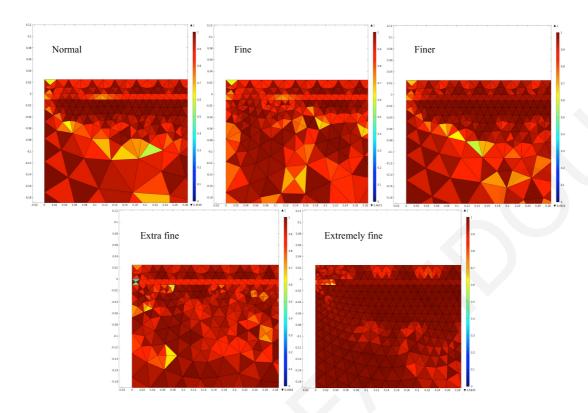

| Figure 2.6 Example of the physics-controlled mesh quality from a normal to an extremely                           |

| fine element size of a 2-D structure                                                                              |

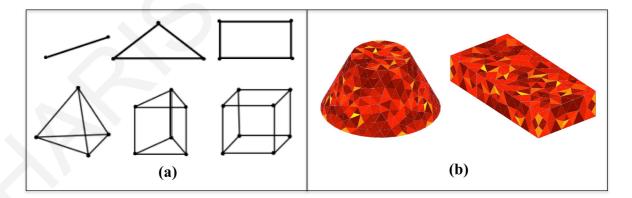

| Figure 2.7 (a) Basic finite elements: 1-D, 2-D, and 3-D. (b) Examples of 3-D finite elements                      |

| discretization                                                                                                    |

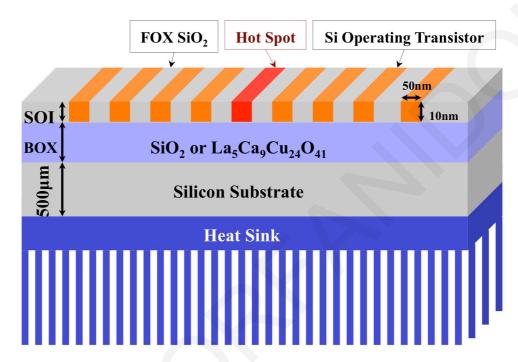

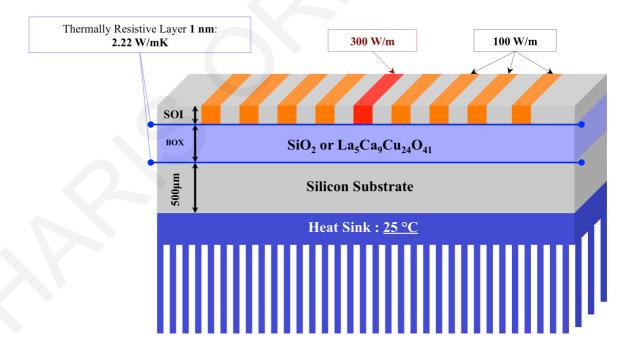

| Figure 2.8 Schematic showing the geometry of the devices we have simulated. The                                   |

| operating transistors are shown in orange, the hot-spot in red and the BOX layer (LCCC                            |

| or $SiO_2$ ) in lilac. The thicknesses are not to scale                                                           |

| Figure 2.0 Schematic showing the houndary conditions of the devices under study                                   |

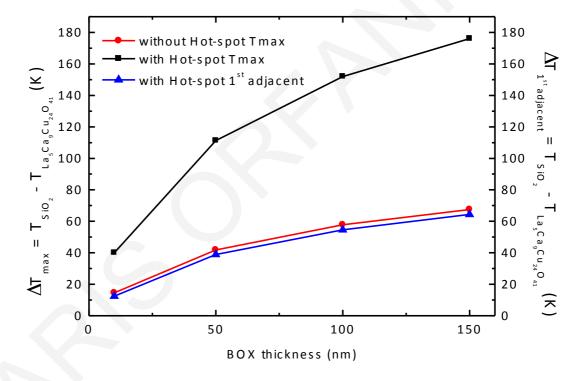

| <b>rigure 2.10</b> Temperature differences for 1-μm spacing between transistors, obtained of      |

|---------------------------------------------------------------------------------------------------|

| subtracting from the temperature of the SoI device with a $SiO_2$ BOX layer, the temperature      |

| of the SoI device with an LCCO BOX layer. Left ordinate: circular dots (red line) are the         |

| temperature differences of the devices without the hot-spot, and square dots (black line          |

| are the temperature differences of the devices with the hot-spot. Right ordinate: triangula       |

| dots (blue line) are the temperature differences locally at the first adjacent to the hot-spo     |

| operating transistor                                                                              |

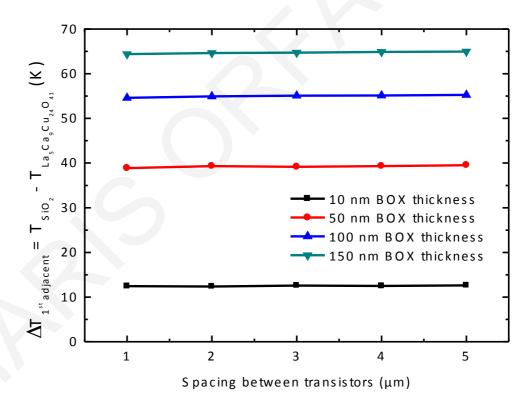

| Figure 2.11 Temperature differences obtained by subtracting from the local temperature            |

| at the first adjacent to the hot-spot operating transistor of the ETSoI device with a SiO         |

| BOX layer, the local temperature of the ETSoI device with an LCCO BOX layer, for                  |

| different spacing between the transistors of the device                                           |

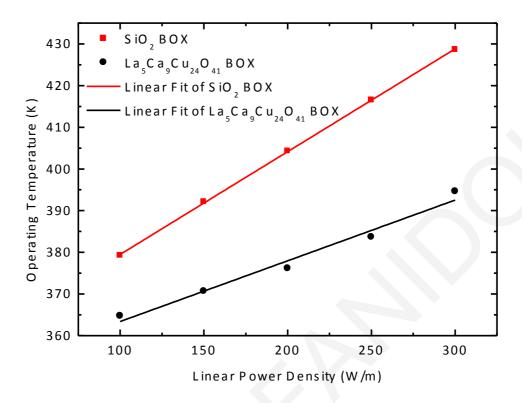

| Figure 2.12 Maximum operating temperatures obtained from an ETSOI device with a SiO               |

| BOX layer (red square dots) and an ETSOI device with an LCCO BOX layer (black                     |

| circular dots) while the linear power density of the hot-spot is increasing gradually from        |

| 100 W/m to 300 W/m. The lines are linear fittings23                                               |

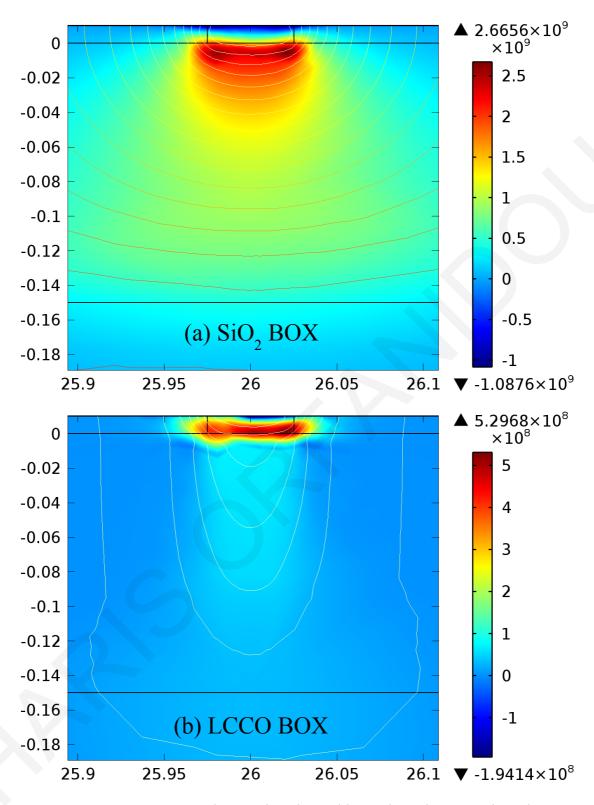

| Figure 2.13 Temperature gradient and isothermal lines along the cross-plane direction             |

| plotted for the ETSoI device with a 150-nm BOX layer of (a) SiO <sub>2</sub> and (b) LCCO. Plot   |

| show only the hot-spot (fifth operating transistor). Temperature gradient is given in             |

| kelvin/meter and dimensions in micrometers24                                                      |

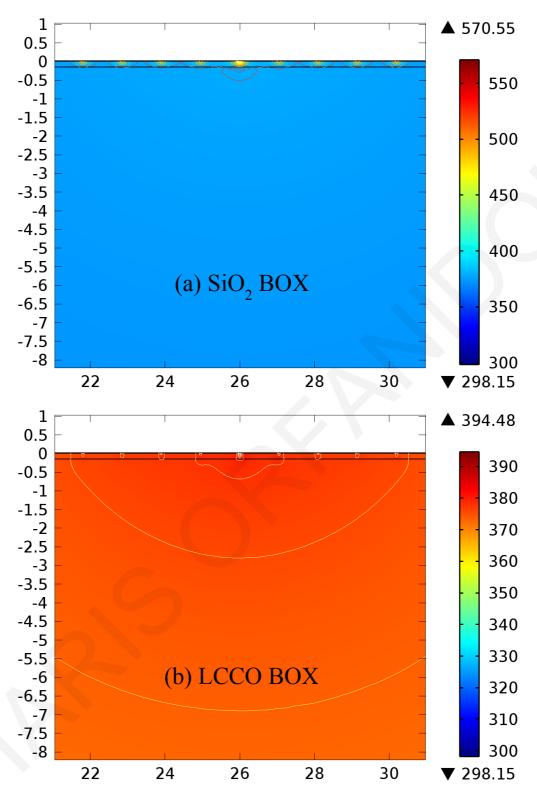

| Figure 2.14 Surface temperature and the isothermal lines plotted for the ETSoI device             |

| with a BOX layer of (a) SiO2 and (b) LCCO. Plots show all the nine transistors in device.         |

| with hot-spot. For visualization reasons, we present data only for devices with 1-µn              |

| spacing between transistors and a BOX layer of 150 nm. Temperature is given in kelvin             |

| and dimensions in micrometers25                                                                   |

|                                                                                                   |

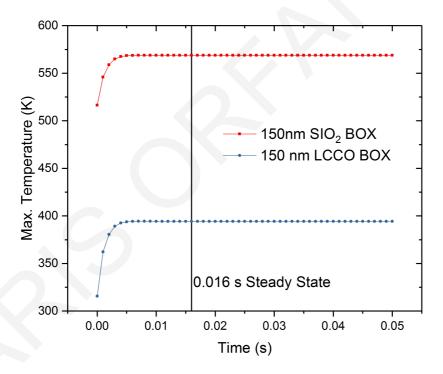

| Figure 2.15 Time dependence of the maximum temperature of the ETSoI device with a                 |

| SiO <sub>2</sub> BOX layer (red) and with an LCCO BOX layer (blue). After a sharp increase of the |

| temperature at the first 5 ms the steady state condition is finally obtained at 16 ms20           |

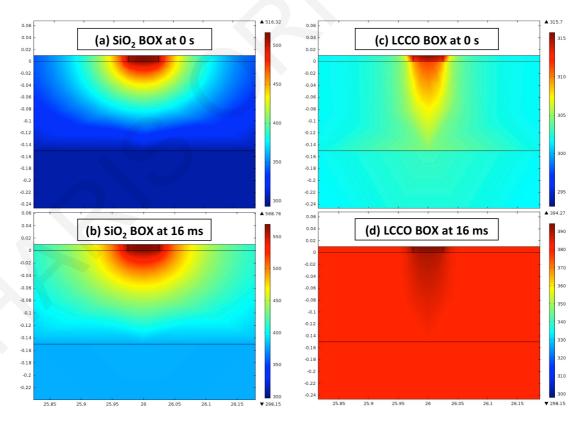

| Figure 2.16 Surface temperature plotted for the ETSoI device with a 150-nm BOX layer of           |

| (a), (b) SiO <sub>2</sub> and (c), (d) LCCO. Plots show only the temperature distribution at ano  |

| around the hot-spot for time steps at 0 s ((a) and (c)), and 16 ms ((b) and (d)) $\frac{1}{2}$    |

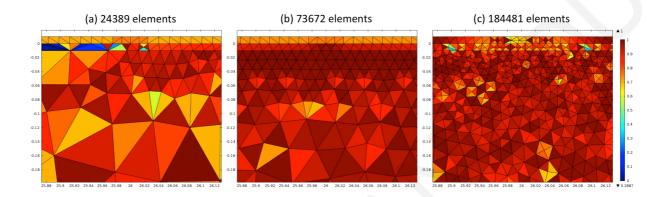

| Figure 2.17 Mesh quality plots for three different grid sizes: (a) extremely coarse, (b) fine and (c) extremely fine meshes. A triangular element of high quality (equilateral) |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                 |

| corresponds to value 1 (dark red color) and an element of very low quality - that deviate.                                                                                      |

| a lot from the triangle – corresponds to 0 (dark blue color)29                                                                                                                  |

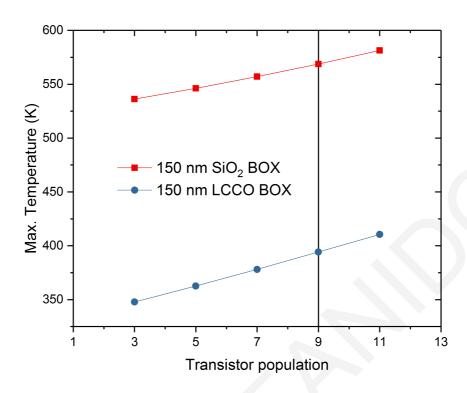

| Figure 2.18 Maximum temperature of the ETSoI device with a SiO <sub>2</sub> BOX layer (red) and                                                                                 |

| with an LCCO BOX layer (blue) depending on the number of operating transistors30                                                                                                |

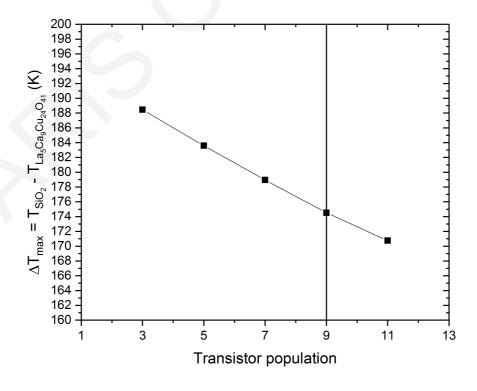

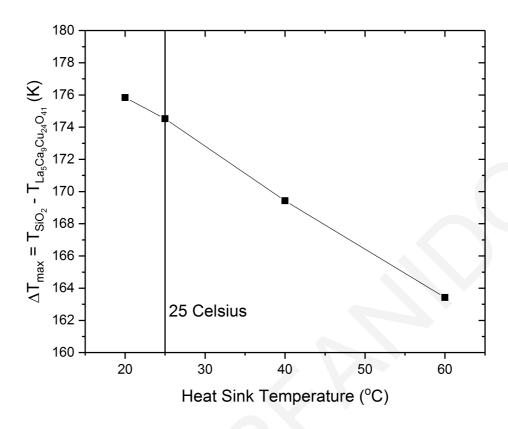

| Figure 2.19 Maximum temperature differences of the ETSoI device depending on the                                                                                                |

| number of operating transistors30                                                                                                                                               |

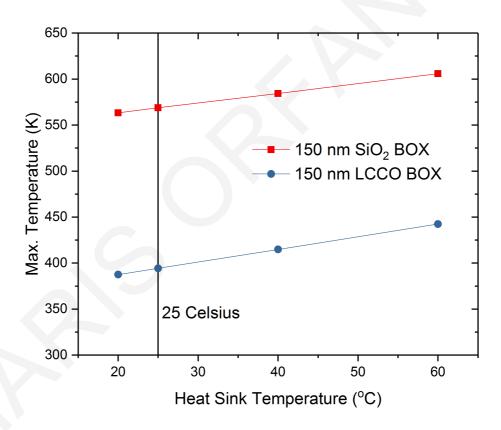

| <b>Figure 2.20</b> <i>Maximum temperature of the ETSoI device with a SiO<sub>2</sub> BOX layer (red) and</i>                                                                    |

| with an LCCO BOX layer (blue) depending on the heat sink temperature                                                                                                            |

| Figure 2.21 Maximum temperature differences of the ETSoI devices depending on the hea                                                                                           |

| sink temperature                                                                                                                                                                |

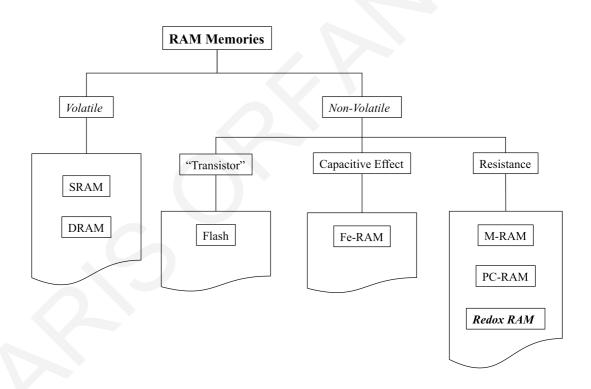

| Figure 3.1 Simplified diagram of RAM memories (Nanoelectronics 2012)                                                                                                            |

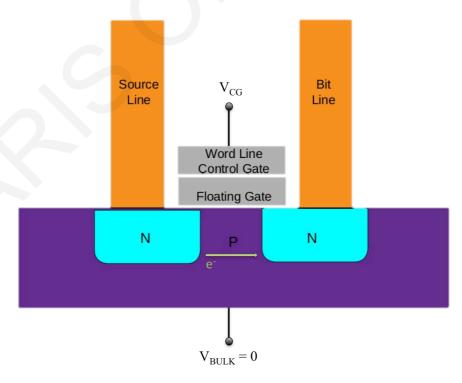

| Figure 3.2 Simplified diagram showing the operation of Flash memory (Cyferz Oct                                                                                                 |

| 2016)                                                                                                                                                                           |

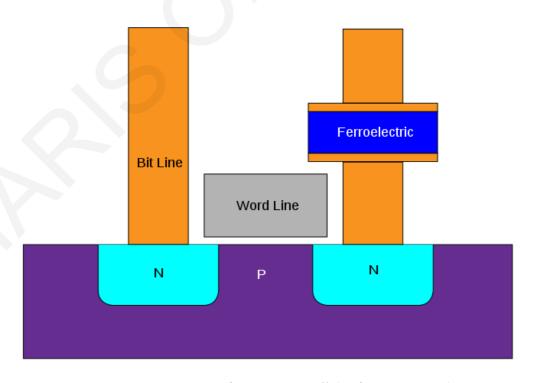

| Figure 3.3 Structure of a Fe-RAM cell (Cyferz Aug-2016)                                                                                                                         |

|                                                                                                                                                                                 |

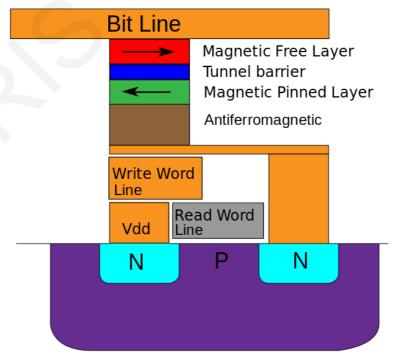

| Figure 3.4 Simplified diagram showing the structure of a MRAM memory (Cyferz Sep                                                                                                |

| 2016a)39                                                                                                                                                                        |

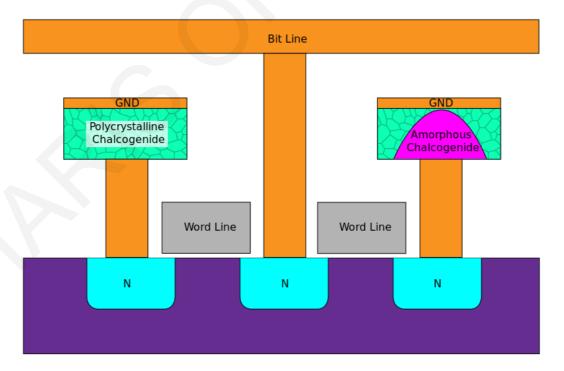

| Figure 3.5 A cross-section of two PC-RAM memory cells. One cell is in low resistance                                                                                            |

| crystalline state, the other in high resistance amorphous state (Cyferz Sep-2016b)40                                                                                            |

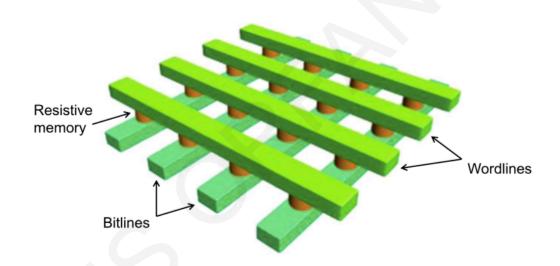

| Figure 3.6 Schematic showing crossbar array architecture where wordlines (rows) and                                                                                             |

| bitlines (columns) stand for M, and resistive memory stands for I of an MIM memory cel                                                                                          |

| (Ielmini 2016, Jo 2009)                                                                                                                                                         |

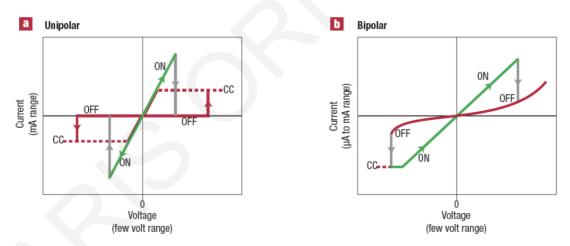

| Figure 3.7 Diagrams showing (a) Unipolar RS, and (b) Bipolar RS, according to (Wase                                                                                             |

| 2007)                                                                                                                                                                           |

| Figure 3.8 Conceivable redox-reaction processes during RS (Waser 2011)  45                                                                                                      |

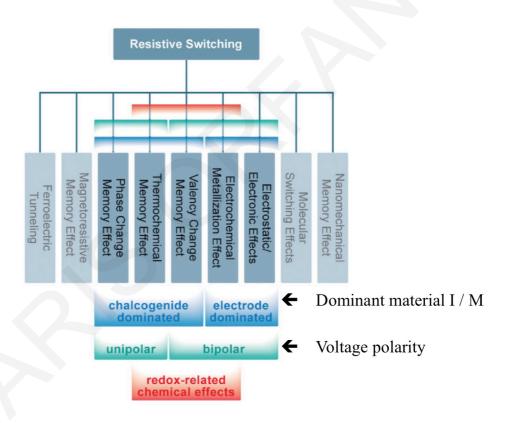

| <b>Figure 3.9</b> Classification of the resistive switching effects that are considered for non                                   |

|-----------------------------------------------------------------------------------------------------------------------------------|

| volatile memory applications. Switching mechanisms based on thermal, chemical, and                                                |

| electronic/electrostatic effects (Waser 2009)44                                                                                   |

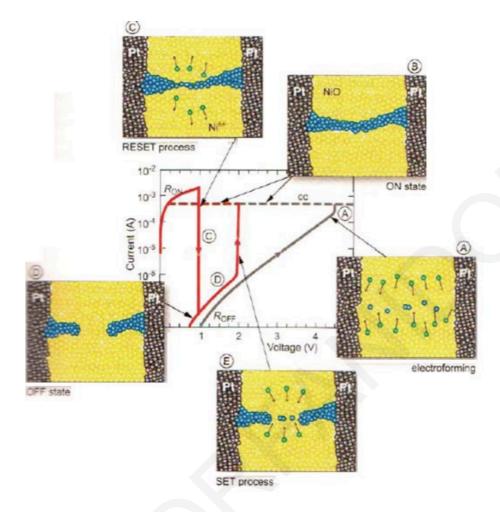

| Figure 3.10 Schematic showing an-inside of the electrochemical reactions that take place                                          |

| in an ECM during a complete cycle. (A) to (D) show the SET process $(Ag \rightarrow Ag^+ + e^-)$ and                              |

| (E) the RESET process (Valov 2011)                                                                                                |

| Figure 3.11 Current-voltage (I-V) plot of a Pt/ZrO <sub>x</sub> /Zr VCM cell. Pt acts as the active                               |

| electrode, while Zr is the ohmic electrode. The insets show the different stages of the RS                                        |

| process. (A) OFF (HRS) state; (B) SET process; (C) ON (LRS) state; (D) RESET process                                              |

| (Nanoelectronics 2012)                                                                                                            |

|                                                                                                                                   |

| Figure 3.12 Schematic showing an-inside of the electrochemical reactions that take place                                          |

| in a Pt/NiO/Pt TCM memory. The process is of a unipolar type and it is shown in inset.                                            |

| from (A) to (E) (Nanoelectronics 2012)48                                                                                          |

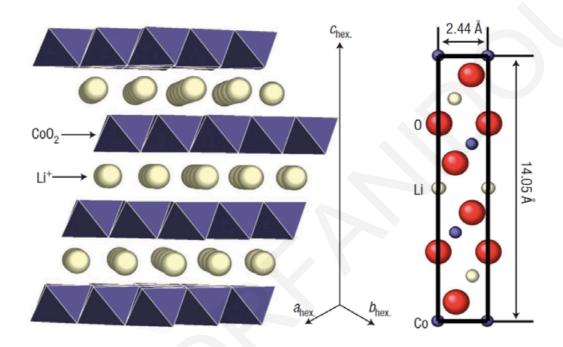

| <b>Figure 3.13</b> HT- Li <sub>x</sub> CoO <sub>2</sub> crystal structure (Shao-Horn 2003)                                        |

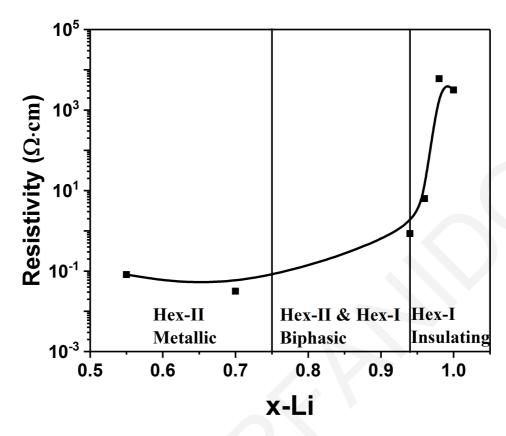

| Figure 3.14 Resistivity, $\rho$ , as a function of Li stoichiometry at room temperature                                           |

| (Ménétrier 1999)51                                                                                                                |

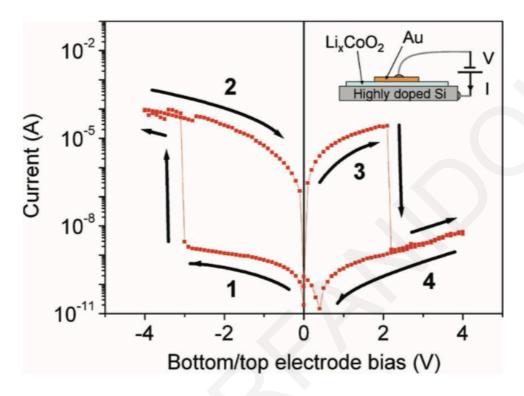

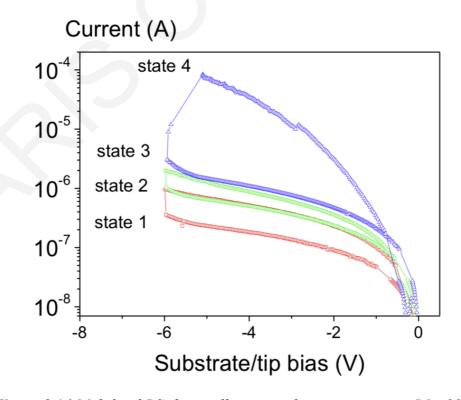

| <b>Figure 3.15</b> <i>I-V</i> characteristics of a $Li_xCoO_2$ MIM cell (Moradpour 2011)                                          |

| <b>Figure 3.16</b> Multilevel RS, four well-separated resistance states (Mai 2015)                                                |

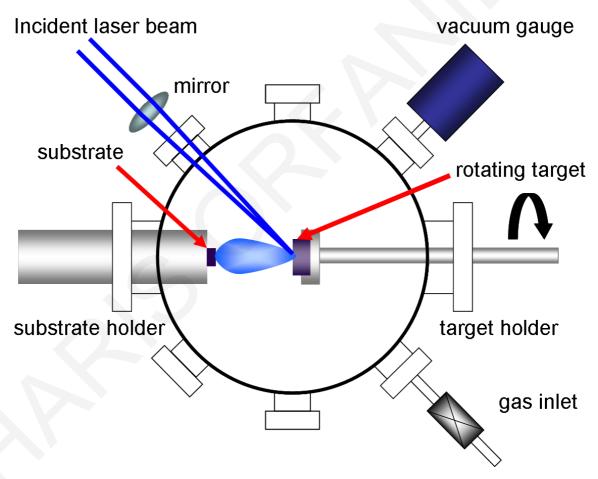

| Figure 4.1 Schematic of the PLD chamber configuration (Wang 2013)55                                                               |

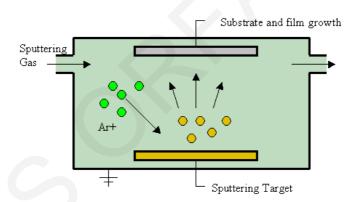

| Figure 4.2 Simplified schematic of sputtering deposition technique (Pub.Dom. 2016)57                                              |

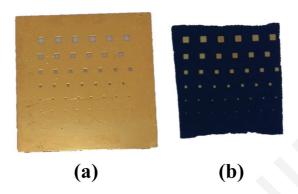

| Figure 4.3 (a) Veco B.V. high electroformed Ni shadow mask with aperture sizes of                                                 |

| $0.5 \times 0.5, 0.4 \times 0.4, 0.3 \times 0.3, 0.2 \times 0.2, 0.1 \times 0.1, 0.06 \times 0.06, 0.03 \times 0.03 \ mm^2$ , (b) |

| Au/Li <sub>x</sub> CoO <sub>2</sub> /SiO <sub>2</sub> /Si memory cells after top electrode deposition using the Ni shadov         |

| mask                                                                                                                              |

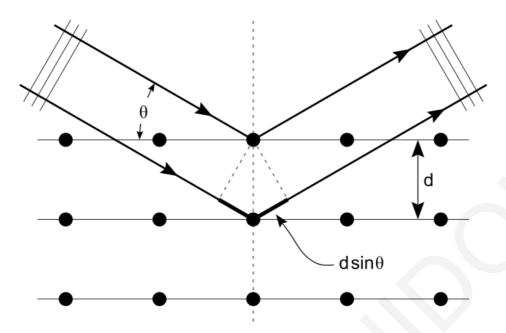

| Figure 4.4 Bragg's law schematic (Hydrargyrum 2016)                                                                               |

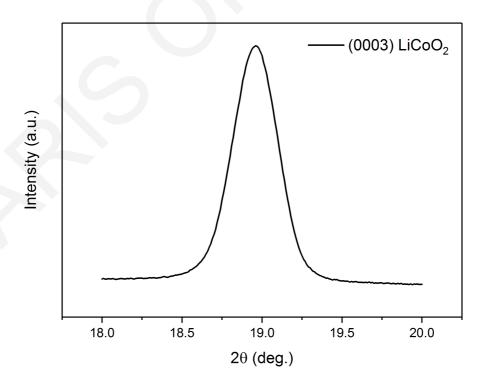

| Figure 4.5 Typical GIXRD nattern of a Li CoO2 thin film                                                                           |

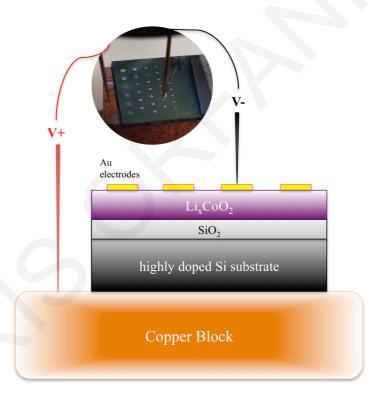

| <b>Figure 4.6</b> Cross-section at agram of an $Au/Li_xCoO_2/SiO_2/Si$ sample give a with $Ag$ -paste                       |

|-----------------------------------------------------------------------------------------------------------------------------|

| on top of a copper block. Inset shows a photograph of the sample with the probe tips                                        |

| mechanically attached on the top and bottom electrodes of a memory cell                                                     |

|                                                                                                                             |

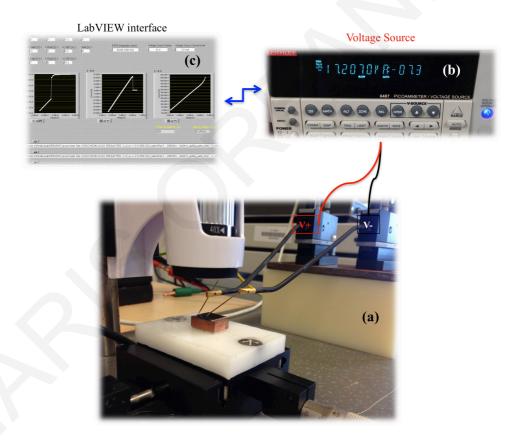

| Figure 4.7 Schematic of the I-V setup. (a) An $Au/Li_xCoO_2/SiO_2/Si$ sample is mounted on                                  |

| the sample holder and probe tips are mechanically attached on the top and bottom                                            |

| electrodes of a memory cell. (b) A Keithley 6487 instrument sourcing voltage and                                            |

| measuring current is connected with the micro-manipulators. (c) The LabVIEW .vi                                             |

| program is controlling the voltage source and recording current measurements data61                                         |

| Figure 4.8 (a) Homemade LabVIEW interface, and (b) block diagram62                                                          |

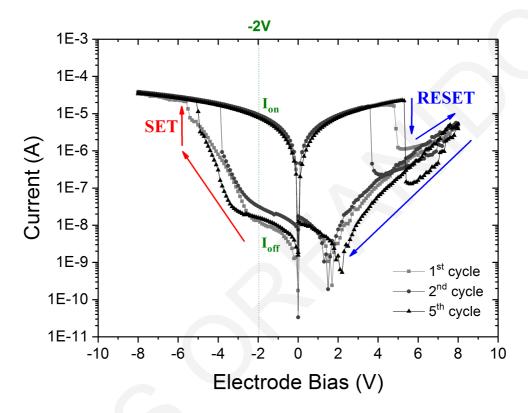

| Figure 4.9 Typical I-V characteristics of Au/Li <sub>x</sub> CoO <sub>2</sub> /SiO <sub>2</sub> /Si PLD grown memory cells. |

| Shown here are different cycles for a cell composed of a 50 nm-thick Li <sub>x</sub> CoO <sub>2</sub> film                  |

| deposited on a $p++$ type Si (111) substrate with a 3 nm SiO <sub>2</sub> layer as deposited by RF-                         |

| sputtering, (I-V sweeps were performed on $500x500 \mu m^2$ Au electrodes and $200 k\Omega$                                 |

| external resistor). The vertical dashed line at -2 V indicates the voltage bias at which $I_{on}$                           |

| (LRS) and $I_{off}$ (HRS) values were extracted in order to plot Figures 4.13, 4.14, and                                    |

| 4.15                                                                                                                        |

|                                                                                                                             |

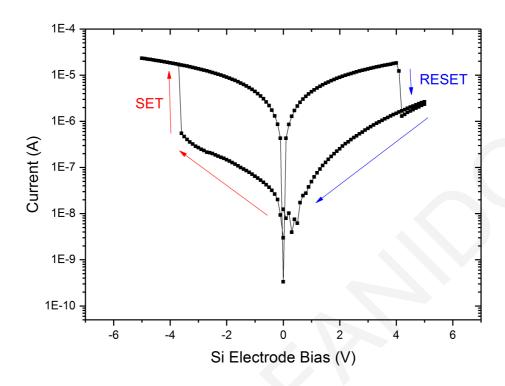

| Figure 4.10 Voltage sweep of a Au/Li <sub>x</sub> CoO <sub>2</sub> /SiO <sub>2</sub> /Si RF magnetron sputtering grown      |

| memory cell (I-V sweeps were performed on 500x500 μm² Au electrodes)64                                                      |

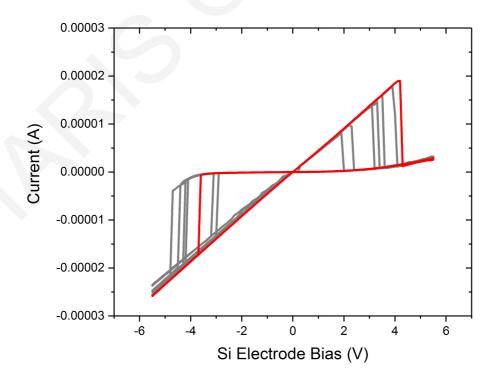

| Figure 4.11 I-V measurement of 10 consecutive (occasionally overlapping) RS cycles64                                        |

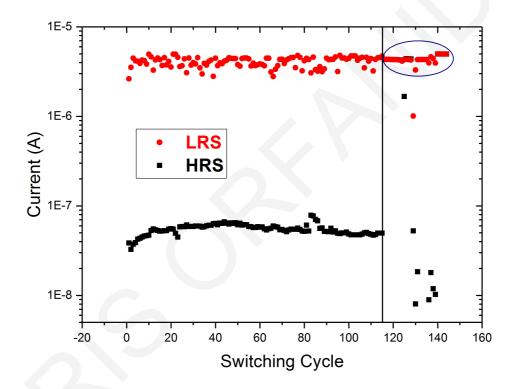

| Figure 4.12 LRS and HRS distribution over 144 RS cycles. Degradation of the RS                                              |

| performance is beginning to occur on the 116 <sup>th</sup> switching cycle. The areas of overlapping                        |

| HRS and LRS are indicated65                                                                                                 |

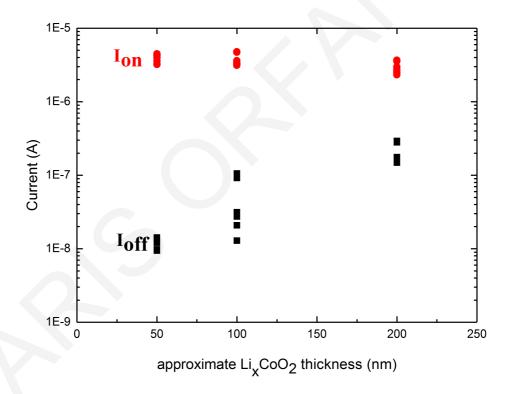

| Figure 4.13 Dependence of $I_{on}$ and $I_{off}$ on $Li_xCoO_2$ thickness. $SiO_2$ thickness is 3 nm (RF-                   |

| sputtered) for all cells shown in the graph (I-V measurements with a 200 k $\Omega$ external                                |

| resistor). Different data points for the same $Li_xCoO_2$ thickness correspond to different                                 |

| cells, and also to different cycles for the same cell. The cells have been fabricated on $p++$                              |

| type Si (111) substrates                                                                                                    |

|                                                                                                                             |

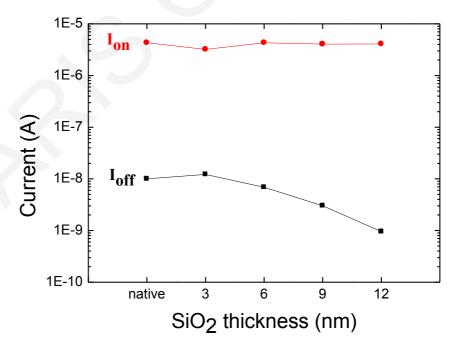

| <b>Figure 4.14</b> Dependence of $I_{on}$ and $I_{off}$ on the deposited $SiO_2$ thickness (I-V measurements                |

with a 200  $k\Omega$  external resistor). The thickness values correspond to the ones of the as-

| grown $SIO_2$ films prior to post-aeposition annealing. $Li_xCoO_2$ films have an a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | рргохітаге   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| thickness of 50 nm and the substrates are $p^{++}$ type Si (111)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67           |

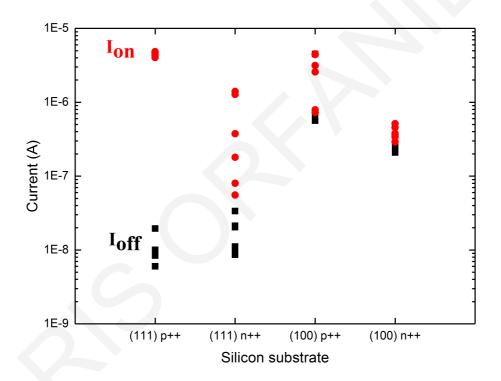

| Figure 4.15 Dependence of $I_{on}$ and $I_{off}$ on the type and orientation of $Si$ substitutes $Si$ subst | strates (I-V |

| measurements with a 200 $k\Omega$ external resistor). Different data points for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | he same Si   |

| substrate correspond to different cells, and also to different cycles for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | same cell.   |

| $Li_xCoO_2$ films have an approximate thickness of 50 nm and the $SiO_2$ is native                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 68           |

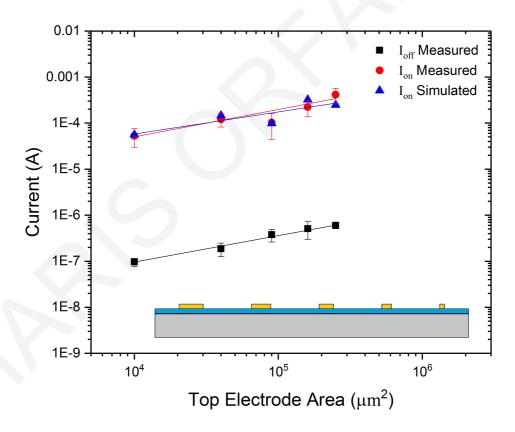

| Figure 4.16 Dependence of current on top electrode area of Au/Li <sub>x</sub> CoO <sub>2</sub> /SiO <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | /Si memory   |

| cells: experimental $I_{off}$ (at -2 V; black squares), experimental $I_{on}$ (at -2 V; red of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | circles) and |

| simulated $I_{on}$ (at -2 V; blue triangles). Inset: a cross-section schematic diag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ram of five  |

| cells defined by the Au (yellow) top electrodes of 500x500, 400x400, 300x30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0, 200x200   |

| and $100x100 \mu m^2$ , as deposited on a $Li_xCoO_2$ thin film (blue) grown on a Si (gr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

| $SiO_2$ (black) substrate. The x and y dimensions are not to scale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 69           |

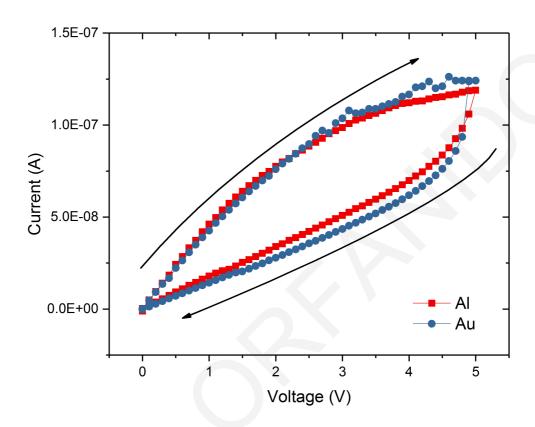

| Figure 4.17 Positive voltage sweeps of a Al/Li <sub>x</sub> CoO <sub>2</sub> /SiO <sub>2</sub> /Si (red square                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | res) and a   |

| Au/Li <sub>x</sub> CoO <sub>2</sub> /SiO <sub>2</sub> /Si (blue circles) memory cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 71           |

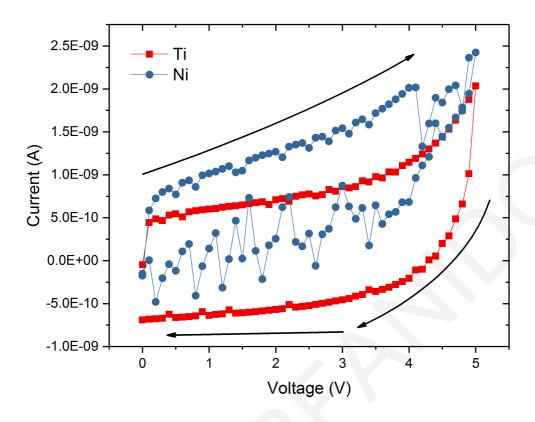

| Figure 4.18 Positive voltage sweeps of a Ti/Li <sub>x</sub> CoO <sub>2</sub> /SiO <sub>2</sub> /Si (red square                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | es) and a    |

| Ni/Li <sub>x</sub> CoO <sub>2</sub> /SiO <sub>2</sub> /Si (blue circles) memory cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 72           |

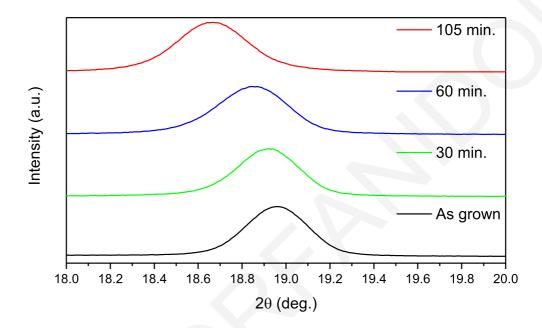

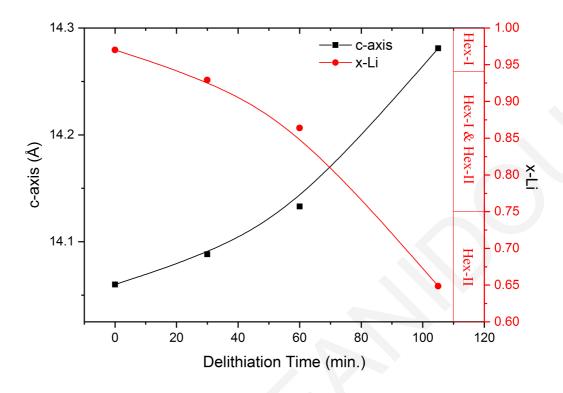

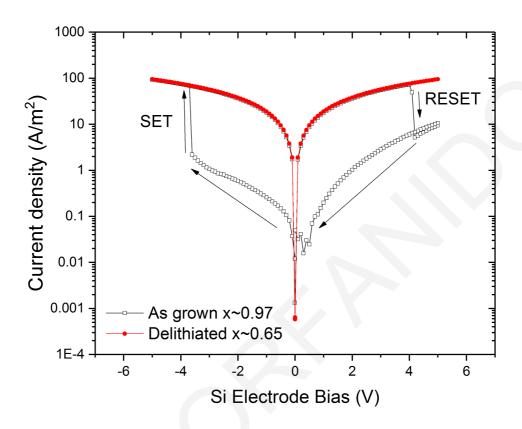

| Figure 4.19 GIXRD patterns showing the shift of the (003) Li <sub>x</sub> CoO <sub>2</sub> peak aft                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | er repeatea  |

| delithiation steps, indicating a reduction of the Li content (incidence angle is 1°                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | )73          |